引言

两年前,我写过一个简单的除法器,当时由于时间问题,只实现了一个简单的逻辑电路,但是实际中大多都是时序的,所以后面给出了修改意见,但是并没有进行进一步的测试,最近发现那个简单的除法器引起了很多讨论,本小节就做一个终结。

1,RTL编码

a,div_rill.v

/*

* module:div_rill

* file name:div_rill.v

* syn:yes

* author:rill

* date:2014-04-10

*/

module div_rill

(

input clk,

input rst,

input enable,

input [31:0] a,

input [31:0] b,

output reg [31:0] yshang,

output reg [31:0] yyushu,

output reg done

);

reg[31:0] tempa;

reg[31:0] tempb;

reg[63:0] temp_a;

reg[63:0] temp_b;

reg [5:0] status;

parameter s_idle = 6'b000000;

parameter s_init = 6'b000001;

parameter s_calc1 = 6'b000010;

parameter s_calc2 = 6'b000100;

parameter s_done = 6'b001000;

reg [31:0] i;

always @(posedge clk)

begin

if(rst)

begin

i <= 32'h0;

tempa <= 32'h1;

tempb <= 32'h1;

yshang <= 32'h1;

yyushu <= 32'h1;

done <= 1'b0;

status <= s_idle;

end

else

begin

case (status)

s_idle:

begin

if(enable)

begin

tempa <= a;

tempb <= b;

status <= s_init;

end

else

begin

i <= 32'h0;

tempa <= 32'h1;

tempb <= 32'h1;

yshang <= 32'h1;

yyushu <= 32'h1;

done <= 1'b0;

status <= s_idle;

end

end

s_init:

begin

temp_a = {32'h00000000,tempa};

temp_b = {tempb,32'h00000000};

status <= s_calc1;

end

s_calc1:

begin

if(i < 32)

begin

temp_a = {temp_a[62:0],1'b0};

status <= s_calc2;

end

else

begin

status <= s_done;

end

end

s_calc2:

begin

if(temp_a[63:32] >= tempb)

begin

temp_a = temp_a - temp_b + 1'b1;

end

else

begin

temp_a = temp_a;

end

i <= i + 1'b1;

status <= s_calc1;

end

s_done:

begin

yshang <= temp_a[31:0];

yyushu <= temp_a[63:32];

done <= 1'b1;

status <= s_idle;

end

default:

begin

status <= s_idle;

end

endcase

end

end

endmodule

/*************** EOF ******************/b,div_rill_tb.v

/*

* module:div_rill_tb

* file name:div_rill_tb.v

* syn:no

* author:rill

* date:2014-04-10

*/

`timescale 1ns/1ns

module div_rill_tb;

reg clk;

reg rst;

reg enable;

reg [31:0] a;

reg [31:0] b;

wire [31:0] yshang;

wire [31:0] yyushu;

wire done;

initial

begin

clk = 0;

#10

rst = 1;

#20

rst = 0;

#15

enable =1;

a = 2;//$random()%10000;

b = 7;//$random()%1000;

#10

enable =0;

#1000

enable =1;

a = 7;//$random()%1000;

b = 2;//$random()%100;

#10

enable =0;

#1000

enable =1;

a = 7;//$random()%100;

b = 7;//$random()%10;

#10

enable =0;

#1000 $stop;

end

always # 5 clk = ~clk;

div_rill DIV_RILL

(

.clk (clk),

.rst (rst),

.enable (enable),

.a (a),

.b (b),

.yshang (yshang),

.yyushu (yyushu),

.done (done)

);

endmodule

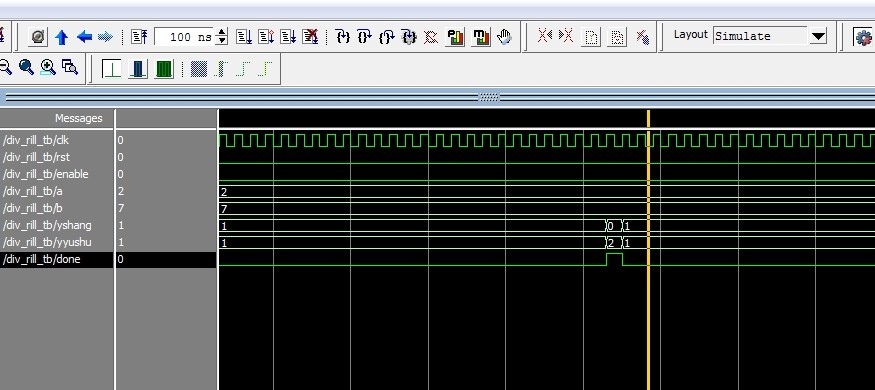

/******** EOF ******************/2,,验证结果

最后

以上就是陶醉裙子最近收集整理的关于数字集成电路设计-9-除法器的verilog简单实现(续2)引言1,RTL编码2,,验证结果的全部内容,更多相关数字集成电路设计-9-除法器内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复