根据逻辑功能的不同特点,可以将数字电路分成两大类:

- 组合逻辑电路

- 时序逻辑电路。

一、组合电路

概念:在组合逻辑电路中,任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。这就是组合逻辑电路在逻辑功能上的共同特点。

特点:从组合电路逻辑功能的特点不难想到,既然它的输出与电路的历史状态无关,那么电路中就不能包含有存储单元。

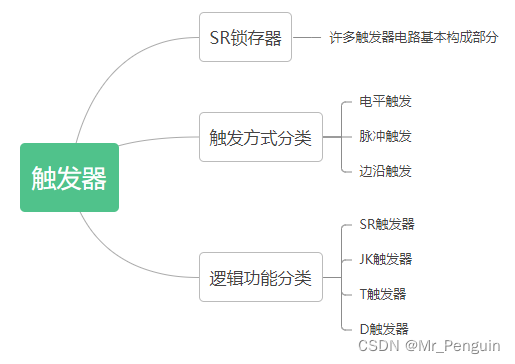

二、触发器(Flip-Flop)

在各种复杂的数字电路中,不但需要对二值信号进行算数运算和逻辑运算,还经常需要将这些信号和运算结果保存起来。为此,需要使用具有记忆功能的基本逻辑单元。能够存储1位的二进制数码的单元电路称为触发器,即触发器是具有记忆功能的基本逻辑单元。 为了实现记忆1位二值信号的功能,触发器必须具备以下两个基本特点:

- 具有两个能自行保持的稳定状态,用来表示逻辑状态的0和1,或二进制数的0和1。

- 在触发信号的操作下,根据不同的输入信号可以置成1或0状态。

SR锁存器(Set-Reset Latch):它是各种触发器电路的基本构成部分。虽然它也有能够自行保持保持的稳定状态,并且可以根据输入信号置成1或0状态,但由于它的置1或置0操作是由输入的置1或置0信号直接完成,不需要触发信号(用于改变电路状态的信号称为“触发信号”)的触发,所以没有将它归入下一节的触发器中。

三、时序电路

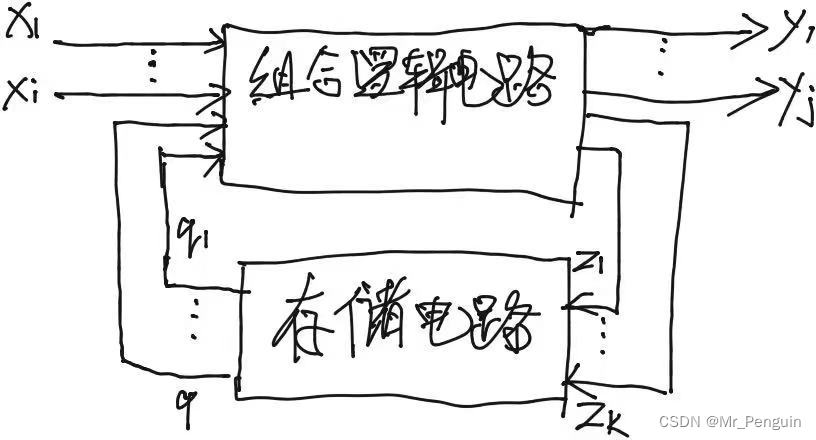

概念:时序电路任一时刻的输出信号不仅取决于当时的输入信号,而且还取决于电路原来的状态,或者说,还与以前的输入有关。具有这种逻辑功能特点的电路称为时序电路。时序电路在电路结构上有两个显著的特点:

- 时序电路中通常包含组合电路和存储电路两个组成部分,而存储电路是必不可少的;

- 存储电路的输出状态必须反馈到组合电路的输入端,与输入信号一起,共同决定组合逻辑电路的输出;

综上,时序逻辑电路的结构框图如下:

由于存储电路中触发器的动作特点不同,时序电路中又有同步时序电路、异步时序电路:

- 同步时序电路中,所有触发器状态的变化都是在同一时钟信号操作下同时发生的;

- 异步时序电路中,触发器状态的变化不是同时发生的;

四、寄存器

寄存器:Register,用于寄存一组二值代码,它被广泛地用于各类数字系统和数字计算机中。因为一个触发器能存储1位二值代码,所以用N个触发器组成的寄存器能存储一组N位的二值代码。

对寄存器中的触发器只要求它们具有置1、置0的功能即可,因为无论是用电平触发、脉冲触发、边沿触发的触发器,都可以组成寄存器。

最后

以上就是年轻蜗牛最近收集整理的关于组合电路、触发器、时序电路、寄存器一、组合电路二、触发器(Flip-Flop)三、时序电路四、寄存器的全部内容,更多相关组合电路、触发器、时序电路、寄存器一、组合电路二、触发器(Flip-Flop)三、时序电路四、寄存器内容请搜索靠谱客的其他文章。

发表评论 取消回复