文章目录

- 一、计数器及应用

- (1)实验目的

- (2)实验原理或设计过程

- (3)实验电路图

- 分频比为5的整数分频电路

- 输出序列码10101

- (4)分频比为5的整数分频电路RTL代码设计(加分项)

- (5)输出序列码10101RTL代码设计(加分项)

- (6)实验数据分析和实验结果

- 二、移位寄存器及应用

- (1)实验目的

- (2)实验原理或设计过程

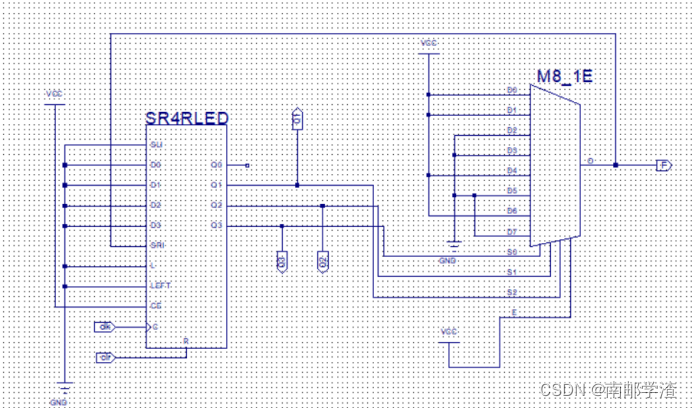

- (3)实验电路图

- (4)实验数据分析和实验结果

一、计数器及应用

(1)实验目的

1、掌握计数器的逻辑功能及应用方法

2、掌握任意进制计数器的设计方法

3、掌握数字电路多个输出波形相位关系的正确测试方法

4、了解非均匀周期信号波形的测试方法

(2)实验原理或设计过程

- 设计一个分频比N=5的整数分频电路,观察并记录时钟脉冲和输出波形。

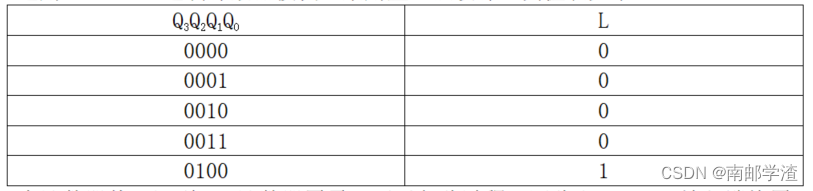

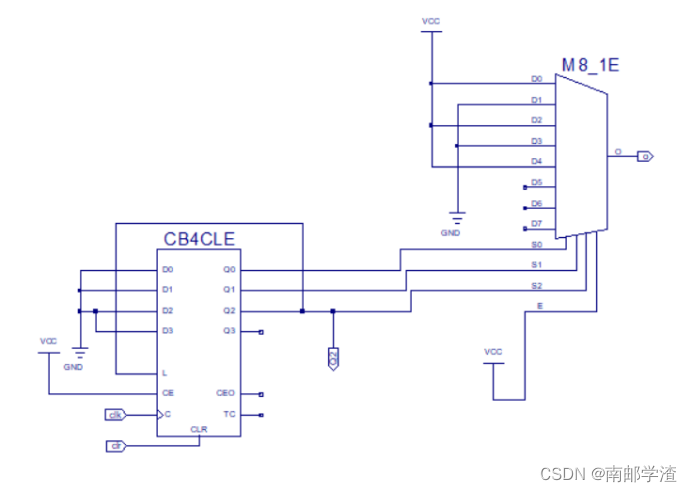

选用cb4cle二进制计数器模块,采用置0法设计,真值表如下。

当计数器从0记到4,计数器置零,再反复此过程,因此取Q2=L,D输入端均置零。 - 设计一个10101序列信号发生器,观察并记录时钟脉冲和输出波形。

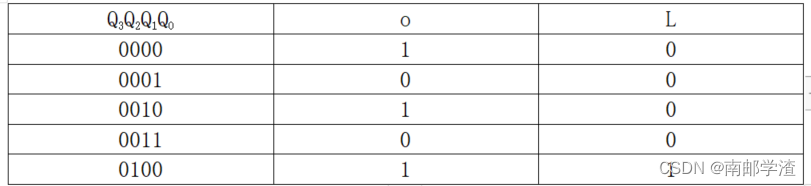

选用cb4cle和八选一数据选择器,采用置0法设计,真值表如下。

当计数器从0记到4,计数器置零,再反复此过程,因此取Q2=L,D输入端均置零。当计数器从0记到4,数据选择器输出10101,实现目的。

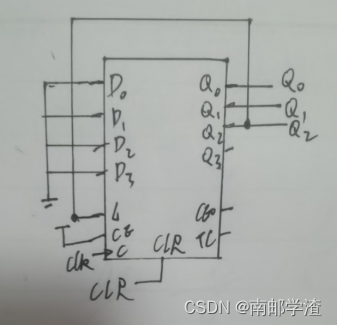

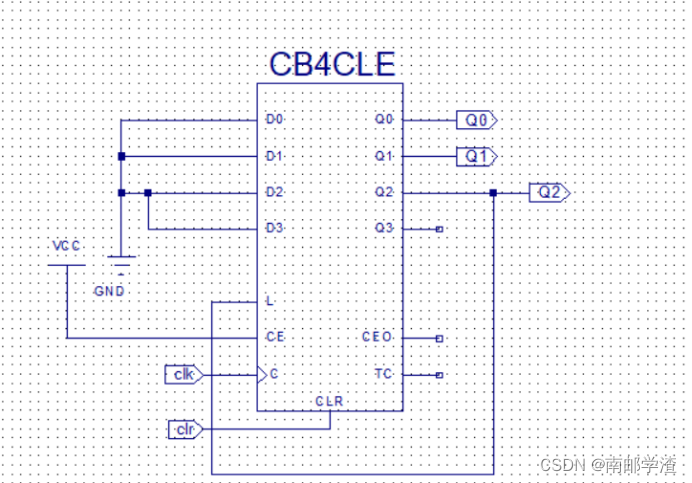

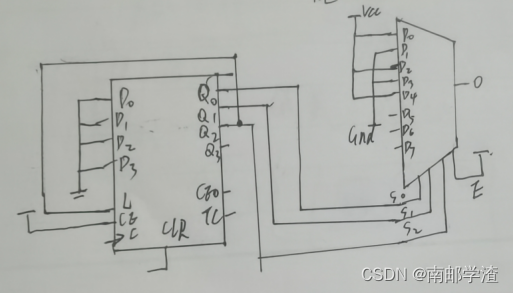

(3)实验电路图

分频比为5的整数分频电路

输出序列码10101

(4)分频比为5的整数分频电路RTL代码设计(加分项)

- RTL代码

module counter_5(

input wire clk,

input wire rst_n,

output reg counter

);

reg [2:0]cnt;

always @(posedge clk or negedge rst_n)

if(!rst_n)

cnt <= 1'b0;

else if(cnt == 3'd4)

cnt <= 1'b0;

else

cnt <= cnt +1'b1;

always @(posedge clk or negedge rst_n)

if(!rst_n)

counter <= 1'b0;

else if(cnt == 3'd3)

counter <= 1'b1;

else

counter <= 1'b0;

endmodule

- 仿真测试模块代码

`timescale 1ns/1ns

`define clk_period 20

module counter_5_tb;

reg clk;

reg rst_n;

wire counter;

counter_5 counter_5_inst(

.clk(clk),

.rst_n(rst_n),

.counter(counter)

);

initial clk = 1'b0;

always #(`clk_period/2) clk = ~clk;

initial begin

rst_n = 1'b0;

#(`clk_period*10);

rst_n = 1'b1;

#(`clk_period*500);

$stop;

end

endmodule

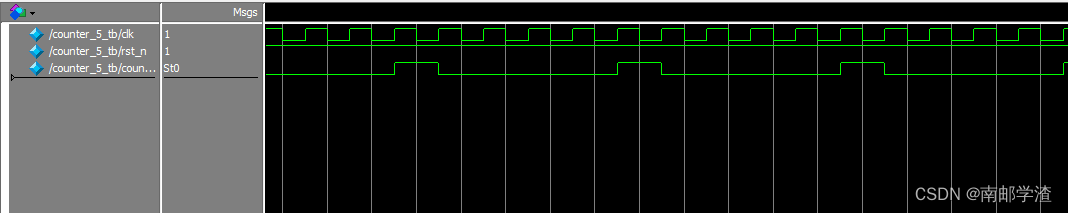

- 仿真波形图

(5)输出序列码10101RTL代码设计(加分项)

- RTL代码

module sequence(

input wire clk,

input wire rst_n,

output reg seq

);

reg [2:0]cnt;

always @(posedge clk or negedge rst_n)

if(!rst_n)

cnt <= 1'b0;

else if(cnt == 3'd4)

cnt <= 1'b0;

else

cnt <= cnt + 1'b1;

always @(*)

case(cnt)

3'b000 : seq = 1'b1;

3'b001 : seq = 1'b0;

3'b010 : seq = 1'b1;

3'b011 : seq = 1'b0;

3'b100 : seq = 1'b1;

endcase

endmodule

- 仿真测试模块代码

`timescale 1ns/1ns

`define clk_period 20

module sequence_tb;

reg clk;

reg rst_n;

wire seq;

sequence sequence_inst(

.clk(clk),

.rst_n(rst_n),

.seq(seq)

);

initial clk = 1'b0;

always #(`clk_period/2) clk = ~clk;

initial begin

rst_n = 1'b0;

#(`clk_period*10);

rst_n = 1'b1;

#(`clk_period*100);

$stop;

end

endmodule

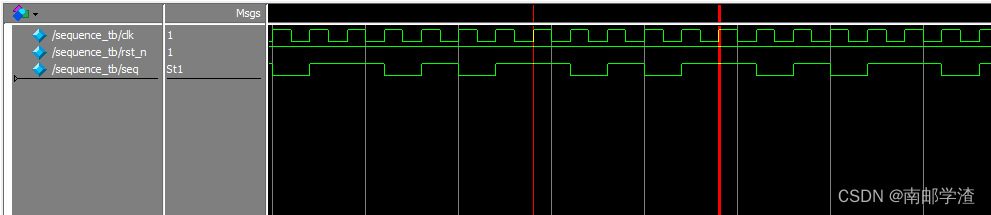

- 仿真波形图

(6)实验数据分析和实验结果

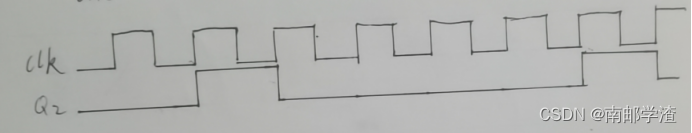

1、分频比为N=5的整数分频电路波形图。

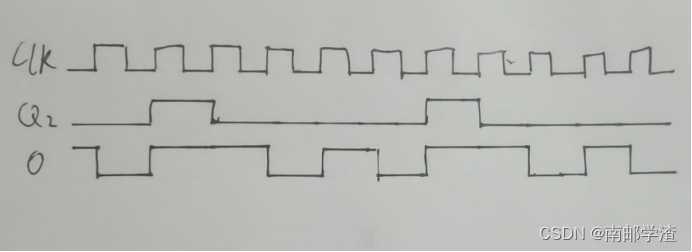

2、输出序列码10101波形图:

二、移位寄存器及应用

(1)实验目的

1、掌握移位寄存器的逻辑功能

2、掌握移位寄存器的具体应用方法

3、掌握移位寄存型计数器的自启动特性的检测方法

4、掌握不均匀周期信号波形的测试方法

(2)实验原理或设计过程

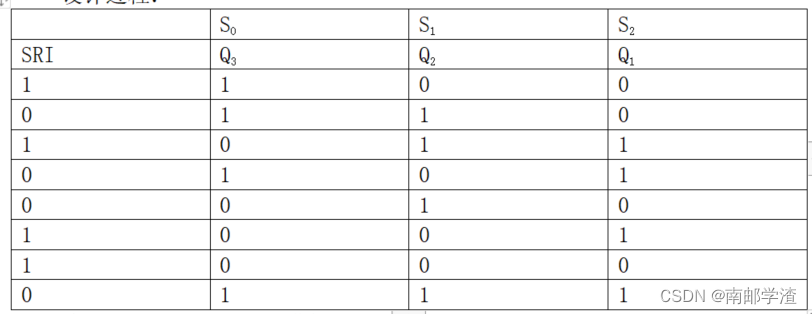

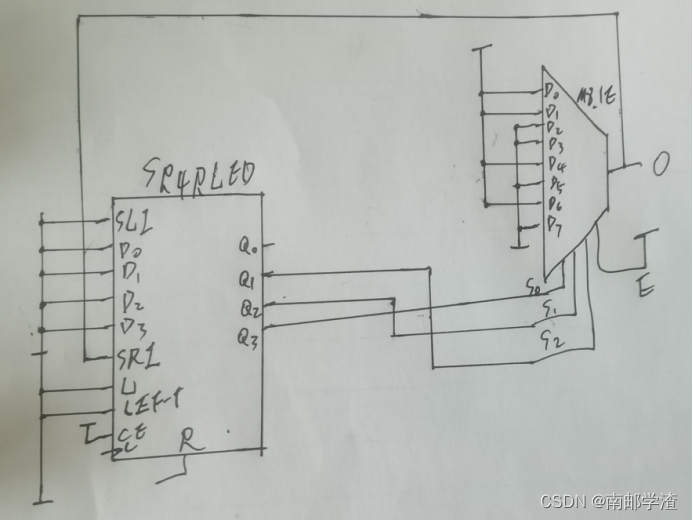

用移位寄存器附加数据选择器电路设计101001序列信号发生器,要求具有自启动特性,用实验验证。用示波器双踪观察并记录时钟脉冲和输出波形。

设计过程:

选用SR4RLED和M8_1E进行设计

(3)实验电路图

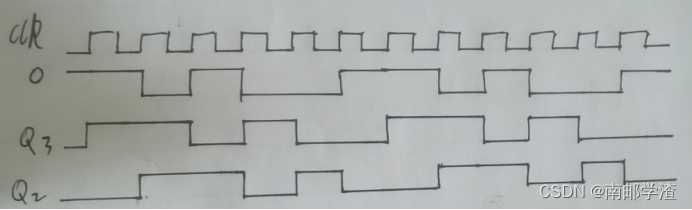

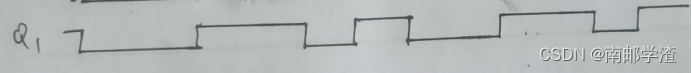

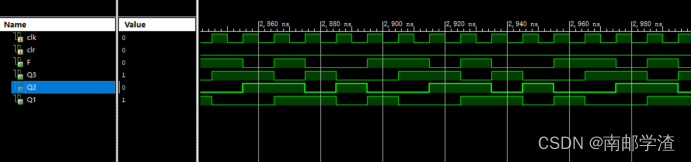

(4)实验数据分析和实验结果

最后

以上就是能干蜜蜂最近收集整理的关于南京邮电大学电工电子(数电)实验报告——计数器 & 移位寄存器一、计数器及应用二、移位寄存器及应用的全部内容,更多相关南京邮电大学电工电子(数电)实验报告——计数器内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复