我前段时间对这两个逻辑的概念有点混淆,所以就百度查看了一下,排名第一的结果就出现了这样的解释:

数字电路根据逻辑功能的不同特点,可以分成两大类,一类叫组合逻辑电路(简称组合电路),另一类叫做时序逻辑电路(简称时序电路)。组合逻辑电路在逻辑功能上的特点是任意时刻的输出仅仅取决于该时刻的输入,与电路原来的状态无关。而时序逻辑电路在逻辑功能上的特点是任意时刻的输出不仅取决于当时的输入信号,而且还取决于电路原来的状态,或者说,还与以前的输入有关

额…,怎么说呢还是没太看懂,什么叫还与以前的输入有关呢?又是怎么一个关系呢?

那么咱们还是说的再具体一点

这里我参考了 知乎 大道至简 提出的三个区别,分别是

关于组合逻辑和时序逻辑的不同,我们可以从三方面来理解,分别是code(代码),电路图和波形图三方面。

从代码层面来看,时序逻辑即敏感列表里面带有时钟上升沿,如果是没有上升沿或者是带有“*”号的代码,为组合逻辑。

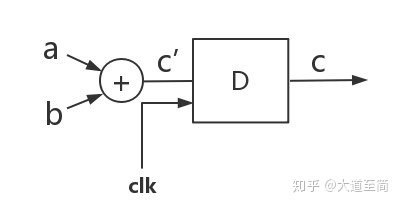

电路层面,两种逻辑反映的电路也有不同,时序逻辑相当于在组合逻辑的基础上多了一个D触发器。

波形图层面,组合逻辑的波形是即刻反映变化的,与时钟无关;但是时序逻辑的波形不会立刻反映出来,只有在时钟的上升沿发生变化。

举个例子吧,计算c=a+b

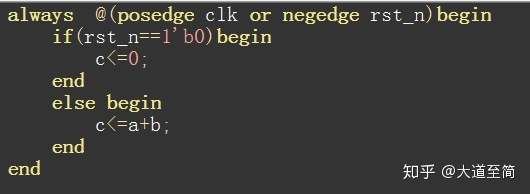

在代码层面,时序逻辑代码表示如下,可以看到此代码有“posedge“时钟上升沿,即表示有一个D触发器,a+b的结果c是在D触发器发出指令后才进行输出的。

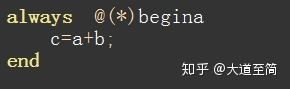

组合逻辑则如下所示,是不带上升沿的,有“*”号的,直接输出a+b=c的值,不进行额外操作,也是组合逻辑:

对比两种逻辑的代码表示,可以看出同样是输出c的值,不同的逻辑输出时间却不同,时序逻辑是在时钟上升沿输出,组合逻辑则直接输出。

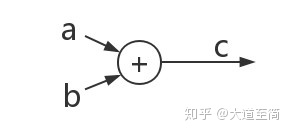

这是组合逻辑,直接输出a+b=c

时序逻辑的电路图加法器连接的a和b没有变,但是c的值在输出部分,不会直接输出,D触发器就像一扇门,信号值c‘停留在门前,当D触发器收到了时钟clk上升沿的信号,才会把门打开,输出信号c的值,如下图所示:

这里也可以简单的理解为,看输出是否受时钟的上升沿控制,在时钟的上升沿之后再进行运算,时钟上升沿之后计算的c的值为上一时刻的a+b(故也有时序电路常会延迟一拍的说法),这里我放上时序图大家看看

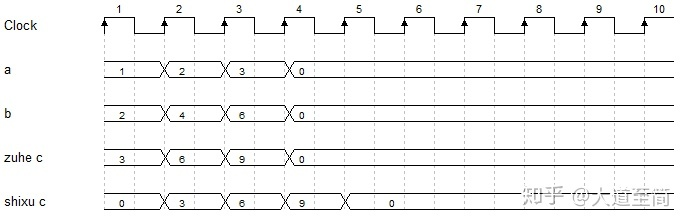

在波形图层面,我们可以画出时序图来分析,如下图所示。可以看出第一个时钟时a=1,b=2,此时组合逻辑立刻得出c=3,是跟时钟没有关系的;但是时序逻辑一定要在下一个时钟的上升沿处才得出c=3的结果;

以此类推,后面的原理是一样的,当a=2,b=4时,组合逻辑马上得出c=6,时序逻辑在第3个时钟上升沿得出c=6。

也可简单理解为时序电路常会延迟一个时钟周期

怎么样,大家学费了吗。

最后

以上就是沉静短靴最近收集整理的关于组合逻辑与时序逻辑的全部内容,更多相关组合逻辑与时序逻辑内容请搜索靠谱客的其他文章。

发表评论 取消回复