1、写模块count.v和测试文件tcount.v代码:

module count(out,data,load,reset,clk);

output[7:0] out;

input[7:0] data;

input load,clk,reset;

reg[7:0] out;

always @(posedge clk)

begin

if(!reset)

out=8'h00;

else if(load) out=data;

else

out=out+1;

end

endmodule

//测试文件tcount.v

`timescale 1ns/1ns

module tcount;

wire[7:0] out;

reg[7:0] data;

reg load,clk,reset;

initial

begin

clk = 0;

#10 forever #10 clk = !clk;

end

initial

begin

reset=1; load=1; data = 8'h01;

#40 data = 8'h4;

#40

data = 8'h20;

#40

data = 8'h80;

#40 load=0;

#160 reset=0;

end

//exemplify

count v1_count(

.out (out),

.data (data),

.load (load),

.reset (reset),

.clk (clk)

);

endmodule

代码分析:

开始设置rst为1,load为1,clk在第10s开始出现上升沿,前160ns为同步置数功能,out输出值就是data的数据。在第160ns时刻当load为0时,开始计数功能,在原来的值加1。在第320ns时刻reset设置为0,执行复位操作,所以输出为0。

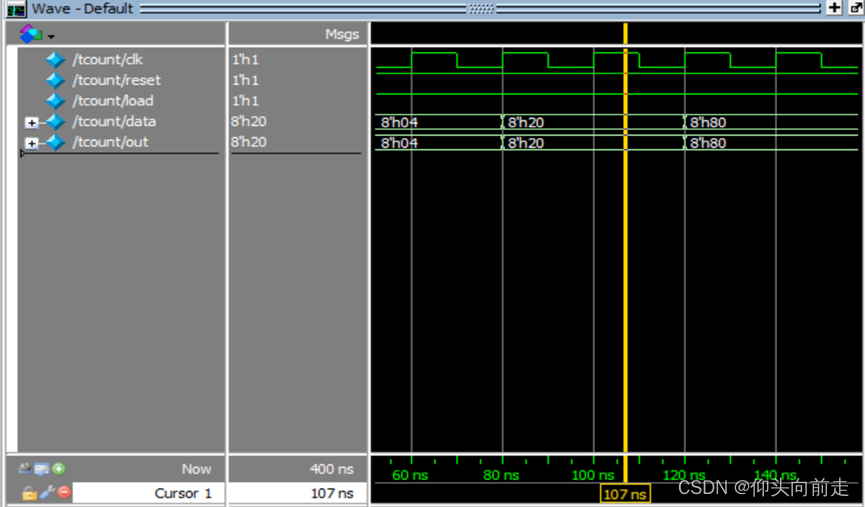

2、仿真结果分析:

3、结果分析:

仿真波形中从上到下分别是clk、reset、load、data和out。reset为1且load为1的时候,为置数功能,输出out的值就为data的值,当reset为1且load为0时候,为计数功能,每来一个上升沿,计数值加1,当reset为0时输出out为0,仿真结果和预期实现的完全一致,实验正确。

最后

以上就是细腻果汁最近收集整理的关于verilog计数器count.v和测试台文件,同步置数、同步清零,计数功能,仿真波形及分析的全部内容,更多相关verilog计数器count内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复