本章目录:

- 1. 锁存器/触发器

- 1.1 概念

- 1.2 性质

- 1.3 分类

- 1.4 二者区别

- 1.5 为什么锁存器不好?

- 1.6 小问题,大智慧

- 2. 寄存器

- 3. 基本SR锁存器

- 3.1 符号表示的意义

- 3.2 由与非门构成的

- 3.3 由或非门构成的

- 4 门控SR锁存器

- 4.1 电平触发

- 4.1.1 带异步清零和异步置位的门控SR锁存器

- 4.2 动作特点

- 4.3 空翻问题的出现

- 4.3.1 面试题目

- 4.3.1.1 门控锁存器产生空翻现象的原因是什么?

- 4.3.2 怎么解决这个问题呢?

- 5 主从SR触发器

- 6. 主从JK触发器

- 6.1 逻辑功能描述

- 6.2 带清零端和置位端的主从JK触发器

- 6.3 进一步改进

- 7 边沿触发器——D触发器

- 7.1 符号说明

- 7.2 内部结构

- 8. 边沿触发器——JK触发器(利用传输延迟)

- 9. T触发器

- 10. T’触发器

- 参考文献

- 学习声明

1. 锁存器/触发器

1.1 概念

锁存器(latch) :是电平触发的存储单元, 数据存储的动作只取决于 输入信号 的电平值 ,只有当锁存器处于使能 状态, 输出才会随着 输入发生变化;

触发器(Flip flops 或者FF): 当收到 输入脉冲时,又称为触发。触发器 输出会根据 规则 改变 状态,然后保持这种状态直到 收到 另一个 触发 ;

1.2 性质

(1)具有两个稳定的状态:1状态和0状态。

(2)具有两个输出端:原码输出Q和反码输出 Q ‾。一般用Q的状态表明电路状态。

(3)由一个稳态到另一稳态,必须有外界信号的触发,否则将长期稳定在某个状态。

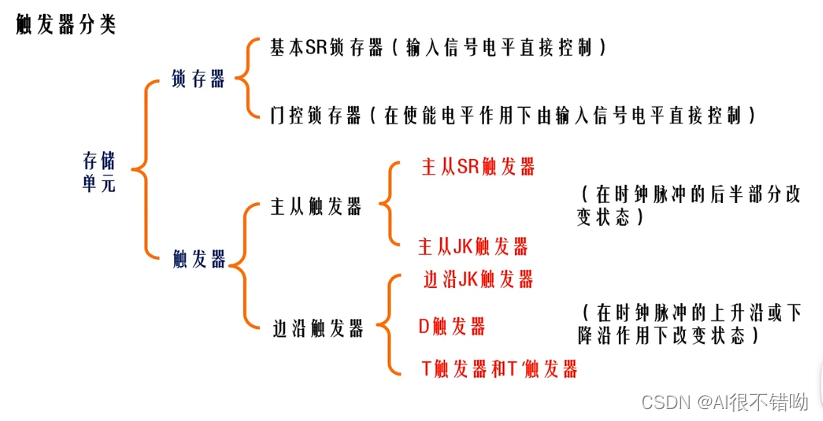

1.3 分类

1.4 二者区别

latch 是电平触发,FF是边沿触发,FF在同一时钟边沿触发下动作,符合同步电路的设计思想,而 latch 则属于异步电路设计,往往会导致时序分析困难,不适当的应用 latch则会大量浪费芯片资源。

一般将信号经过两级触发器就可以消除毛刺。

1.5 为什么锁存器不好?

- 锁存器对毛刺不敏感,很容易在信号上产生毛刺;

- 而且也没有时钟信号,不容易进行静态时序分析。

正是因为这两个原因,我们在 FPGA 设计时,尽量不用锁存器。

1.6 小问题,大智慧

“FPGA 中只有 LUT 和 FF 的资源,没有现成的 Latch,所以如果要用 Latch,需要更多的资源来搭出来。”这个观点不完全是正确的。

在 Xilinx 的 FPGA 中,6 系列之前的器件中都有 Latch;6 系列和 7 系列的 FPGA 中,一个Slice 中有 50%的 storage element 可以被配置为 Latch 或者 Flip-Flop,另外一半只能被配置为 Flip-Flop。比如 7 系列 FPGA 中,一个 Slice 中有 8 个 Flip-Flop,如果被配置成了 Latch, 该 Slice 的另外 4 个 Flip-Flop 就不能用了。这样确实造成了资源的浪费。但在在 UltraScale 的 FPGA 中,所有的 storage element 都可以被配置成 Flip-Flop 和 Latch。

2. 寄存器

由多个锁存器或者触发器构成的存储单元。

3. 基本SR锁存器

3.1 符号表示的意义

S:Set,置位

R:Reset,复位

D:Direct,直接控制,表示不受时钟影响(再就是锁存器没有时钟信号)

Q:现态

Q’:次态

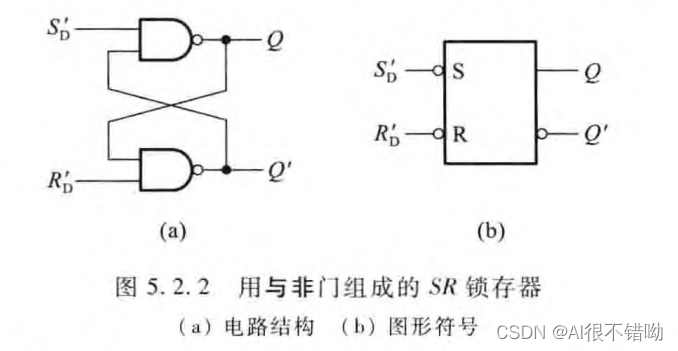

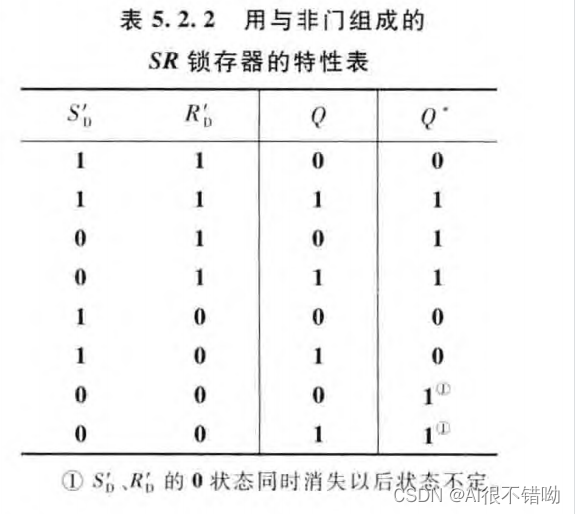

3.2 由与非门构成的

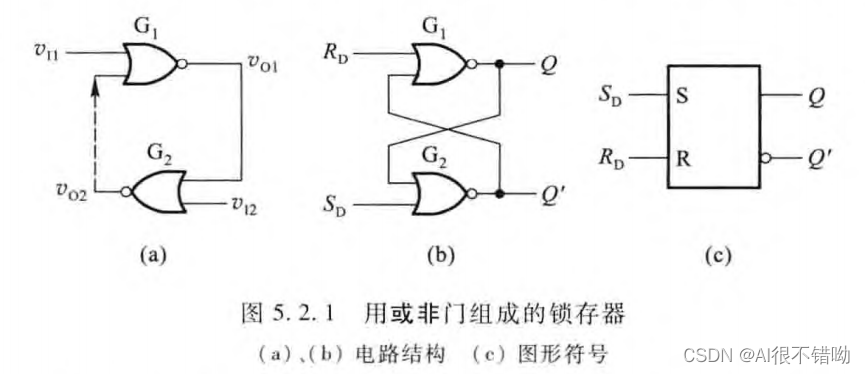

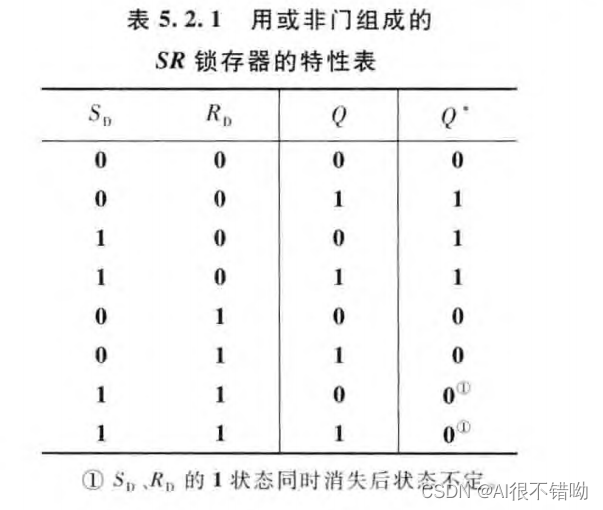

3.3 由或非门构成的

总结:不论是由与非门组成的还是由或非门组成的SR锁存器,记住只要SR两个同时不为 有效电平 (比如与非门组成的,SR不等于00即可),那就是有效状态,S有效R无效,置1;S无效R有效,置0;SR都无效,保持。(注意:我这里说的是有效和无效,可不是确定SR的电平哈!!!)

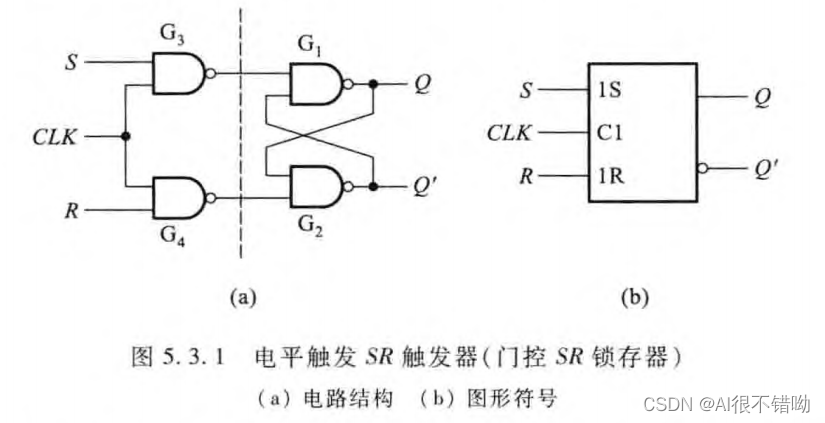

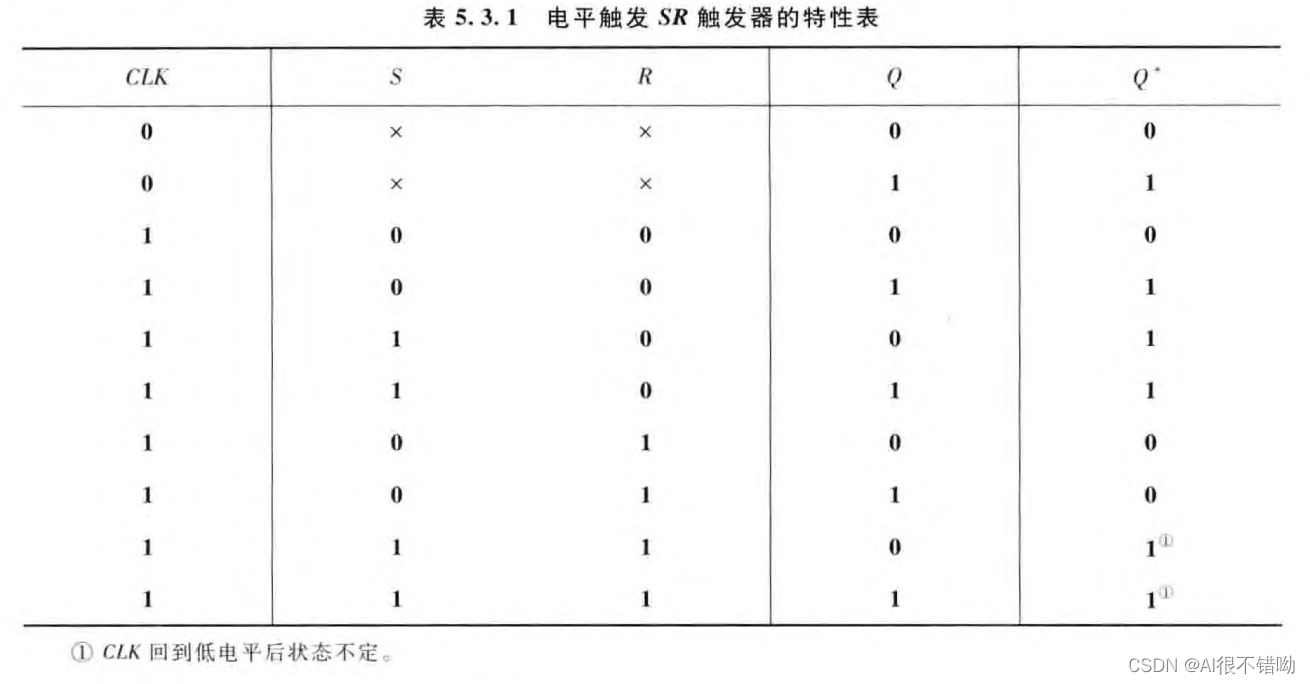

4 门控SR锁存器

4.1 电平触发

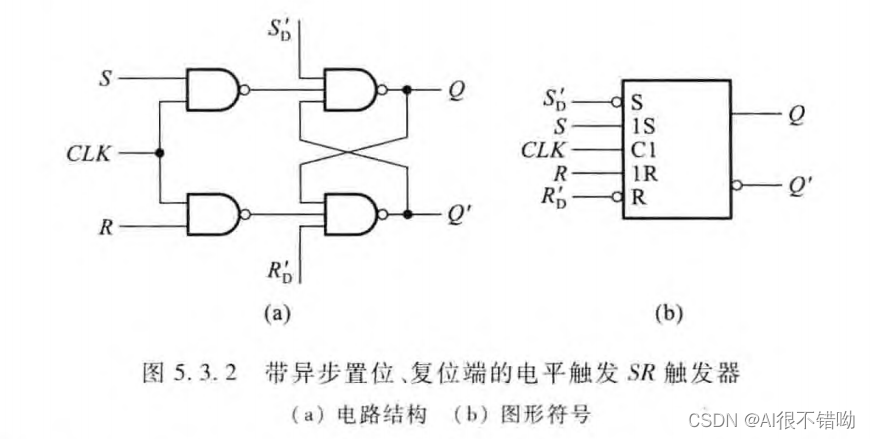

4.1.1 带异步清零和异步置位的门控SR锁存器

分析的时候先看Sd‘和Rd’的信号是否有效,再看S、R、CLK的信号。

分析的时候先看Sd‘和Rd’的信号是否有效,再看S、R、CLK的信号。

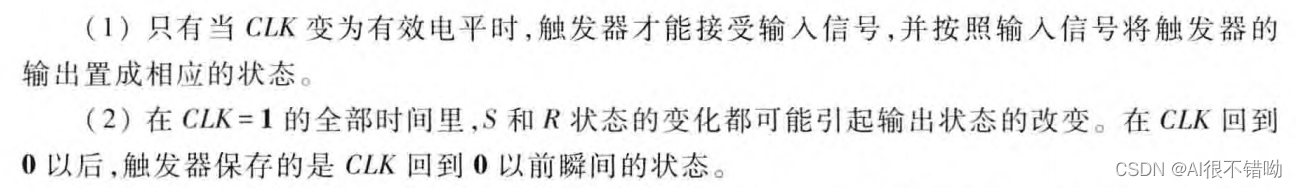

4.2 动作特点

4.3 空翻问题的出现

触发器的一个重要的应用就是 计数器,用来计数CP的个数称为计数器。那“空翻”怎么产生的呢?

因为一些门电路都是有延时的,导致一些电平不能够及时的变化,所以会对输出有一定的影响,这就导致在一个时钟cp期间,出现多次输出翻转的信号,导致时钟的数量记的不对,最后计数器功能出错。

4.3.1 面试题目

4.3.1.1 门控锁存器产生空翻现象的原因是什么?

因为采用了电平触发的方式,导致空翻现象的产生。

4.3.2 怎么解决这个问题呢?

采用 主从触发器

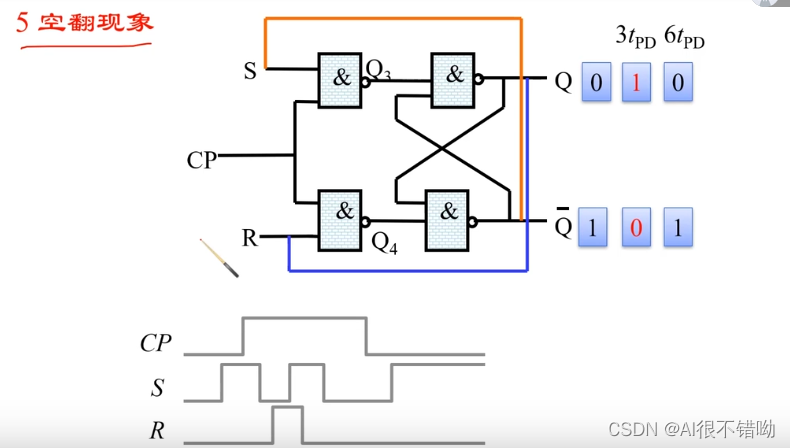

5 主从SR触发器

可想而知,主从是什么意思?简单可以理解成 主人 和 仆人 的关系呗~

左边的控制右边的触发器,对于一个cp内的,主触发器在cp高电平有效,而从触发器在cp低电平有效。左边对信号进行翻转,右边对左边的信号延迟半个周期之后进行搬移,不会出现像门控触发器那样有空翻的现象产生,所以可以用来做计数器。

左边的控制右边的触发器,对于一个cp内的,主触发器在cp高电平有效,而从触发器在cp低电平有效。左边对信号进行翻转,右边对左边的信号延迟半个周期之后进行搬移,不会出现像门控触发器那样有空翻的现象产生,所以可以用来做计数器。

但是,还有个问题,他还是有约束的,SR不能同时有效,这就造成了极大的不便。这就引出了下边的 主从JK触发器。

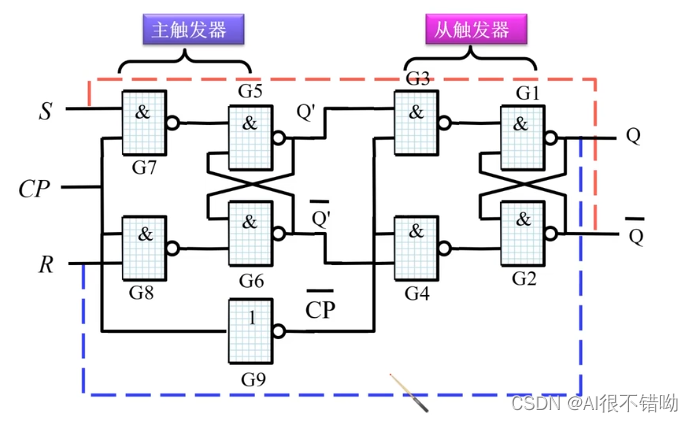

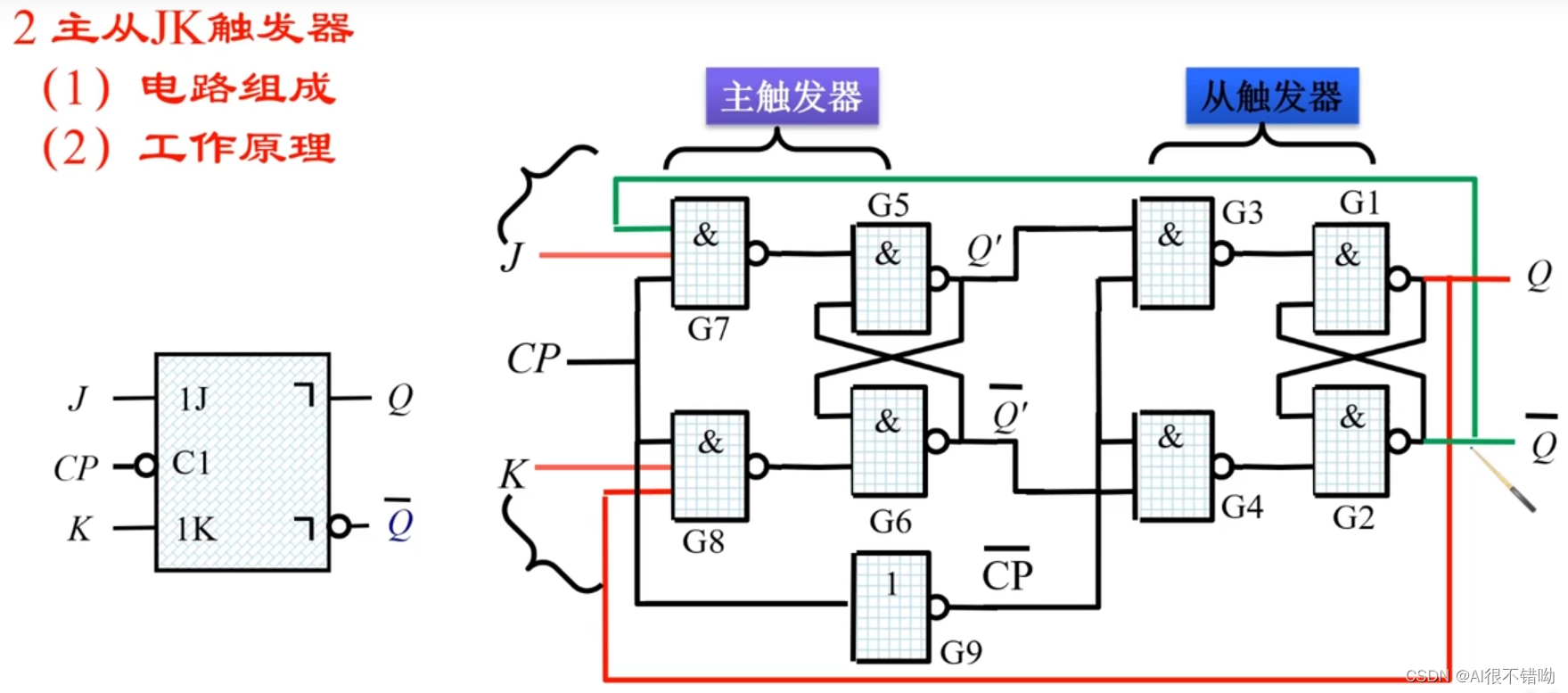

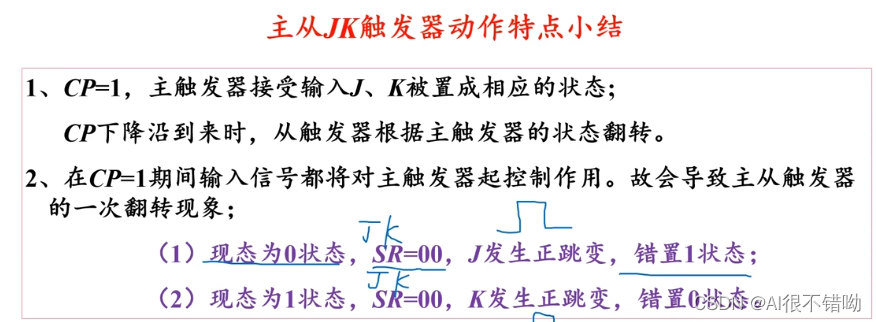

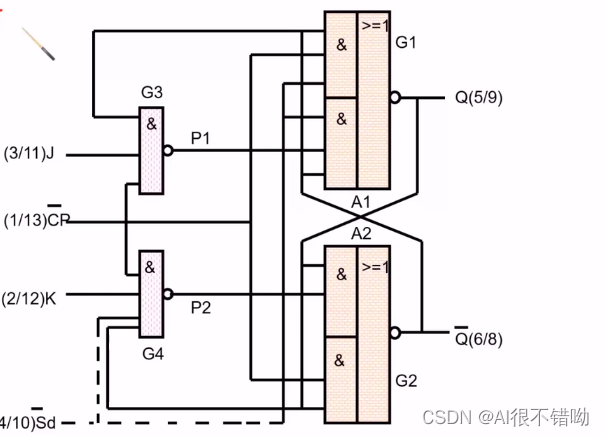

6. 主从JK触发器

这里对 主从SR触发器 做了缺点的进一步改进,不再需要约束条件了,直接将输出信号和输入信号给到与非门,如上图所示。不会再有同时输入两个一的情况发生了。

这里对 主从SR触发器 做了缺点的进一步改进,不再需要约束条件了,直接将输出信号和输入信号给到与非门,如上图所示。不会再有同时输入两个一的情况发生了。

从主从JK触发器 之后,就直接可以先画出Q的波形图,对于Q‘的波形图直接取反就ok。

6.1 逻辑功能描述

JK = 00 ,保持

JK = 01, 置0

JK = 10, 置1

JK = 11, 翻转

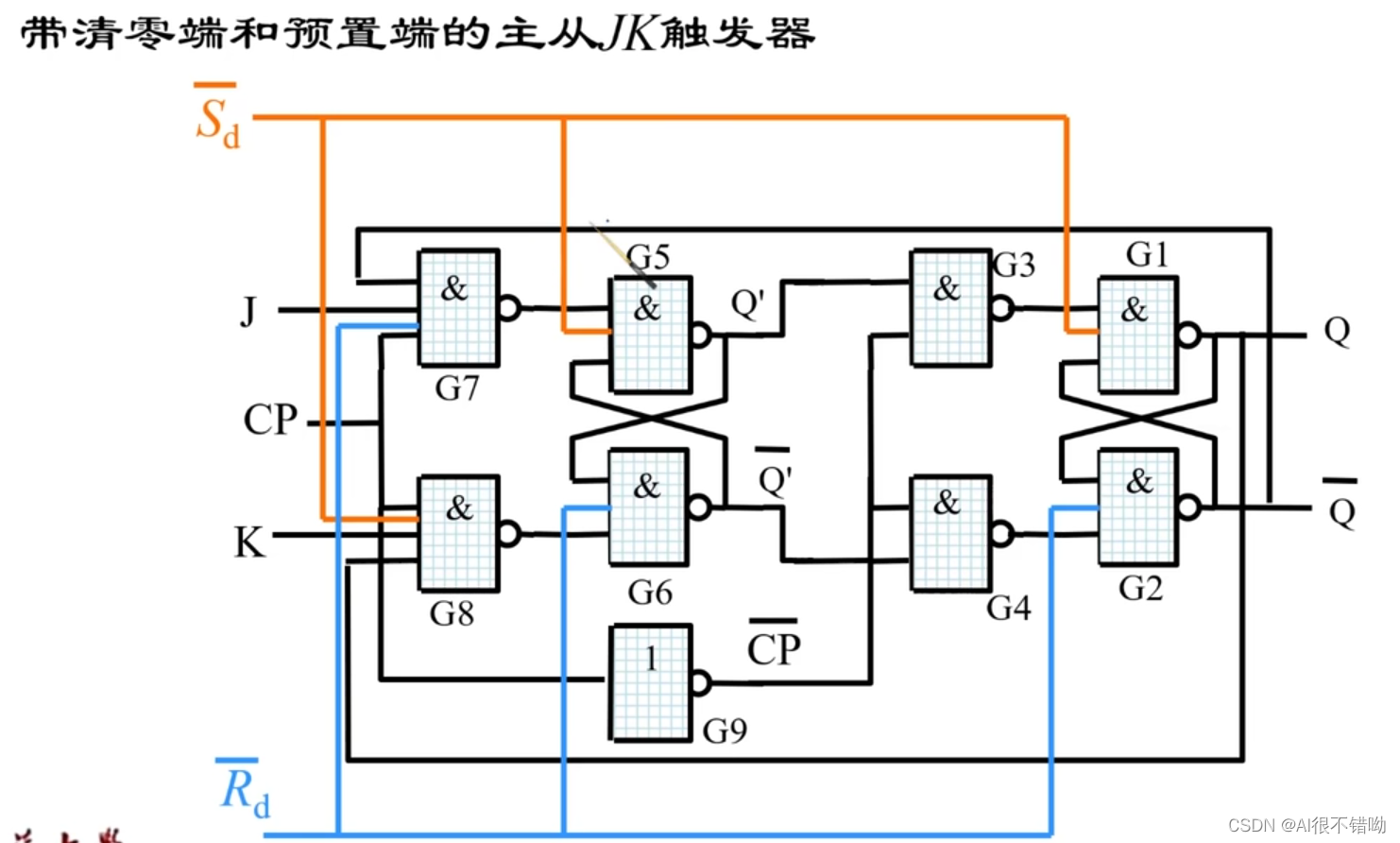

6.2 带清零端和置位端的主从JK触发器

6.3 进一步改进

虽然 主从JK触发器改进了很多,但又有一个新的问题:一次变化!

什么是一次变化???

上边可以知道,输出端只能是一个0一个1,那么对于输入的与非门而言,只能锁住一端,假设另一端受到信号的干扰,那会导致主触发器结果改变,因为只能改变一次,所以等到cp为0时,从触发器只起到搬运作用,搬运的是错误的,导致系统出错。

为了避免发生一次变化,在cp=1的期间,让JK保持不变。

改进: 引入边沿触发器。

改进: 引入边沿触发器。

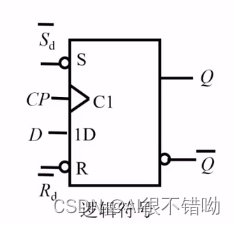

7 边沿触发器——D触发器

7.1 符号说明

同样存在异步清零和异步置一的信号,优先级最高。大家看到cp端口处的三角符号了吗?这个表示的就是边沿触发信号,再就是有 圈圈 表示低电平有效,没有 圈圈 代表高电平有效。

同样存在异步清零和异步置一的信号,优先级最高。大家看到cp端口处的三角符号了吗?这个表示的就是边沿触发信号,再就是有 圈圈 表示低电平有效,没有 圈圈 代表高电平有效。

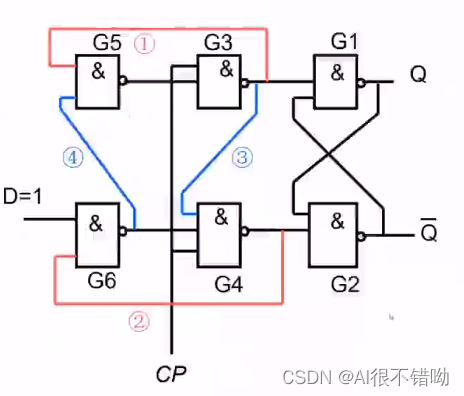

7.2 内部结构

分析:G1和G2是我们前边讲过的基本SR锁存器;G1-G4表示我们前边所说的门控SR锁存器;整个表示的是D触发器。

小结:D触发器实现的是 cp上升沿到来时进行采样,即Q = D。

小结:D触发器实现的是 cp上升沿到来时进行采样,即Q = D。

注意:当时钟上升沿来临时,此时D刚好发生跳变,此时应当采样的是前边的电平信号。

8. 边沿触发器——JK触发器(利用传输延迟)

这个和我们上边学的主从JK触发器不同的点在于,这个是用边沿触发的,只有当有效边沿(上升或下降需要看具体电路)来临时,才遵循变化规则,否则,一直保持。

这个和我们上边学的主从JK触发器不同的点在于,这个是用边沿触发的,只有当有效边沿(上升或下降需要看具体电路)来临时,才遵循变化规则,否则,一直保持。

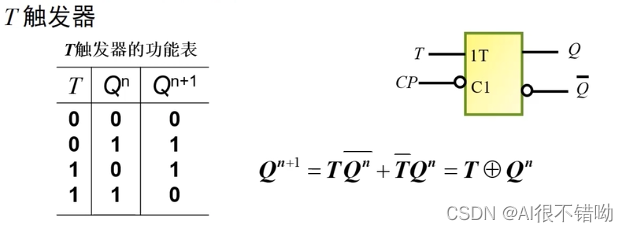

9. T触发器

说明:当有效沿信号到来时,T为0,保持原来状态;T为1时,进行翻转。

说明:当有效沿信号到来时,T为0,保持原来状态;T为1时,进行翻转。

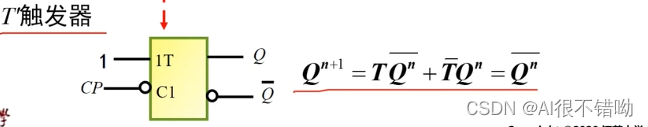

10. T’触发器

说明:T‘触发器只是实现了T触发器的部分功能,只有翻转。

说明:T‘触发器只是实现了T触发器的部分功能,只有翻转。

参考文献

视频1

视频2

博客1

课本:数电基础(如果有同学想要电子版书籍也可以私信我)

学习声明

仅用做学习,不可商业!如有侵权,告知立删。

最后

以上就是奋斗招牌最近收集整理的关于【基础知识】~ 锁存器/触发器、寄存器1. 锁存器/触发器2. 寄存器3. 基本SR锁存器4 门控SR锁存器5 主从SR触发器6. 主从JK触发器7 边沿触发器——D触发器8. 边沿触发器——JK触发器(利用传输延迟)9. T触发器10. T’触发器参考文献学习声明的全部内容,更多相关【基础知识】~内容请搜索靠谱客的其他文章。

![CountDownLatch倒计数锁存器(Latch:门闩[shuan])](https://www.shuijiaxian.com/files_image/reation/bcimg22.png)

发表评论 取消回复