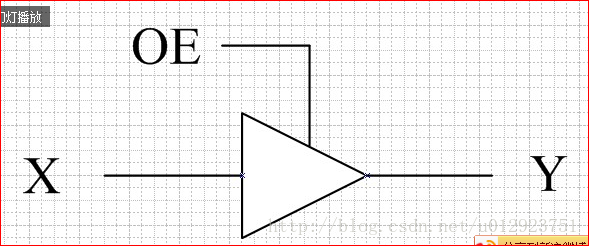

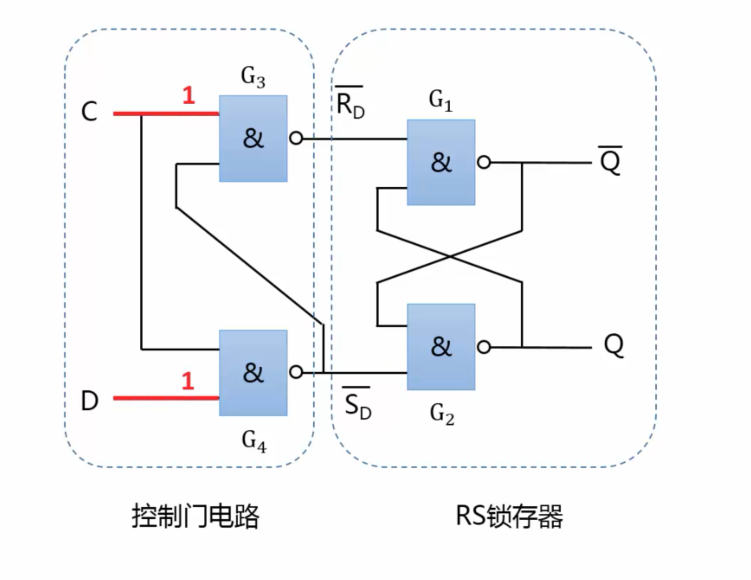

锁存器:具有记忆功能,仅仅在高低电平可以对输入信号敏感改变状态

Q(n+1)=D

分析

C=0,因此Rd非和Sd非均为1,此时不影响输出结果(因为实际决定Q(n+1)还是原来的Q)所以保持不变

C=1,如果D=0则迅速把结果传递到Rd非=0和Sd非=1,由于有0,Q非直接为1,Q为0

反过来D=1一样分析

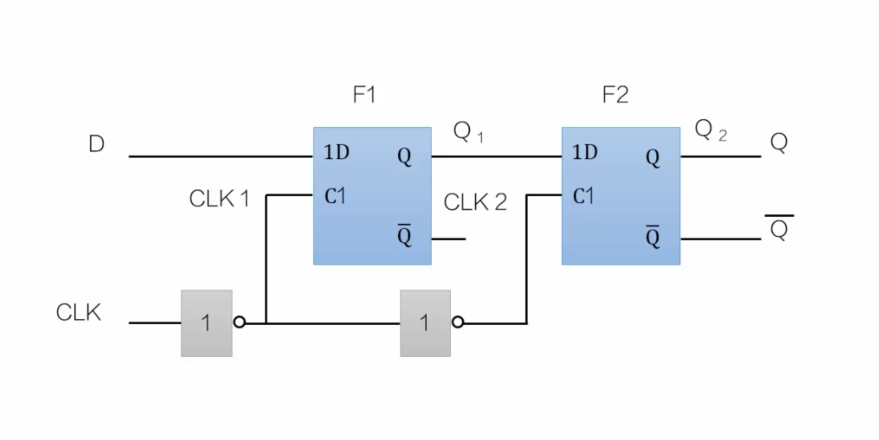

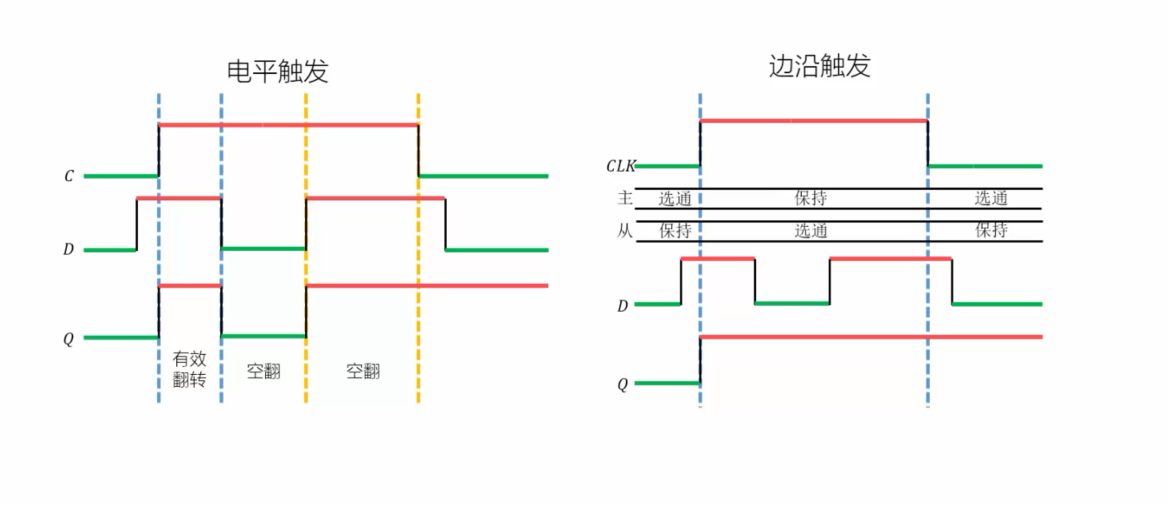

触发器:仅仅在上升沿下降沿那个瞬间才会改变状态

两个锁存器相连的结构,分析如下

首先可知,CLK在高电平时才具有检测能力,因此把CLK1和2通过反相器错开,使得CLK1在CLK=0时间有效,数据传递进入Q1,然后等CLK=1,CLK2才会有效,把数据从Q1传递到Q2,就可以使得其在那个沿的瞬间进行改变了(上边沿)

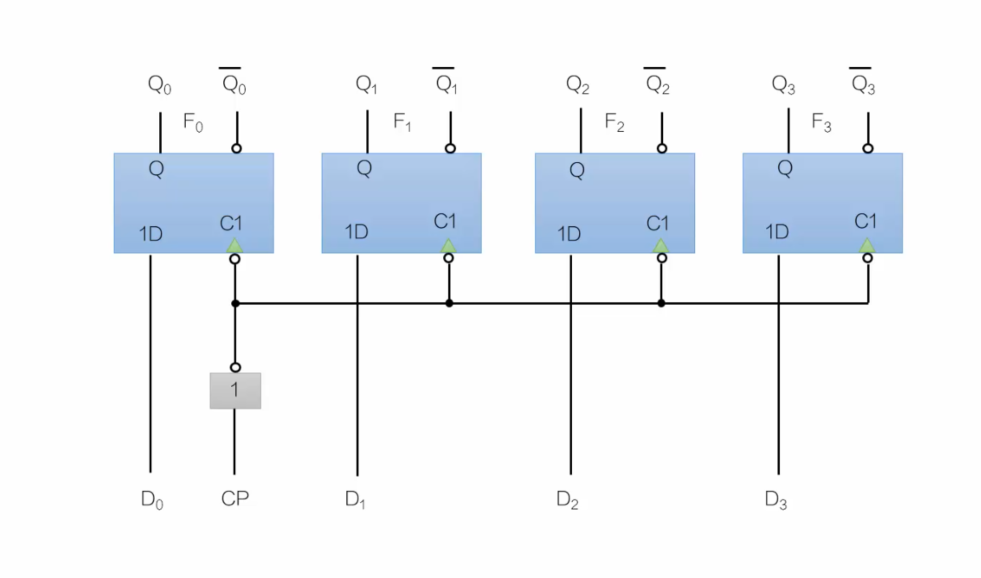

寄存器:能存储多位2进制数码的时序电路(只是多了几个触发器)

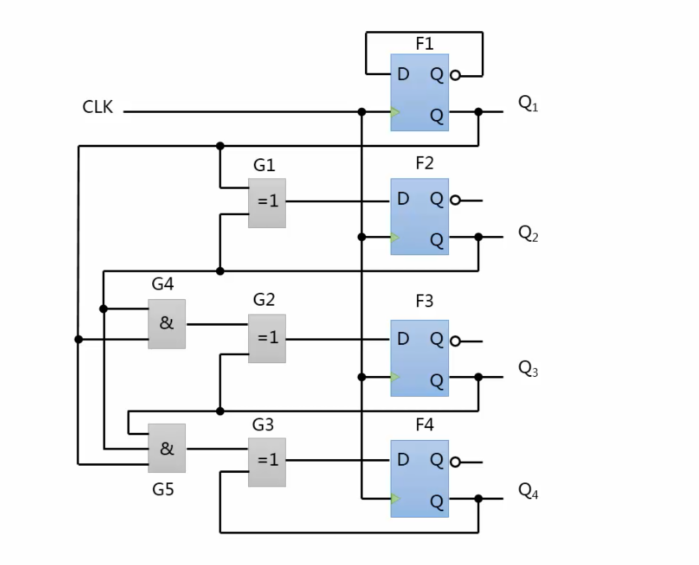

计数器:统计输入脉冲CLK边沿个数(输入的改变要在边沿来临之前,

即先改变D输入,在边沿来临时把D输入赋值给Q,这也能解释为什么把时序和逻辑分开写的原因,核心在于组合部分)

首先假设Q1-Q4是0,此时可以得到D1=1,当第一个上升沿到来时,Q1=1,但是注意此时仅仅只有Q1改变了(因为在那个沿的时候只有Q1的输入D是和上一次不同的),此时输入给Q2的D2变成了1

第二个上升沿到来前情况是:D1输入为0,D2变成了1。

因此在边沿的时候,Q1再度变成0,而Q2会变成1

第三个上升沿到来前:Q1=0,Q2=1,此时D1=1,D2=1,因此到来后,Q1,Q2为11,而Q3还是0

第四个上升沿:Q1,Q2,Q3=110,而此时D的情况为D1=0,D2=0(因为异或),而此时D3=1,下一刻为001

最后

以上就是动听心情最近收集整理的关于时序逻辑电路的全部内容,更多相关时序逻辑电路内容请搜索靠谱客的其他文章。

![CountDownLatch倒计数锁存器(Latch:门闩[shuan])](https://www.shuijiaxian.com/files_image/reation/bcimg22.png)

发表评论 取消回复