什么是代数环?

在Simulink仿真过程中,当输入信号直接取决于输出信号,同时输出信号也直接取决于输入信号时,由于数字计算的时序性,而出现的由于没有输入无法计算输出,没有输出也无法得到输入的“ 死锁环” ,称之为代数环。

代数环的产生

简单地说,代数环其实就是一个输入信号包含输出信号,同时输出信号也包含输入信号的特殊反馈回路。在simulink中,这是由于直通模块(无延时的模块)的原因造成的,simulink中大部分的模块都是直通模块,因此很容易形成代数环。在整个回路中,只包含直通模块就会形成代数环。

代数环的检查

利用Simulink的Diagnostics选项对代数环进行检查,如图:

代数环出现后的影响

当模型中存在代数环后,会出现下列两种结果:

- Simulink执行仿真

- Simulink仿真报错

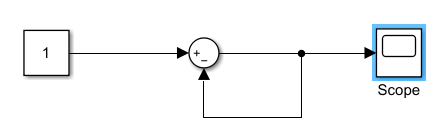

存在代数环,有些情况下模型仍然能仿真,但其结果也不一定正确,例如:

其仿真结果如下:

很明显不是我们想要的结果。

代数环的解决方法

当模型中存在了代数环,其解决方法有以下几种:

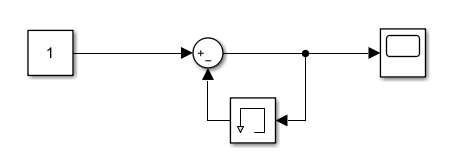

添加Memory模块

仿真结果

添加unit delay模块

采用变换法消除代数环

这种方法仅仅针对简单的代数环有限,对于复杂的代数环基本不可能实现。

通常情况下,大型模型中,代数环往往存在于subsystem中,这种方法不再适用。

在反馈回路中加入高频传递环节

这种方式相当于打断反馈回路的直通模块,消除了输入信号与输出信号的关联关系。

最后

以上就是彩色灯泡最近收集整理的关于[Simulink] 代数环问题笔记的全部内容,更多相关[Simulink]内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

![[Simulink] 代数环问题笔记](https://www.shuijiaxian.com/files_image/reation/bcimg10.png)

发表评论 取消回复