1、分析

基于寄存器的计数器比较常见,时钟上升沿加1即可;基于D触发器的计数器,需要进行状态映射,将计数器的各位对应到各个触发器上,本质即为状态机的次态设计。

2、设计

以4进制计数器为例,使用D触发器实现该功能;

为实现4进制计数器,需要2个D触发器,状态编码如下:

cnt:00-01-10-11

Q1Q0:00-01-10-11

| Q1Q0 | Q1_nQ0_n |

| 00 | 01 |

| 01 | 10 |

| 10 | 11 |

| 11 | 00 |

进一步得到状态方程:

Q0_n = ~Q0;

Q1_n = (~Q1&Q0) | (Q1&~Q0);

3、验证

代码:

`timescale 1ns / 1ps

module d_cnt(

input clk,

input rst_n,

output [1:0]cnt

);

reg Q1,Q0;

wire Q1n,Q0n;

wire Q1_w,Q0_w;

always@(posedge clk or negedge rst_n)

begin

if(!rst_n)

begin

{Q1,Q0} <= 2'b00;

end

else

begin

{Q1,Q0} <= {Q1n,Q0n};

end

end

assign Q0_w = Q0;

assign Q1_w = Q1;

assign Q0n = !Q0_w;

assign Q1n = (!Q1_w&Q0_w)|(Q1_w&!Q0_w);

assign cnt = {Q1,Q0};

endmodule

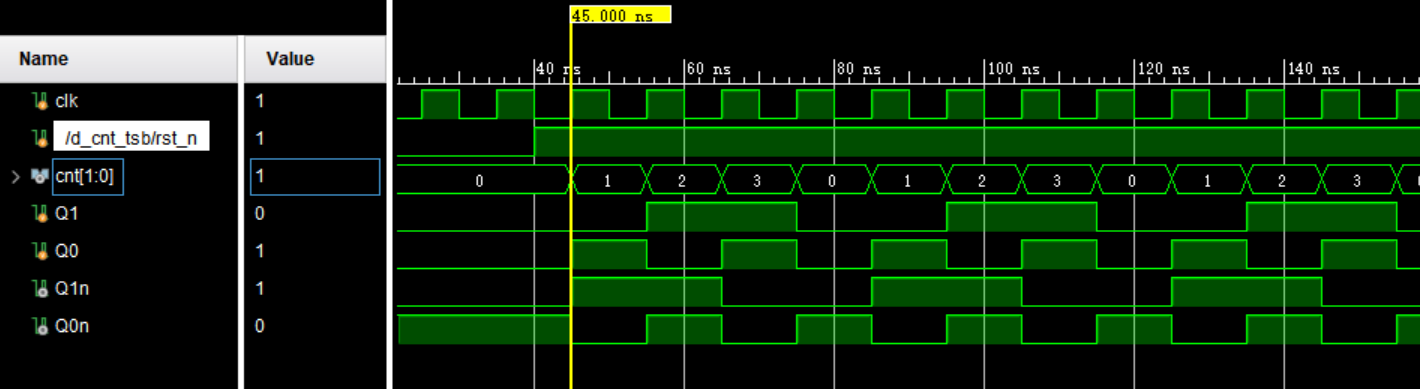

仿真:

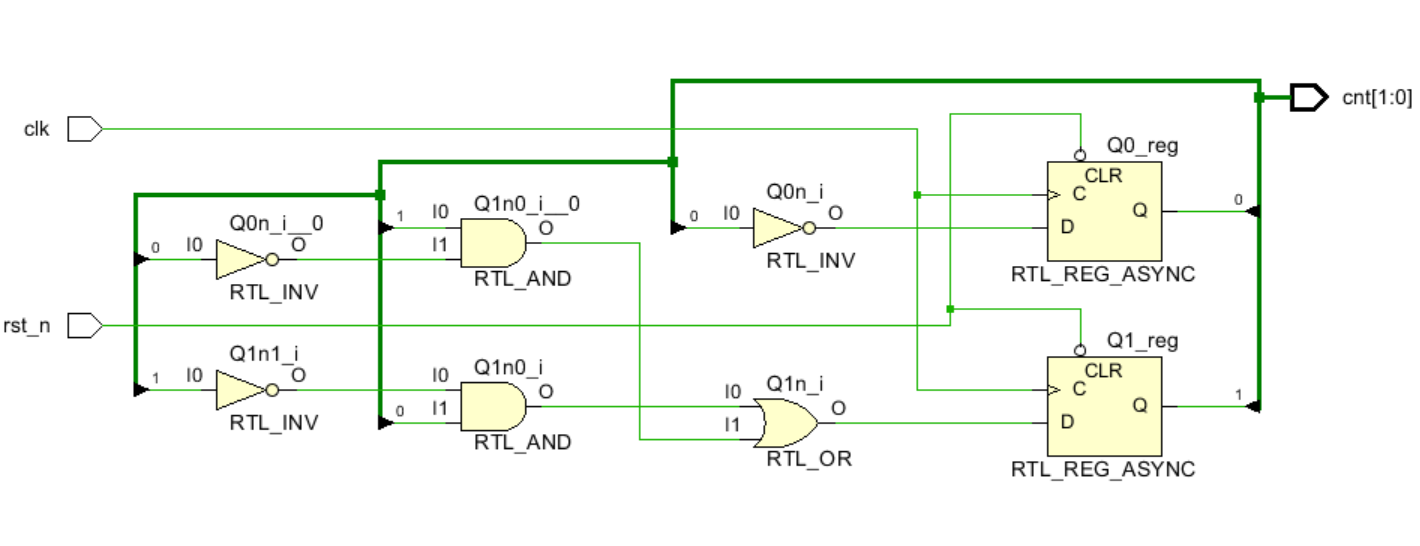

电路:

最后

以上就是勤奋金毛最近收集整理的关于D触发器实现计数器的全部内容,更多相关D触发器实现计数器内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复