文章目录

- 一、加法器——行为级描述

- 二、数据选择器——四选一

- 三、译码器——3线-8线

- 四、触发器——同步复位与异步复位

- 五、寄存器——数据寄存与移位寄存

- 六、计数器——二进制与非二进制计数器

- 七、简单偶分频电路(2^n)

- 八、简单奇数分频电路

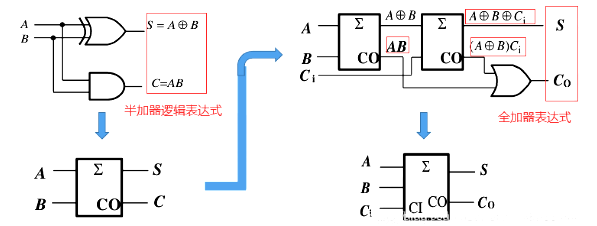

一、加法器——行为级描述

- 半加器:只考虑

两个加数本身,而没有考虑进位位的加法运算的逻辑电路。 - 全加器:能够进行

加数、被加数以及来自低位的进位信号相加,并根据进位位信号给出该位的进位信号的逻辑电路。

一位全加器行为级描述如下:

module one_bit_fa(A,B,Cin,sum,cout);

input

A,B,Cin;

output

sum,cout;

assign {cout,sum} = A+B+Cin;

//行为级描述,完成加法运算

endmodule

扩展——多位加法器描述

8位二进制加法器代码如下:

module N_bit_fa(A,B,Cin,sum,cout);

module 8bit_fa(A,B,Cin,sum,cout);

parameter

N = 4;

input [7:0]

A,B;

input [N-1:0]

A,B;

input

Cin;

input

Cin;

output[7:0]

sum;

output[N-1:0]

sum;

output

cout;

output

cout;

assign

{cout,sum} = A+B+Cin;

assign

{cout,sum} = A+B+Cin;

endmodule

endmodule

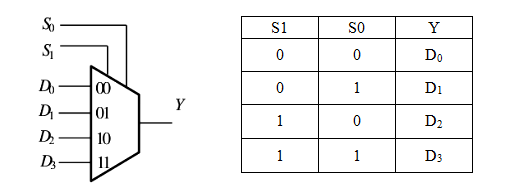

二、数据选择器——四选一

module mux4_1(out,in0,in1,in2,in3,sel);

input

in0,in1,in2,in3;

input [1:0] sel;

output reg

out;

always@(*)begin

//verilog-2001语法,等价于always@(in0 or in1 or in2 or in3 or sel)

case(sel)

2'b00: out = in0;

//组合逻辑,使用阻塞赋值

2'b01: out = in1;

2'b10: out = in2;

2'b11: out = in3;

default: out = 2'bx;

endcase

end

endmodule

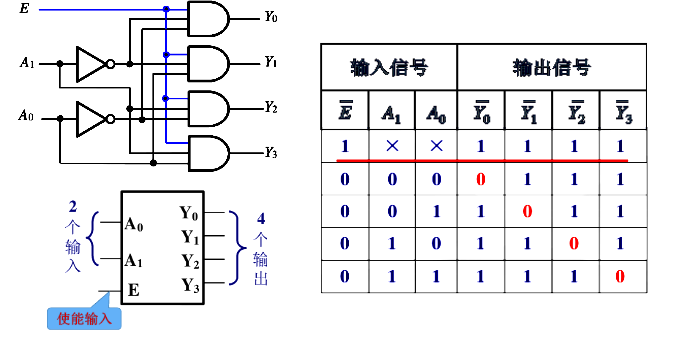

三、译码器——3线-8线

- 下图为2线—4线译码器原理图,编码时扩展至3线—8线译码。

module decoder_38(out,enable,in);

input

enable;

input [2:0]

in;

output reg[7:0] out;

always@(in or enable)begin

if(!enable)

out = 8'b0;

else

case(in)

3'b000:out = 8'b0000_0001;

3'b001:out = 8'b0000_0010;

3'b010:out = 8'b0000_0100;

3'b011:out = 8'b0000_1000;

3'b100:out = 8'b0001_0000;

3'b101:out = 8'b0010_0000;

3'b110:out = 8'b0100_0000;

3'b111:out = 8'b1000_0000;

default:out = 8'b0000_0000;

endcase

end

endmodule

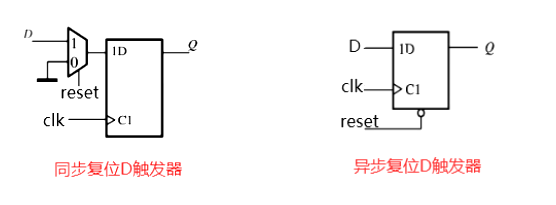

四、触发器——同步复位与异步复位

- 同步复位D触发器与异步复位D触发器仅在敏感事件列表上有所不同,对于异步复位触发器的敏感信号列表需添加复位信号。

- 同步复位D触发器

2. 异步复位D触发器

module DFF_sync(D,Q,clk,reset);

module DFF_async(D,Q,clk,reset);

input

D,clk,reset;

input

D,clk,reset;

output reg

Q;

output reg

Q;

always@(posedge clk) begin

always@(posedge clk or negedge reset)begin

if(!reset)

if(!reset)

Q <= 0;

Q <= 0;

//时序逻辑采用非阻塞赋值 “<=”

else

else

Q <= D;

Q <= D;

//Q为always块中被赋值,需要求reg类型

end

end

endmodule

endmodule

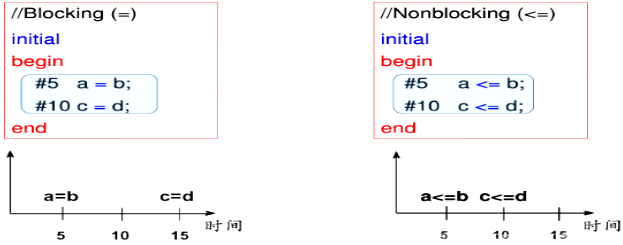

补充说明:阻塞型赋值与非阻塞性赋值的区别

- 阻塞型赋值:使用 “=”号, 串行执行语句,即前一条语句没有完成赋值过程之前,后面的语句不会被执行。

- 非阻塞赋值:使用 “<=”号,并行执行语句,即语句的执行顺序与语句位置无关,一条非阻塞语句的执行不影响块中其他语句的执行。

- RTL设计中,习惯性将阻塞赋值用于组合逻辑中,非阻塞赋值用于时序逻辑中。

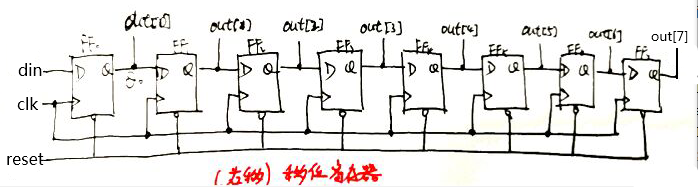

五、寄存器——数据寄存与移位寄存

- 寄存器:寄存器由触发器组成,用来存储二进制数据,1个触发器可以存储1个二进制数据,N位寄存器需用N个触发器组成,可以用来存储N为二进制数据。

- 下图为一个右移位寄存器原理图

- 8位数据寄存器

(并行输入数据)

module reg8(Q, data, clk, reset);

input[7:0]

data;

input

clk,reset;

output reg[7:0]

Q;

always@(posedge clk,negedge reset)begin

if(!reset)

Q <= 0;

else

Q <= data;

//寄存数据

end

endmodule

-

8位左移位寄存器

(串行输入数据)

module shifter(dout,din,clk,reset);

input

din,clk,reset;

output reg[7:0]

dout;

always@(posedge clk)begin

if(!reset)

dout <= 8'b0;

else begin

dout <= dout << 1;

//输出信号左移一位

dout[0] <= din;

//输入信号补充到输出信号的最低位

end

end

endmodule

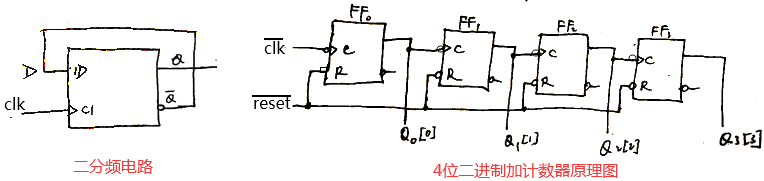

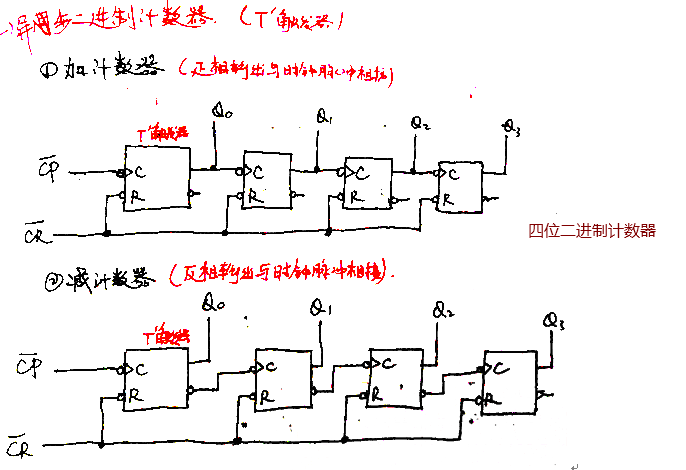

六、计数器——二进制与非二进制计数器

- 计数器是常用时序电路之一,且种类繁多,有同步和异步之分。常用的有二进制计数器和非二进制计数器,按照二进制自然数递增或递减编码的计数器称为二进制计数器。N为二进制

计数器的模为2^N,由N个触发器组成。 - 计数器不仅可以用来计数,也可作为

分频器使用(当计数器的周期保持不变时)。 - 计数器的状态跳转由两种实现方法:

反馈清零法、反馈置数法。

1.二进制计数器

1)、1位二进制计数器(二分频电路)

4位二进制计数器

module counter2bit(

module counter16bit(

input

clk,reset,

input

clk,reset,

output reg

Q

output reg[3:0]

Q

);

);

always@(posedge clk,negedge reset)begin

always@(posedge clk,negedge reset)begin

if(!reset)

if(!reset)

//异步复位

Q <= 1'b0;

Q <= 1'b0;

else

else

//计数

Q <= ~Q;

Q <= Q + 1'b1;

end

end

endmodule

endmodule

2)、下面为一个**同步置数、同步清零**的二进制计数器

module count_en(

input

clk,reset,enable,

input [7:0]

D,

output reg[7:0] Q

);

always@(posedge clk)begin

if(!reset)

Q <= 8'h0;

//同步清零,低电平有效

else if(enable)

Q <= Q + 1;

//计数

else

Q <= Q;

//默认保持不变

end

endmodule

2. 任意进制计数器——以十进制计数器为例(非自然递增)

1)、下面为一个带有**使能端、异步清零**的同步模10计数器,最少需要4个触发器

module m10_counter(

//verilog 2001,2005的语法

input

enable, clk, reset,

//输入端口声明

output reg[3:0] Q

//输出端口以及变量类型声明

);

always@(posedge clk, negedge reset)begin

if(!reset)

Q = 4'b0;

//异步清零

else if(enable)

//使能enable=1,有下面的模块完成模10计数

begin

if(Q == 4'b1001)

Q <= 4'b0;

//反馈清零法计数,十进制计数最大值为9,即1001,如果将其改为1010,则变为十一进制计数器

else

Q <= Q + 1'b1;

end

else

Q <= Q;

//输出保持不变(默认情况)

end

endmodule

上述代码中的计数部分也可采用反馈置数法计数:

if(Q == 4'b0000)

Q <= 4'b1001; //反馈置数法计数

else

Q <= Q - 1;

2). 复位值可配置的7进制计数器

module updown_count(out, clk, rst, pre_data);

input

clk, rst;

input [2:0]

pre_data;

output[2:0]

out;

reg[2:0]

cnt;

always@(posedge clk or negedge rst)begin

if(!rst)

cnt <= pre_data;

//同步预置

else if(out==3'b110)

cnt <= 0;

else

cnt <= cnt+1;

//加法计数

end

assign out = cnt;

endmodule

3).前面是累加计数,下面是一个既可以递增也能递减,且具备初始值装载和复位的计数器,代码如下所示:

module updown_count#(parameter N=8)(

input clk,

input clear,

input load,

input up_down,

input [N-1:0] preset_D,

output[N-1:0] cnt_Q

);

reg[N-1:0] cnt;

assign cnt_Q = cnt;

always@(posedge clk)

if(clear)

cnt <= 'h0;

//同步清 0,高电平有效

else if(load)

cnt <= preset_D;

//同步预置

else if(up_down)

cnt <= cnt+1;

//加法计数

else

cnt <= cnt-1;

//减法计数

endmodule

七、简单偶分频电路(2^n)

- 一个最大计数长度为N(从0计数到N-1)的计数器,其最高位的输出,是输入频率的N分频。

计数器实质是对输入的驱动时钟进行计数,所以计数器在某种意义上讲,等同于对时钟进行分频。例如一个最大计数长度为N=2^n (从0计数到N-1)的计数器,也就是寄存器位数为n,那么寄存器最高位的输出为N=2 ^n分频,次高位为N/2分频。

如下N=3的8分频代码:(N=2——4分频;N=1——2分频)

//N=3时,最高位的输出为输入时钟的8分频

module test#(parameter N=3)(

input clk,

input rst_n,

output clk_div

);

reg [N-1:0] div_reg

;//分频计数器

always @(posedge clk or negedge rst_n)

if (rst_n == 1'b0 )

div_reg

<= 0 ;

else

div_reg

<= div_reg + 1'b1 ;

assign clk_div = div_reg[N-1] ;

endmodule

八、简单奇数分频电路

当N不是2的整数次幂时,即N≠2^n时,从0计数到N-1,其最高位作为时钟输出(占空比不一定为 1:1)是输入时钟的1/N,也就是N分频。我们来举个例子,比如最大计数长度为5的计数器,即从0计数到4后又返回0,那么需要定义一个三位的寄存器。寄存器的计数过程为:

000-001-010-011-100-000-001-010-011-100-000-001-010-011-100-000-001-010-011-100······

我们取最高位,得到的信号变化就是:

0-0-0-0-1-0-0-0-0-0-1-0-0-0-0-1-0-0-0-0-1···

//五分频,计数到5返回0

module test#(parameter N=3)(

input clk,

input rst_n,

output clk_div);

reg [N-1:0] div_reg

;//分频计数器

always @(posedge clk or negedge rst_n)

if (rst_n == 1'b0 )

div_reg

<= 0 ;

else if(div_reg == 3'd4)//从0计数到4,然后返回到0,

**5分频**

div_reg

<= 0;

else

div_reg

<= div_reg + 1'b1 ;

assign clk_div = div_reg[N-1] ;

endmodule

分频电路参考:https://blog.csdn.net/weixin_34126557/article/details/86246646?utm_medium=distribute.pc_relevant.none-task-blog-BlogCommendFromMachineLearnPai2-3.compare&depth_1-utm_source=distribute.pc_relevant.none-task-blog-BlogCommendFromMachineLearnPai2-3.compare

最后

以上就是俏皮白猫最近收集整理的关于经典组合与时序电路——(加法器、触发器、计数器)一、加法器——行为级描述二、数据选择器——四选一三、译码器——3线-8线四、触发器——同步复位与异步复位五、寄存器——数据寄存与移位寄存六、计数器——二进制与非二进制计数器七、简单偶分频电路(2^n)八、简单奇数分频电路的全部内容,更多相关经典组合与时序电路——(加法器、触发器、计数器)一、加法器——行为级描述二、数据选择器——四选一三、译码器——3线-8线四、触发器——同步复位与异步复位五、寄存器——数据寄存与移位寄存六、计数器——二进制与非二进制计数器七、简单偶分频电路(2^n)八、简单奇数分频电路内容请搜索靠谱客的其他文章。

发表评论 取消回复