提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档

Xilinx FPGA资源解析与使用系列——DSP48E(一)

- 前言

- DSP48E1 Slice Features

- 结构细节

- 总结

前言

以7系列FPGA为参考,参考文档(ug479)

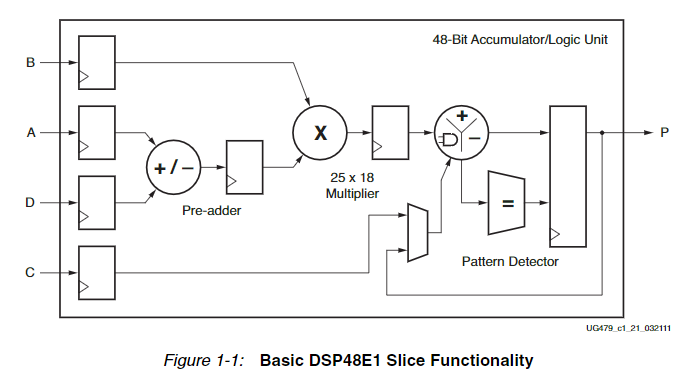

一般来说我们大部分的情况,使用到DSP48E1的时候就是将其理解为乘法器。不管是我们调用IP核还是直接写代码“*”,综合之后都是占用DSP48E1的资源。但久而久之我们就把DSP48E1等效为乘法器了,这就有点小看它了。它可以说是一个微小型的处理器了。

我们来看看它大概有一些什么功能:

1、25 × 18 二进制补码乘法器

2、48-bit累加器(向上累加或者向下递减)

3、低功耗预加器(主要用于滤波器的实现)

4、单指令多数据 (SIMD) 算术单元,可以用作两个24bit/四个12bit 加法器或者减法器或者累加器

5、可以生成两个操作数的十种不同逻辑函数中的任意一种

6、模式检测器:

收敛舍入或对称舍入

与逻辑单元结合使用时的 96 位宽逻辑功能

更进一步的,DSP48E不仅仅有上述这些功能,更牛逼的是有些功能是可以进行动态配置的,例如这个时钟周期是加法器,下个时钟周期就可以配置成减法器,相当于一个小型的MCU了。但我们大部分情况下我们就是将它作为乘法器用。这本来无可厚非,但在资源紧张的时候,了解DSP48E的特性对于你是否能做到更优的设计就至关重要了。

DSP48E1 Slice Features

DSP48E1 Slice 提高了灵活性和利用率,提高了应用效率,降低了整体功耗,并提高了最大频率。 高性能允许设计人员使用时间复用方法在单个 DSP48E1 Slice 中实现多个较慢的操作。

DSP48E1 Slice 支持许多独立的功能。 这些功能包括乘法、乘法累加 (MACC)、乘法加法、三输入加法、桶形移位、宽总线多路复用、幅度比较器、按位逻辑功能、模式检测和宽计数器。 该架构还支持级联多个 DSP48E1 Slice 以形成宽数学函数、DSP 滤波器和复杂算术,而无需使用通用 FPGA 逻辑

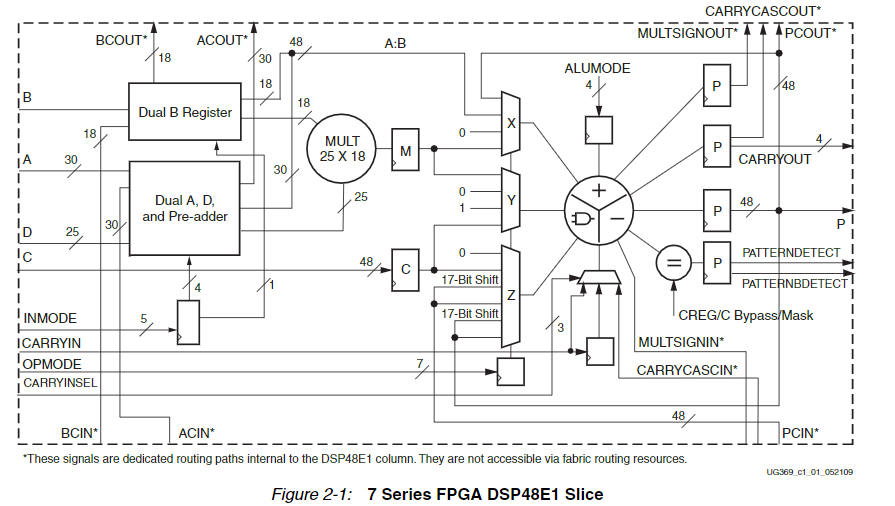

DSP Slice 由一个乘法器和一个累加器组成。乘法和乘法累加运算至少需要三个流水线寄存器才能全速运行。第一阶段的乘法运算产生两个部分乘积,需要在第二阶段相加。

当乘法器设计中只有一两个寄存器时,应始终使用 M 寄存器以节省功耗和提高性能。

加/减和逻辑单元操作至少需要两个流水线寄存器(输入、输出)才能全速运行。

DSP Slice 的级联功能在实现建立在加法器级联而不是加法器树上的高速流水线滤波器方面非常有效。多路复用器由 OPMODE、ALUMODE 和 CARRYINSEL 等动态控制信号控制,具有很大的灵活性。与组合乘法相比,使用寄存器和动态操作模式的设计能够更好地利用 DSP Slice 功能。

通常,由于动态 OPMODE 和级联功能,DSP Slice 支持顺序和级联操作。快速傅立叶变换 (FFT)、浮点、计算(乘法、加法/减法、除法)、计数器和大型总线多路复用器是 DSP Slice 的一些应用。

DSP Slice 的其他功能包括同步复位和时钟使能、双 A 输入流水线寄存器、模式检测、逻辑单元功能、单指令/多数据 (SIMD) 功能以及 MACC 和 Add-Acc 扩展到 96 位。 DSP Slice 支持收敛和对称舍入、计数器的终端计数检测和自动复位以及顺序累加器的上溢/下溢检测

结构细节

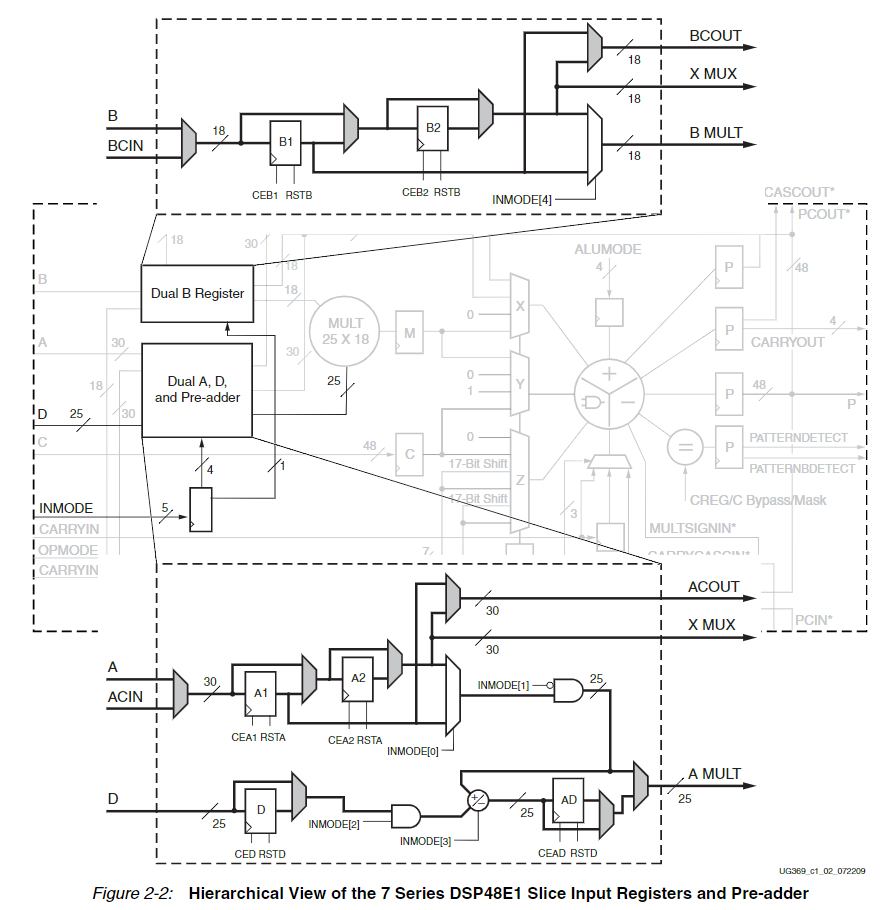

1、带有 D 寄存器的 25 位预加器,以增强 A 路径的能力

2、当在乘法 (A*B) 和加法运算 (A:B) 之间动态切换时,INMODE 控制线支持平衡流水线

3、25 x 18 乘法器

4、30 位 A 输入,其中低 25 位馈送乘法器的 A 输入,整个 30 位输入构成 48 位 A:B 级联内部总线的高 30 位

5、级联 A 和 B 输入

•直接和级联路径之间的半独立可选流水线

• 独立的时钟使能两层深的 A 和 B 输入寄存器组

6、具有独立复位和时钟使能的独立 C 输入和 C 寄存器

7、CARRYCASCIN 和 CARRYCASCOUT 内部级联信号,支持两个 DSP48E1 Slice 中的 96 位累加器/加法器/减法器

8、具有特殊 OPMODE 设置的 MULTSIGNIN 和 MULTSIGNOUT 内部级联信号,以支持 96 位 MACC 扩展

9、三输入加法器/减法器的单指令多数据 (SIMD) 模式,它排除了在第一阶段使用乘法器

- 双 24 位 SIMD 加法器/减法器/累加器,带有两个独立的 CARRYOUT 信号

- 四路 12 位 SIMD 加法器/减法器/累加器,带有四个独立的 CARRYOUT 信号

10、48位逻辑单元

•按位逻辑运算——两输入AND、OR、NOT、NAND、NOR、XOR和XNOR

• 逻辑单元模式可通过 ALUMODE 动态选择

11、模式检测器

•上溢/下溢支持

•收敛舍入支持

•终端计数检测支持和自动重置

12、级联 48 位 P 总线支持内部低功耗加法器级联

• 48 位 P 总线允许 12 位/QUAD 或 24 位/双 SIMD 加法器级联支持

13、可选的 17 位右移以实现更广泛的乘法器实现

14、动态用户控制的操作模式

• 7 位 OPMODE 控制总线提供 X、Y 和 Z 多路复用器选择信号

15、进位为第二阶段加法器

•支持四舍五入

•支持更广泛的加/减

•3 位 CARRYINSEL 多路复用器

16、为第二阶段加法器执行

•支持更广泛的加/减

•适用于每个 SIMD 加法器(最多四个)发送反馈

•级联 CARRYCASCOUT 和 MULTSIGNOUT 允许 MACC 扩展高达 96 位

17、可选的输入、流水线和输出/累加寄存器

18、控制信号的可选控制寄存器(OPMODE、ALUMODE 和 CARRYINSEL)

19、独立的时钟使能和复位具有更大的灵活性,复位优先。

20、 为了在不使用第一级乘法器时省电,USE_MULT 属性允许客户关闭内部乘法器逻辑

每个 DSP48E1 Slice 都有一个双输入乘法器,后跟多路复用器和一个三输入加法器/减法器/累加器。 DSP48E1 乘法器具有非对称输入并接受 18 位二进制补码操作数和 25 位二进制补码操作数。 乘法器级以两个部分乘积的形式产生 43 位二进制补码结果。 这些部分乘积在 X 多路复用器和 Y 多路复用器中被符号扩展为 48 位,并馈入三输入加法器以进行最终求和。 这会产生 43 位乘法输出,该输出已被符号扩展为 48 位。 因此,当使用乘法器时,加法器实际上变成了两输入加法器

第二级加法器/减法器接受三个 48 位二进制补码操作数,并在通过将 USE_MULT 属性设置为 NONE 并使用适当的 OPMODE 设置绕过乘法器时产生一个 48 位二进制补码结果。 在 SIMD 模式下,48 位加法器/减法器还支持带有 CARRYOUT 位的双 24 位或四路 12 位 SIMD 算术运算。 在此配置中,动态 ALUMODE 控制信号也支持对两个 48 位二进制数的按位逻辑运算。

通过在 DSP48E1 列中级联单个 DSP48E1 Slice,可以支持更高级别的 DSP 功能。 两个数据通路(ACOUT 和 BCOUT)和 DSP48E1 Slice 输出(PCOUT、MULTSIGNOUT 和 CARRYCASCOUT)提供级联功能。 级联数据路径的能力在滤波器设计中很有用。 例如,有限脉冲响应 (FIR) 滤波器设计可以使用级联输入来排列一系列输入数据样本,使用级联输出来排列一系列部分输出结果。 级联能力提供了高性能和低功耗的 DSP 滤波器功能实现,因为没有使用结构中的通用路由。

C 输入端口允许形成许多 3 输入数学函数,例如 3 输入加法或带加法的 2 输入乘法。此函数的一个子集是对乘法向零或向无穷大对称舍入的宝贵支持。 C 输入与模式检测器一起也支持收敛舍入。

对于多精度算术,DSP48E1 Slice 提供右移 17 位。因此,来自一个 DSP48E1 Slice 的部分乘积可以右对齐并添加到相邻 DSP48E1 Slice 中计算的下一个部分乘积。使用这种技术,DSP48E1 Slice 可用于构建更大的乘法器。

输入操作数、中间产品和累加器输出的可编程流水线提高了吞吐量。 48 位内部总线 (PCOUT/PCIN) 允许在单个列中聚合 DSP Slice。跨越多列时需要结构逻辑。

DSP48E1 Slice 输出端的模式检测器支持收敛舍入、上溢/下溢、块浮点,并支持累加器终端计数(计数器自动复位)。模式检测器可以检测 DSP48E1 Slice 的输出是否与模式匹配,如掩码所限定

总结

第一篇主要就是阐述了一下DSP48E1的一些功能。基本就是翻译了一下手册。主要目的就是要认识到DSP48E1不仅仅是一个乘法器,它可以实现很多功能,还能动态配置。

下一篇再介绍其原语模型,以及哪些关键信号是我们要注意的。

最后其他篇将结合我自己的实践,将DSP48E1配置成

1、加乘器 (相关器)

P = P +A*B

2、多路累加器 (相关器)

P1 = P1 +/- C1

P2 = P2 +/- C2

最后

以上就是魁梧自行车最近收集整理的关于Xilinx FPGA资源解析与使用系列——DSP48E(一)前言DSP48E1 Slice Features结构细节总结的全部内容,更多相关Xilinx内容请搜索靠谱客的其他文章。

发表评论 取消回复