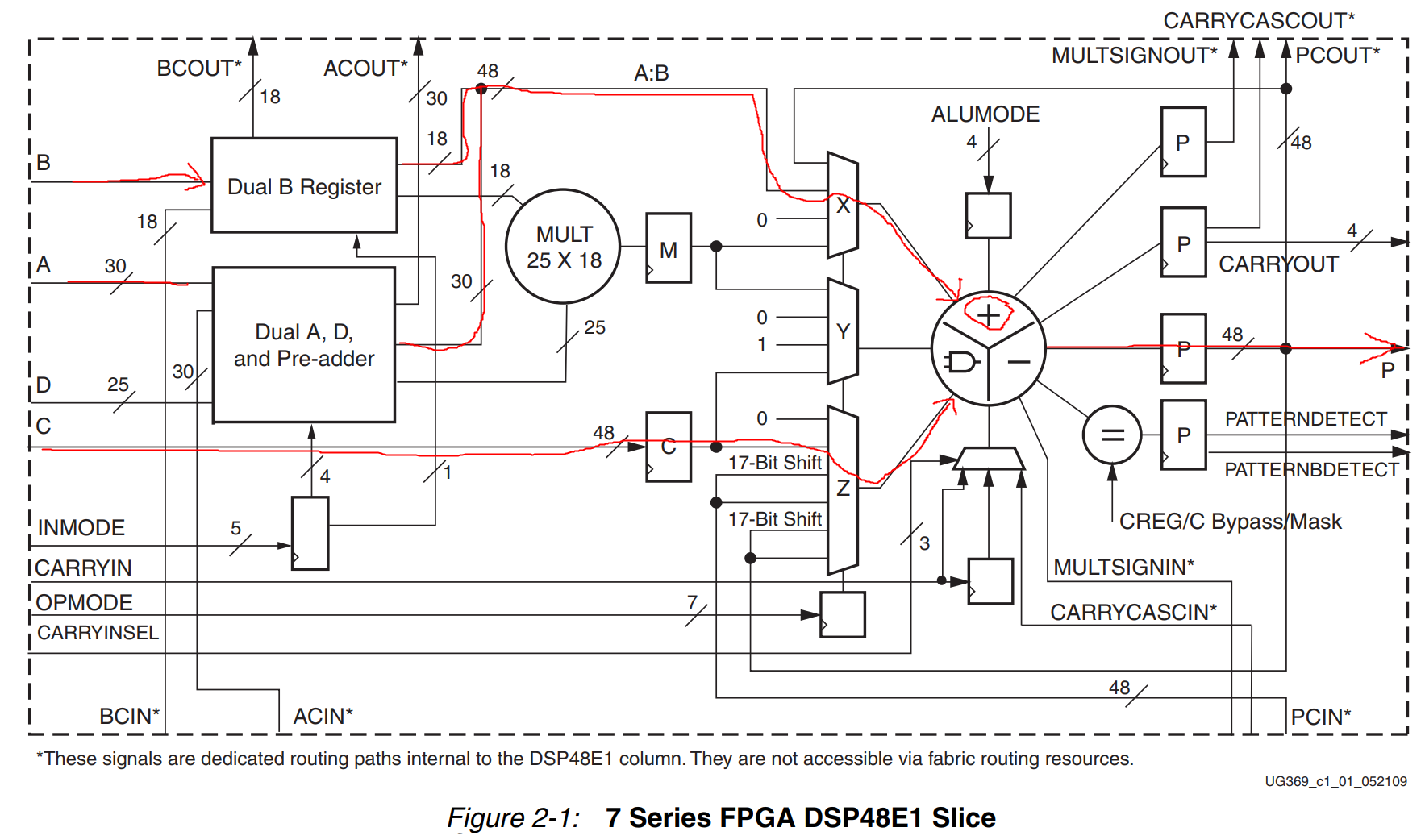

1. 实现48bit加法

quad

由A:B组合一个48bit数据与C相加,D端口禁用。

quad

调用原语实现。

1.1. 参数配置

quad

USE_DPORT = FALSE;

quad

USE_MULT = NONE;乘法器必须禁用

quad

USE_SIMD = ONE48;

quad

USE_PATTERN_DETECT = NO_PATDET;

quad

AREG=2;BREG=2;A、B通道选择两级pipeline

quad

MREG=0;USE_MULT = NONE时MREG必须等于0

1.2. 端口输入

1) INMODE寄存器

quad

A、B通道经过X MUX路径,INMODE取值对这个路径没影响所以取默认值0

2) OPMODE寄存器

quad

OPMODE[1:0] = 11;X MUL选择A:B组合输出

quad

OPMODE[3:2] = 11;Y MUL选择C输出

quad

OPMODE[6:4] = 000;Z MUL输出0

3) ALUMODE寄存器

quad

ALUMODE[3:0] = 0000;选择Z+X+Y+CIN

4) CARRYINSEL寄存器

quad

选择CARRYINSEL多路复用通道的输出通道

quad

CARRYINSEL[2:0] = 000;选择CARRYIN

5) A、C、CIN

quad

A:B =48’h8000_0000_080f

quad

C =48’h8000_0000_080f

quad

CIN=1

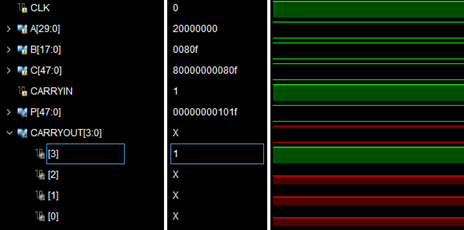

1.3. 仿真结果

P=X+Y+Z+CIN

X=A=48’h8000_0000_080f

Y=C=48’h8000_0000_080f

Z=0

CIN=1

P=48’h1_0000_0000_101f

CARRYOUT[3] = 1

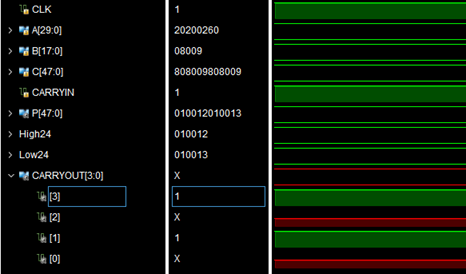

2.实现两个24bit加法

2.1. 配置参数

quad

USE_SIMD = TWO24;

quad

其他参数不变

2.2. 端口输入

quad

A:B = 48’h8080_0980_8009

quad

C = 48’h8080_0980_8009

quad

CIN=1

2.3. 仿真结果

P[23:0] = 24’h01_0013

CARRYOUT[1] = 1

P[47:24] = 24’h01_0012

CARRYOUT[3] = 1

3.参考

ug479_7Series_DSP48E1

https://blog.csdn.net/Leo_9824/article/details/118707437?spm=1001.2014.3001.5501

https://download.csdn.net/download/Leo_9824/20255360?spm=1001.2014.3001.5503

4.代码

DSP48E1 #(

// Feature Control Attributes: Data Path Selection

.A_INPUT("DIRECT"),

// Selects A input source, "DIRECT" (A port) or "CASCADE" (ACIN port)

.B_INPUT("DIRECT"),

// Selects B input source, "DIRECT" (B port) or "CASCADE" (BCIN port)

.USE_DPORT("FALSE"),

// Select D port usage (TRUE or FALSE)

.USE_MULT("NONE"),

// Select multiplier usage ("MULTIPLY", "DYNAMIC", or "NONE")

.USE_SIMD("TWO24"),

// SIMD selection ("ONE48", "TWO24", "FOUR12")

// Pattern Detector Attributes: Pattern Detection Configuration

.AUTORESET_PATDET("NO_RESET"),

// "NO_RESET", "RESET_MATCH", "RESET_NOT_MATCH"

.MASK(48'h3fffffffffff),

// 48-bit mask value for pattern detect (1=ignore)

.PATTERN(48'h000000000000),

// 48-bit pattern match for pattern detect

.SEL_MASK("MASK"),

// "C", "MASK", "ROUNDING_MODE1", "ROUNDING_MODE2"

.SEL_PATTERN("PATTERN"),

// Select pattern value ("PATTERN" or "C")

.USE_PATTERN_DETECT("NO_PATDET"), // Enable pattern detect ("PATDET" or "NO_PATDET")

// Register Control Attributes: Pipeline Register Configuration

.ACASCREG(1),

// Number of pipeline stages between A/ACIN and ACOUT (0, 1 or 2)

.ADREG(1),

// Number of pipeline stages for pre-adder (0 or 1)

.ALUMODEREG(1),

// Number of pipeline stages for ALUMODE (0 or 1)

.AREG(2),

// Number of pipeline stages for A (0, 1 or 2)

.BCASCREG(1),

// Number of pipeline stages between B/BCIN and BCOUT (0, 1 or 2)

.BREG(2),

// Number of pipeline stages for B (0, 1 or 2)

.CARRYINREG(1),

// Number of pipeline stages for CARRYIN (0 or 1)

.CARRYINSELREG(1),

// Number of pipeline stages for CARRYINSEL (0 or 1)

.CREG(1),

// Number of pipeline stages for C (0 or 1)

.DREG(1),

// Number of pipeline stages for D (0 or 1)

.INMODEREG(1),

// Number of pipeline stages for INMODE (0 or 1)

.MREG(0),

// Number of multiplier pipeline stages (0 or 1)

.OPMODEREG(1),

// Number of pipeline stages for OPMODE (0 or 1)

.PREG(1)

// Number of pipeline stages for P (0 or 1)

)

DSP48E1_inst (

// Cascade: 30-bit (each) output: Cascade Ports

.ACOUT(ACOUT),

// 30-bit output: A port cascade output

.BCOUT(BCOUT),

// 18-bit output: B port cascade output

.CARRYCASCOUT(CARRYCASCOUT),

// 1-bit output: Cascade carry output

.MULTSIGNOUT(MULTSIGNOUT),

// 1-bit output: Multiplier sign cascade output

.PCOUT(PCOUT),

// 48-bit output: Cascade output

// Control: 1-bit (each) output: Control Inputs/Status Bits

.OVERFLOW(OVERFLOW),

// 1-bit output: Overflow in add/acc output

.PATTERNBDETECT(PATTERNBDETECT), // 1-bit output: Pattern bar detect output

.PATTERNDETECT(PATTERNDETECT),

// 1-bit output: Pattern detect output

.UNDERFLOW(UNDERFLOW),

// 1-bit output: Underflow in add/acc output

// Data: 4-bit (each) output: Data Ports

.CARRYOUT(CARRYOUT),

// 4-bit output: Carry output

.P(P),

// 48-bit output: Primary data output

// Cascade: 30-bit (each) input: Cascade Ports

.ACIN(ACIN),

// 30-bit input: A cascade data input

.BCIN(BCIN),

// 18-bit input: B cascade input

.CARRYCASCIN(CARRYCASCIN),

// 1-bit input: Cascade carry input

.MULTSIGNIN(MULTSIGNIN),

// 1-bit input: Multiplier sign input

.PCIN(PCIN),

// 48-bit input: P cascade input

// Control: 4-bit (each) input: Control Inputs/Status Bits

.ALUMODE(ALUMODE),

// 4-bit input: ALU control input

.CARRYINSEL(CARRYINSEL),

// 3-bit input: Carry select input

.CLK(CLK),

// 1-bit input: Clock input

.INMODE(INMODE),

// 5-bit input: INMODE control input

.OPMODE(OPMODE),

// 7-bit input: Operation mode input

// Data: 30-bit (each) input: Data Ports

.A(A),

// 30-bit input: A data input

.B(B),

// 18-bit input: B data input

.C(C),

// 48-bit input: C data input

.CARRYIN(CARRYIN),

// 1-bit input: Carry input signal

.D(D),

// 25-bit input: D data input

// Reset/Clock Enable: 1-bit (each) input: Reset/Clock Enable Inputs

.CEA1(1'b1),

// 1-bit input: Clock enable input for 1st stage AREG

.CEA2(1'b1),

// 1-bit input: Clock enable input for 2nd stage AREG

.CEAD(1'b0),

// 1-bit input: Clock enable input for ADREG

.CEALUMODE(1'b1),

// 1-bit input: Clock enable input for ALUMODE

.CEB1(1'b1),

// 1-bit input: Clock enable input for 1st stage BREG

.CEB2(1'b1),

// 1-bit input: Clock enable input for 2nd stage BREG

.CEC(1'b1),

// 1-bit input: Clock enable input for CREG

.CECARRYIN(1'b1),

// 1-bit input: Clock enable input for CARRYINREG

.CECTRL(1'b1),

// 1-bit input: Clock enable input for OPMODEREG and CARRYINSELREG

.CED(1'b0),

// 1-bit input: Clock enable input for DREG

.CEINMODE(1'b1),

// 1-bit input: Clock enable input for INMODEREG

.CEM(1'b0),

// 1-bit input: Clock enable input for MREG

.CEP(1'b1),

// 1-bit input: Clock enable input for PREG

.RSTA(1'b0),

// 1-bit input: Reset input for AREG

.RSTALLCARRYIN(1'b0),

// 1-bit input: Reset input for CARRYINREG

.RSTALUMODE(1'b0),

// 1-bit input: Reset input for ALUMODEREG

.RSTB(1'b0),

// 1-bit input: Reset input for BREG

.RSTC(1'b0),

// 1-bit input: Reset input for CREG

.RSTCTRL(1'b0),

// 1-bit input: Reset input for OPMODEREG and CARRYINSELREG

.RSTD(1'b0),

// 1-bit input: Reset input for DREG and ADREG

.RSTINMODE(1'b0),

// 1-bit input: Reset input for INMODEREG

.RSTM(1'b0),

// 1-bit input: Reset input for MREG

.RSTP(1'b0)

// 1-bit input: Reset input for PREG

);

源码链接:https://download.csdn.net/download/Leo_9824/20255360

环境:vivado2017.4

最后

以上就是欢呼心锁最近收集整理的关于DSP48E1(2)加法运算实例的全部内容,更多相关DSP48E1(2)加法运算实例内容请搜索靠谱客的其他文章。

发表评论 取消回复