我是靠谱客的博主 奋斗哈密瓜,这篇文章主要介绍【FPGA】基于vivado的AM调制与解调(verilog)(三、软件操作篇)1.创建工程,添加设计文件、仿真文件2.调用IP核3.编译与仿真,现在分享给大家,希望可以做个参考。

目录

- 1.创建工程,添加设计文件、仿真文件

- 2.调用IP核

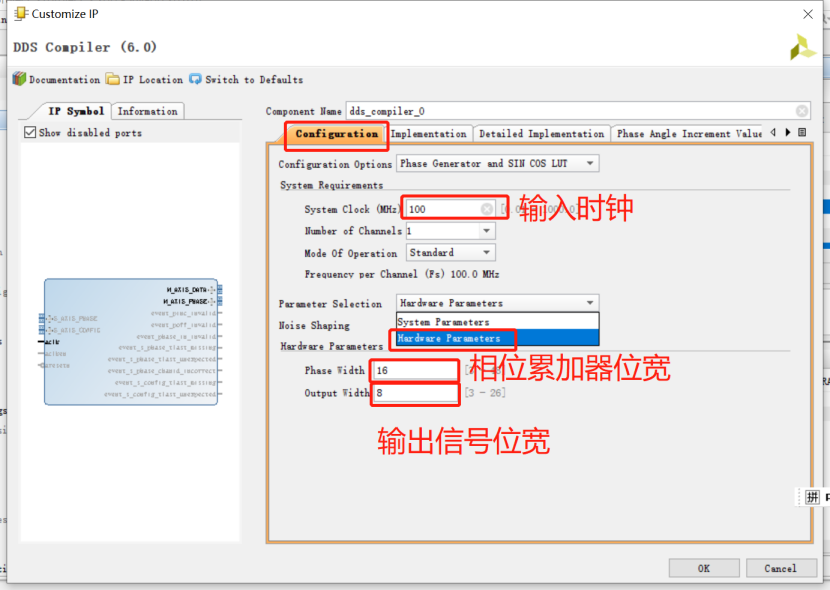

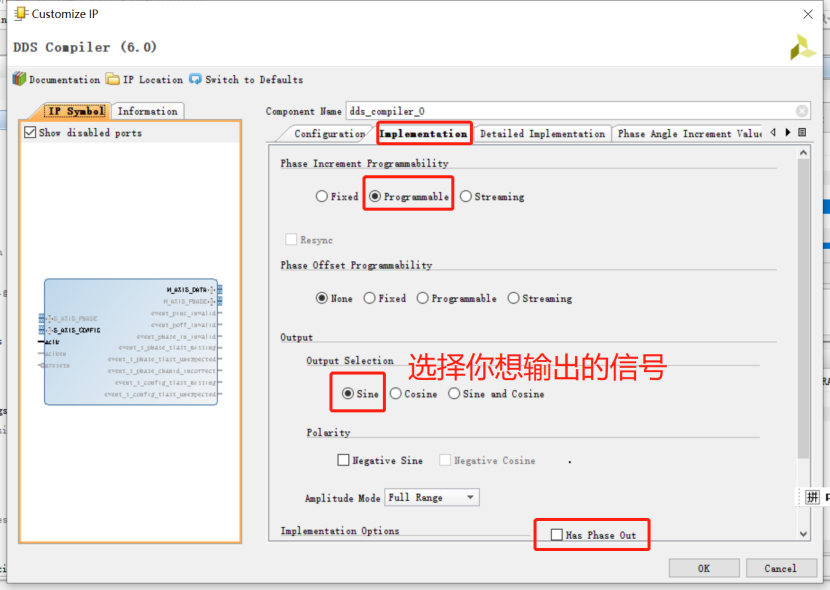

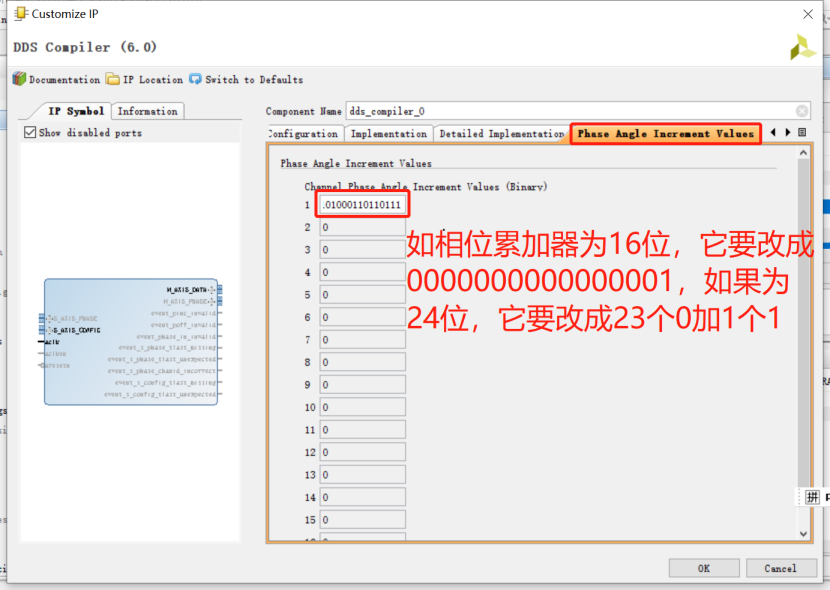

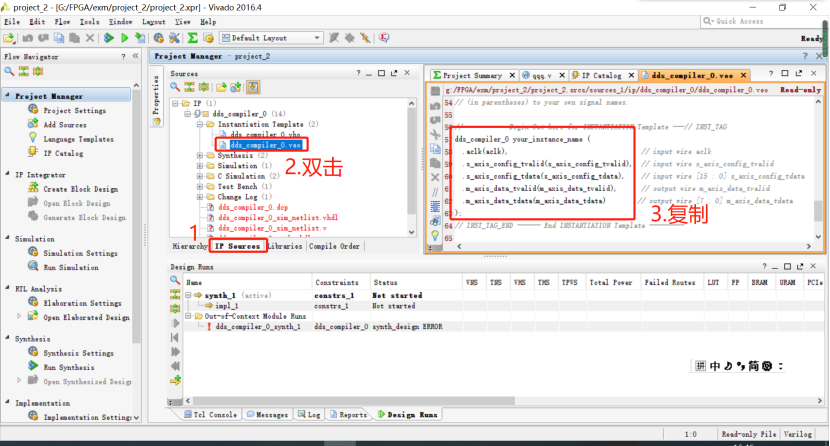

- (1)DDS(产生特定频率正余弦信号的)

- (2)乘法器

- (3)fir滤波器

- 3.编译与仿真

1.创建工程,添加设计文件、仿真文件

打开vivado,创建工程,需要改工程名和选择芯片,其余一路next。(怕芯片要求不一样,就不放图了)。

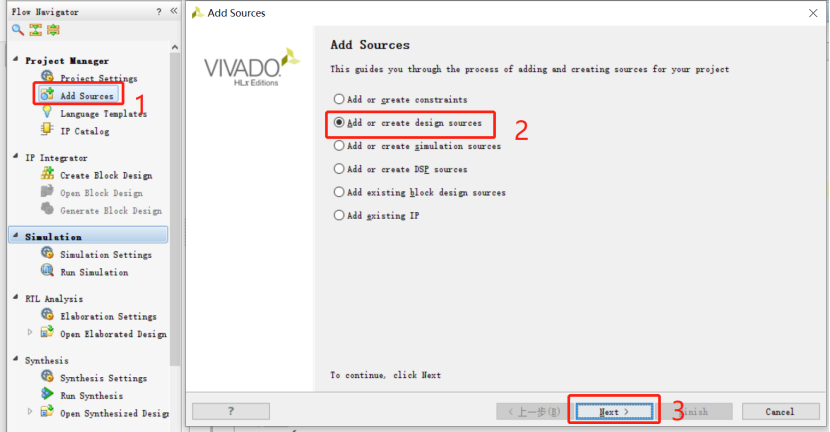

创建好工程后,新建设计文件

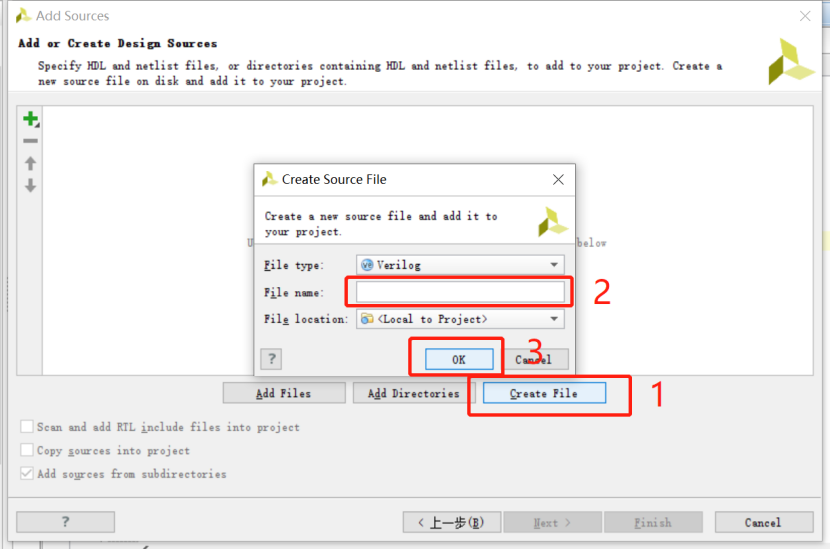

起个名字

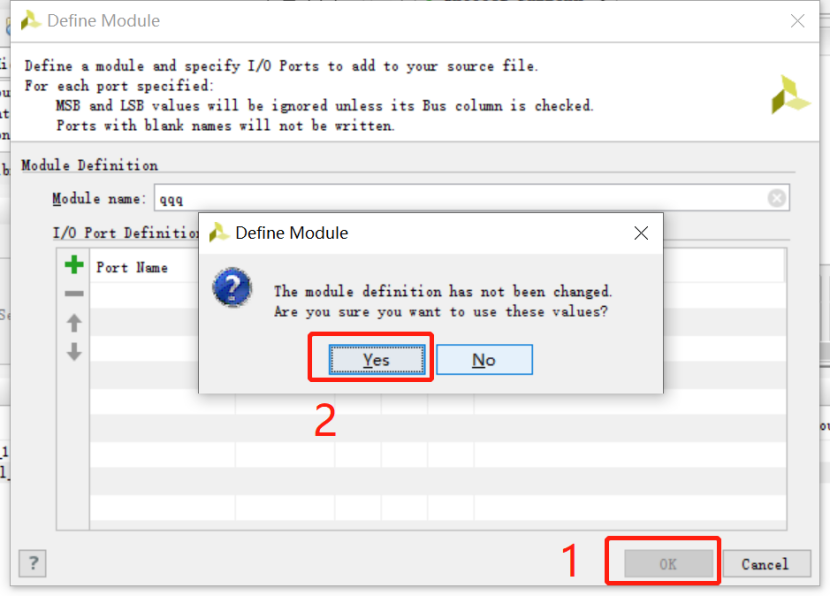

点击finish

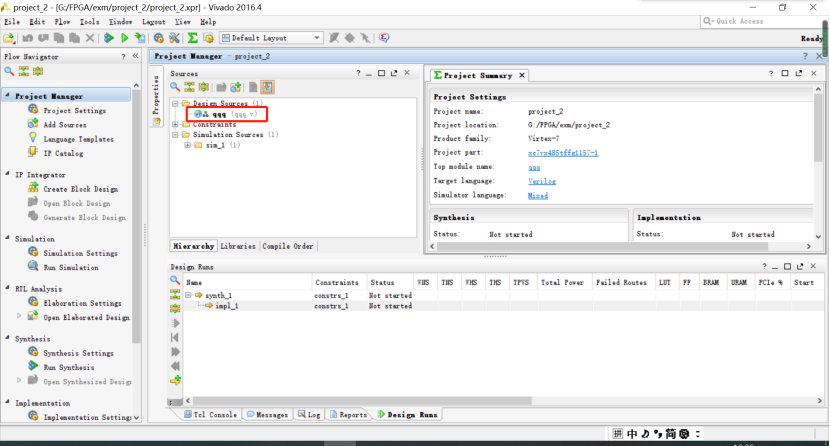

双击打开,即可编写设计程序

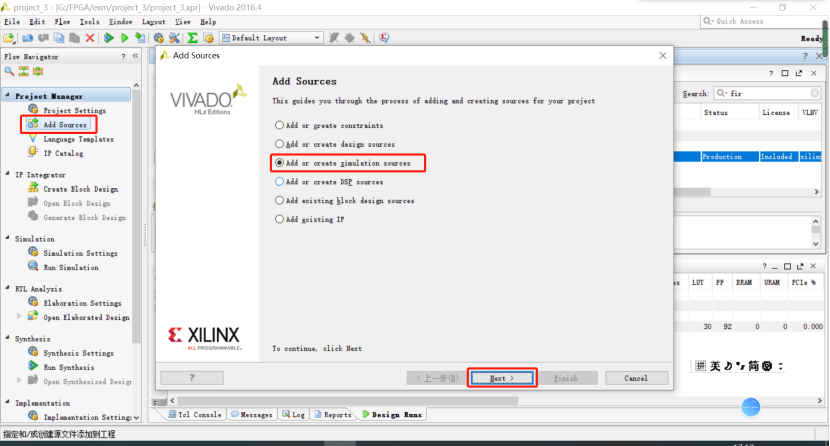

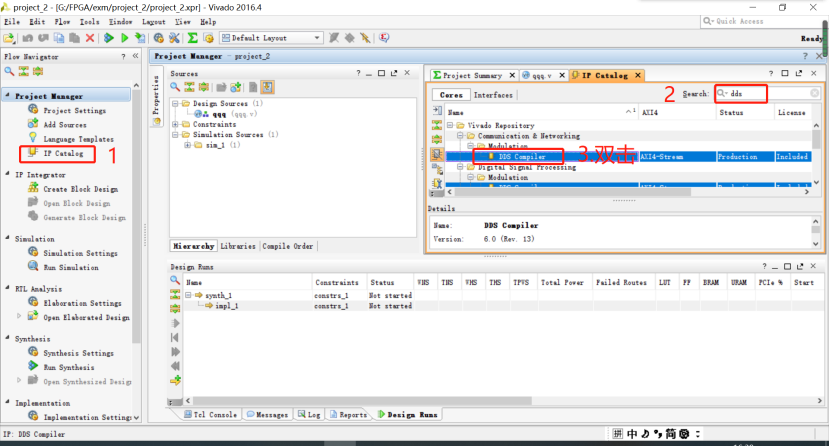

写完设计文件,写仿真文件

命名时,习惯在设计文件名后面加tb作为仿真文件名。

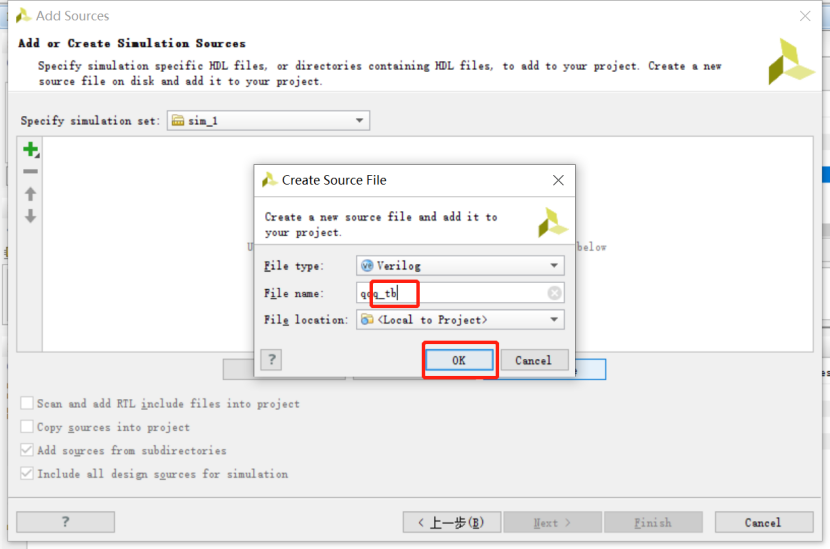

创建完了在这找,双击打开,写程序

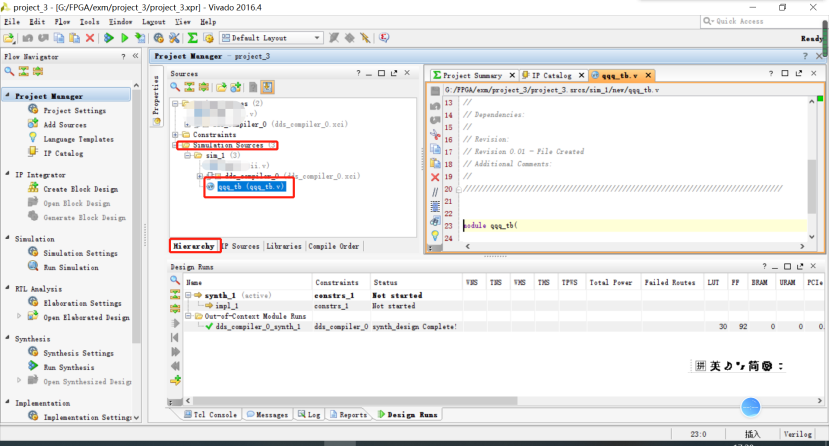

2.调用IP核

(1)DDS(产生特定频率正余弦信号的)

点击OK,OK,generate,等待一会,OK。

复制粘贴到设计文件,改好对应的变量。

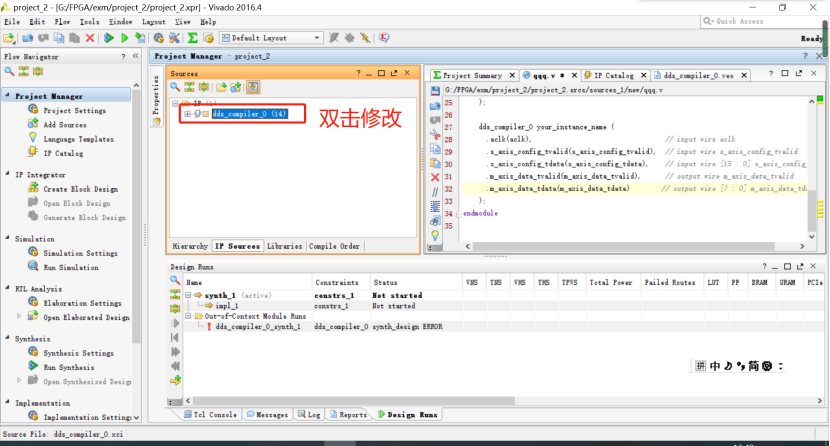

注:IP核参数设置错了怎么办?能直接修改吗?还是要删除重新调用?

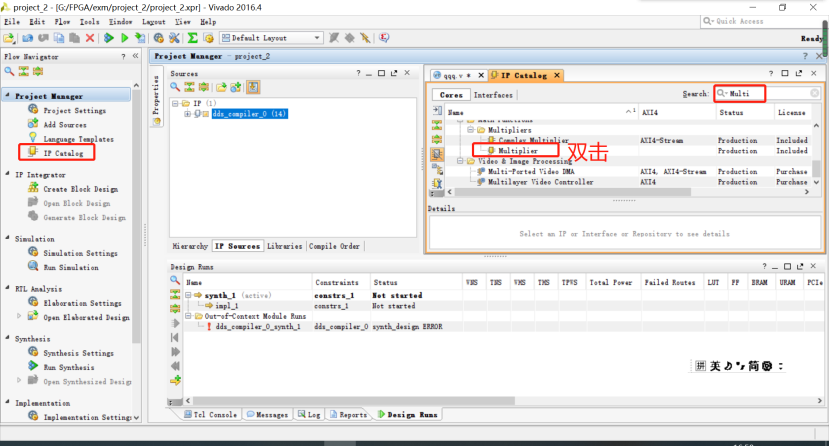

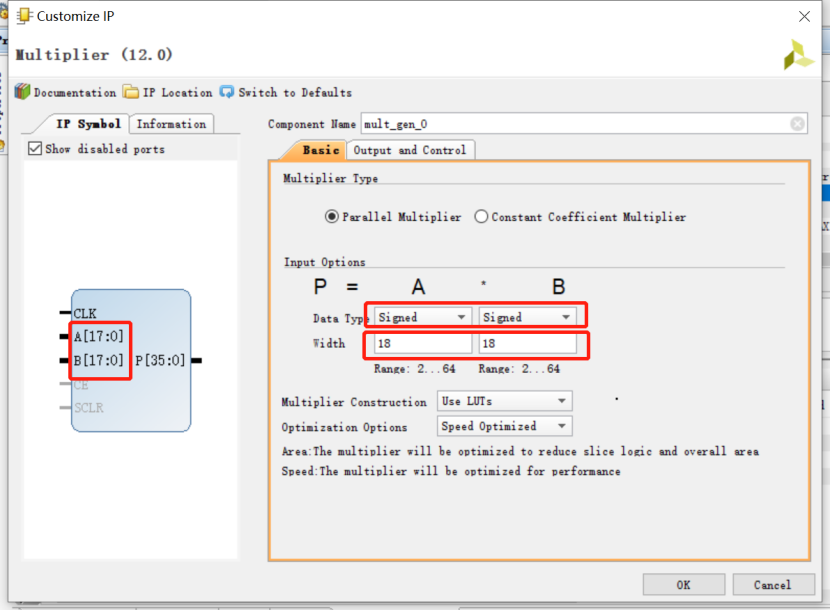

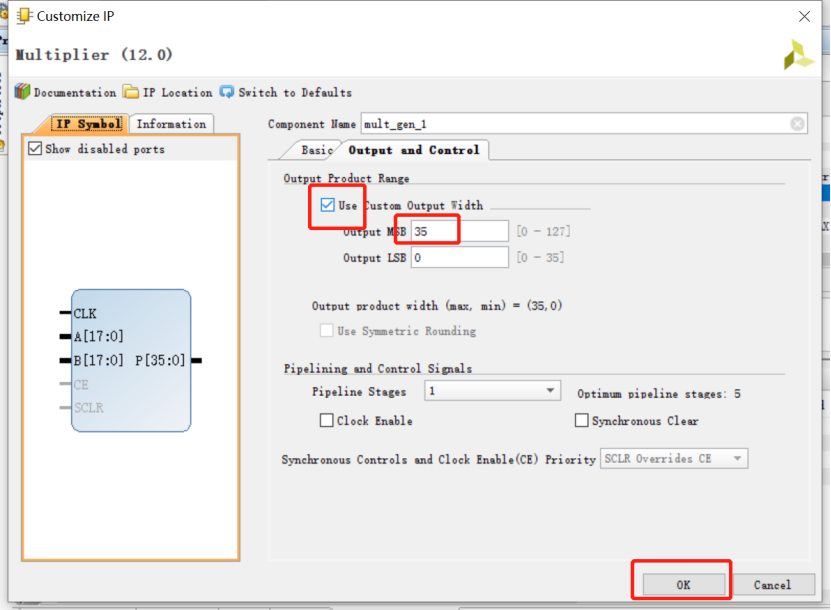

(2)乘法器

设置输入输出符号、位宽,结果预览在左侧。

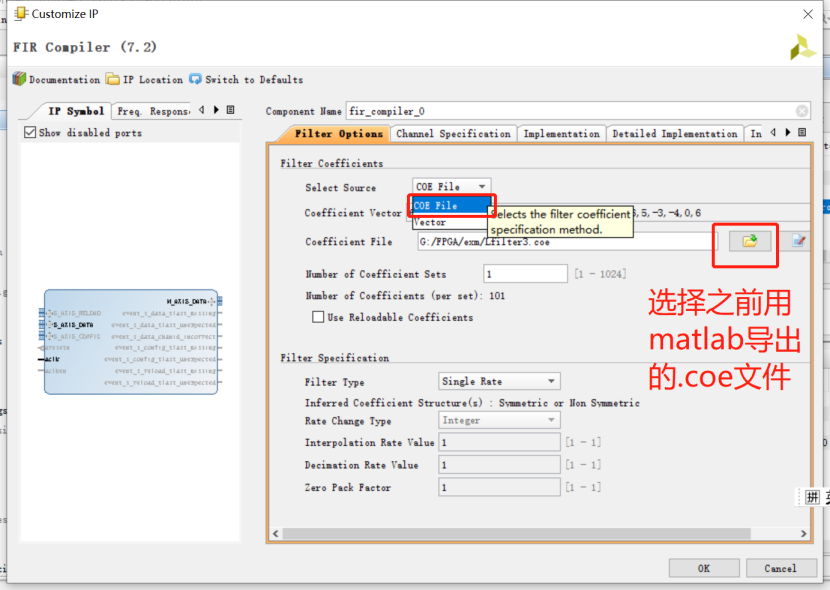

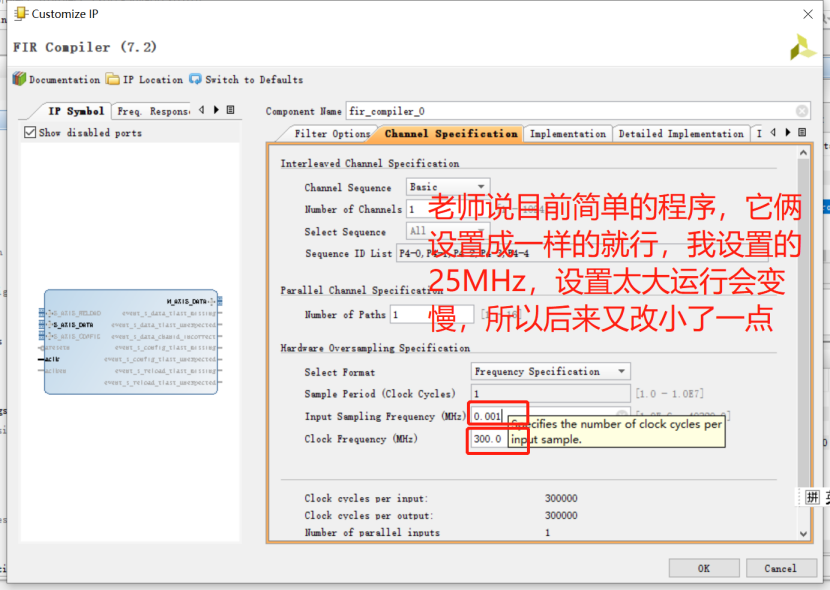

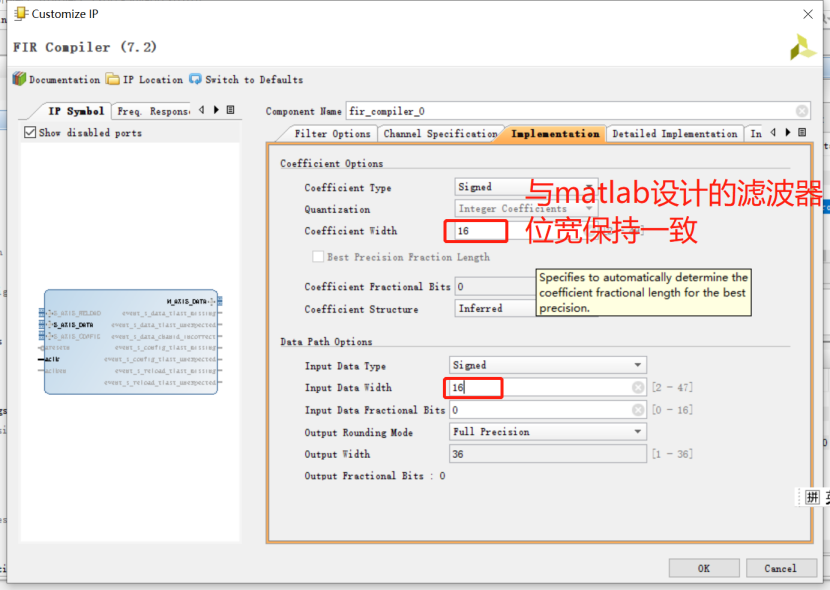

(3)fir滤波器

3.编译与仿真

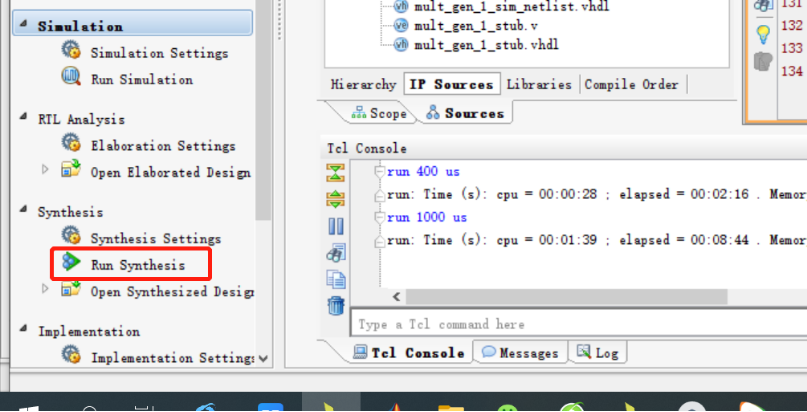

写完程序(随时保存!),点击综合

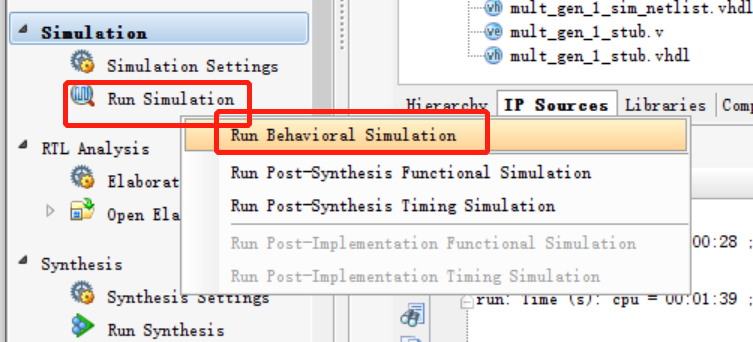

有错误就去它提示的文件里面看,没有错误就点击运行仿真

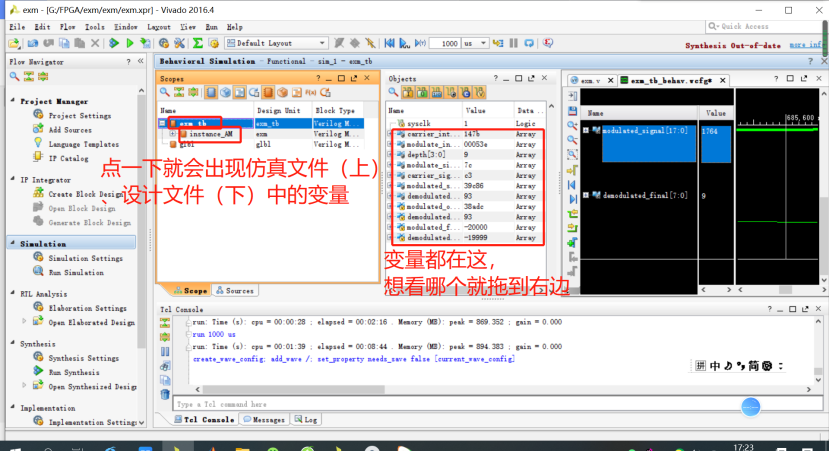

经过漫长的等待后

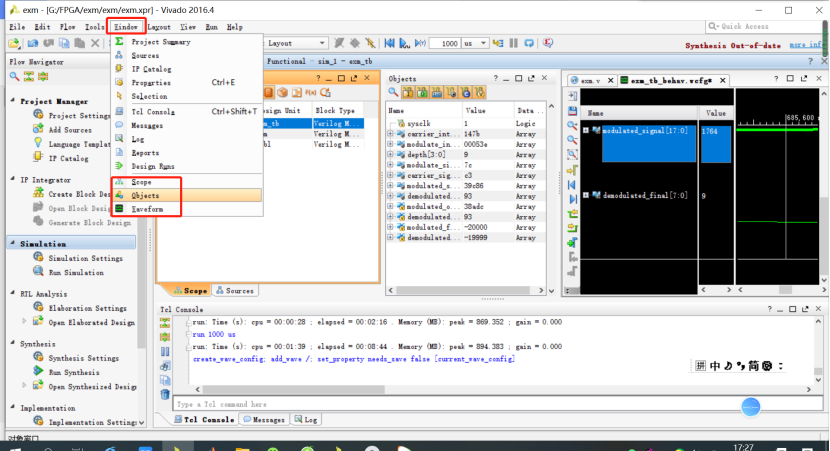

注:我的有好多变量的那个窗口怎么不见了呜呜呜?

你想要的,这里都有~

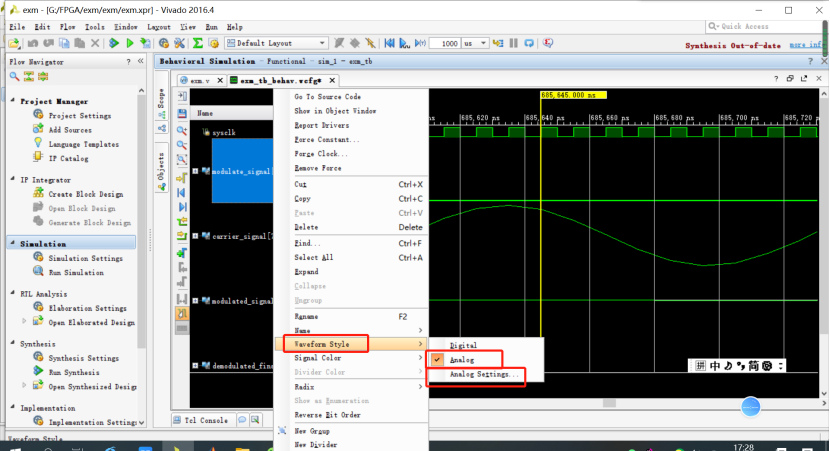

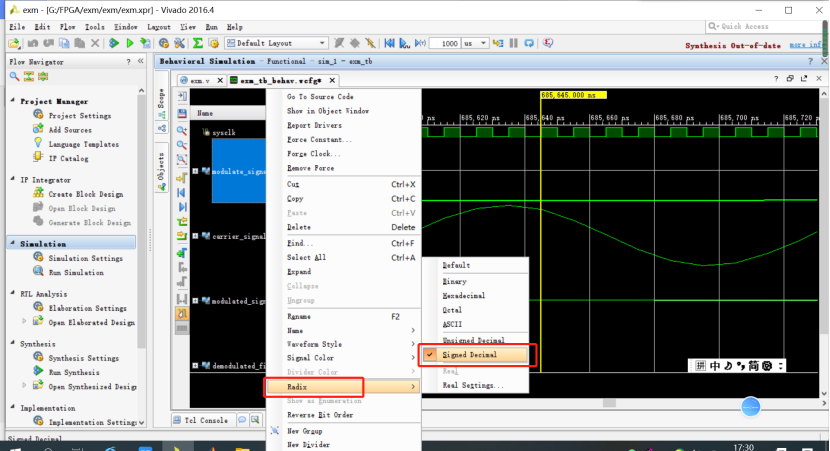

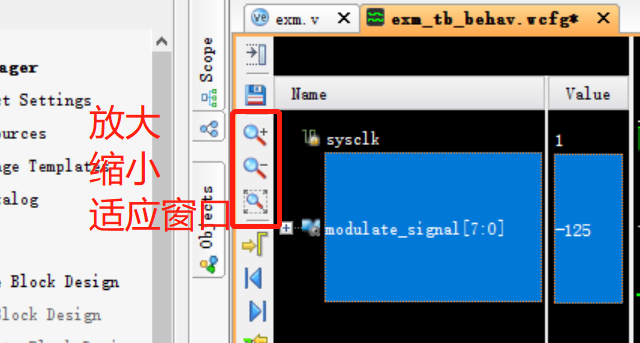

波形改成模拟的

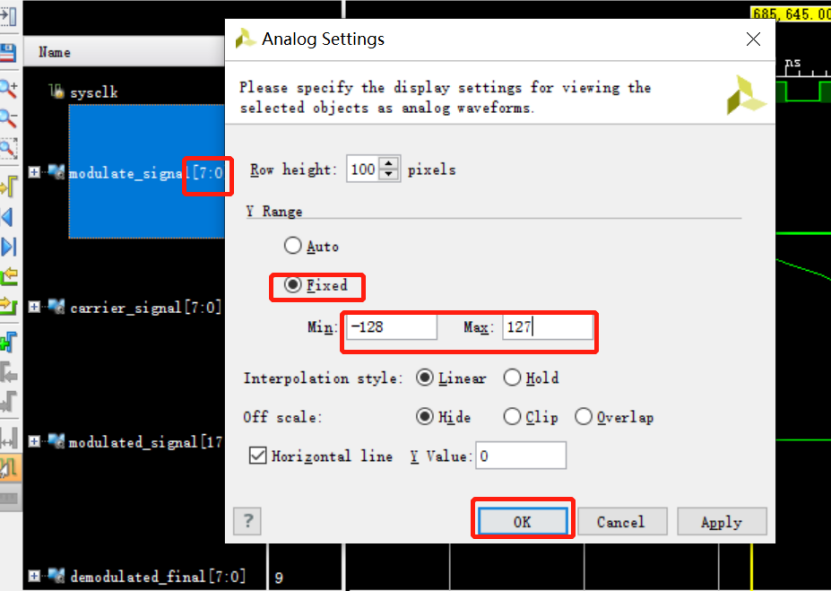

设置范围

如果你观测的变量是有符号数,就设置成有符号数。

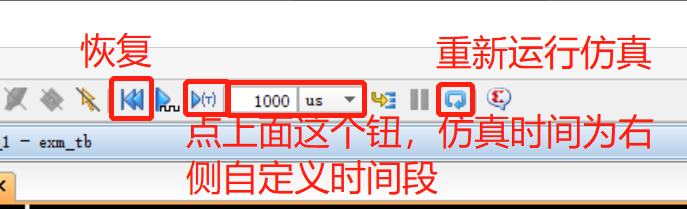

仿真按钮的用法

没了,加油。

最后

以上就是奋斗哈密瓜最近收集整理的关于【FPGA】基于vivado的AM调制与解调(verilog)(三、软件操作篇)1.创建工程,添加设计文件、仿真文件2.调用IP核3.编译与仿真的全部内容,更多相关【FPGA】基于vivado内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复