置位与复位:置位就是将初始状态变为1;复位就是将初始状态变为0.

同步复位原理:同步复位是指只有在时钟沿到来的时候复位信号才起作用。复位信号时间应该持续一个时钟周期才能保证系统稳定。

异步复位原理:与时钟沿无关只要有复位信号到来就执行复位。这时我们需要将复位信号置于always的事件控制括号中。

1.同步复位

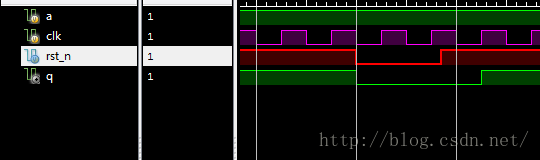

如果我们设置的为上升沿采样数据的话,同步复位只有在上升沿到来时才会产生复位。如图所示:

module RST_Compare(

//input port

clk,rst_n,a,

//output port

q

);

//********************

//input declaration

//********************

input clk;

input rst_n; //active low

input a;

//********************

//output declaration

//********************

output q;

//************************

//wire or reg declaration

//************************

wire clk;

wire rst_n;

wire a;

reg q;

//

//

//logic

//

/

always @(posedge clk)

begin

if(!rst_n)

q<= 1'b0;

else

q<= a;

end

endmodule

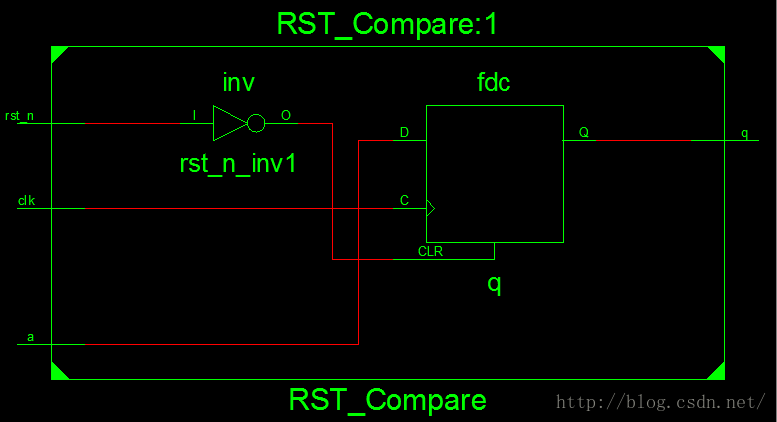

RTL图:

由于Xilinx采用了特殊的处理,综合之后会会比其他软件好。其他软件综合之后如下图

2.异步复位

异步复位只要有复位信号就会立即执行复位动作,不会等到时钟上升沿到来

module RST_Compare(

//input port

clk,rst_n,a,

//output port

q

);

//********************

//input declaration

//********************

input clk;

input rst_n; //active low

input a;

//********************

//output declaration

//********************

output q;

//************************

//wire or reg declaration

//************************

wire clk;

wire rst_n;

wire a;

reg q;

//

//

//logic

//

/

always @(posedge clk or negedge rst_n)

begin

if(!rst_n)

q<= 1'b0;

else

q<= a;

end

endmodule

两者的比较:

同步复位会消耗一定的组合逻辑。这样就消耗比较多的逻辑资源。

异步复位消耗的逻辑比较少一些,但它对复位信号得要求比较高,不能有毛刺,否则会产生亚稳态。

最后

以上就是优雅镜子最近收集整理的关于同步复位与异步复位比较分析的全部内容,更多相关同步复位与异步复位比较分析内容请搜索靠谱客的其他文章。

发表评论 取消回复