一、

总得来说,FALSE PATH就是我们在进行时序分析时,不希望工具进行分析的那些路径。一般不需要工具时序分析的路径指的是异步的路径,异步路径就是指的不同时钟域的路径。

在QuartusII的一个培训文档里面解释了什么时候要用到FALSE PATH:

1. 从逻辑上考虑,与电路正常工作不相关的那些路径,比如测试逻辑,静态或准静态逻辑。

2. 从时序上考虑,我们在综合时不需要分析的那些路径,比如跨越异步时钟域的路径。

二、

芯片接口的三态数据总线实现时在芯片顶层把三态数据总线转为单向的两组总线

三、

同步复位在时钟沿采复位信号,完成复位动作

异步复位不管时钟,只要复位信号满足条件,就完成复位

异步复位对复位信号要求比较高,不能有毛刺

异步复位也需要同步到对应的时钟域,以便后续STA分析

四、多周期路径

多周期路径的约束语法为:

set_multicycle_path <path_multiplier> [-setup|-hold] [-start|-end] [-from <startpoints>] [-to <endpoints>] [-through <pins|cells|nets>]

set_multicycle_path N -setup -from [get_pins data0_reg/C] -to [get_pins data1_reg/D]

set_multicycle_path N-1 -hold -from [get_pins data0_reg/C] -to [get_pins data1_reg/D]

| 参数名称 | 含义 |

|---|---|

| -setup | 表示分析建立时间所需要移动的时钟周期个数 |

| -hold | 表示分析保持时间时,相较于设置了setup后默认的hold check edge,实际hold check edge偏差的时钟周期个数 |

| -start | 表示以目的端时钟作为时钟周期计数基准 |

| -end | 表示以源端时钟作为时钟周期的计数基准 |

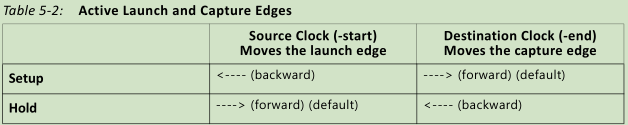

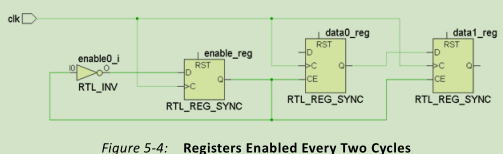

active launch edge和capture edge的移动:

默认的检查规则为:

set_multicycle_path 1 -setup -end -from [get_clocks s_clk] -to [get_clocks d_clk]

set_multicycle_path 0 -hold -start -from [get_clocks s_clk] -to [get_clocks d_clk]

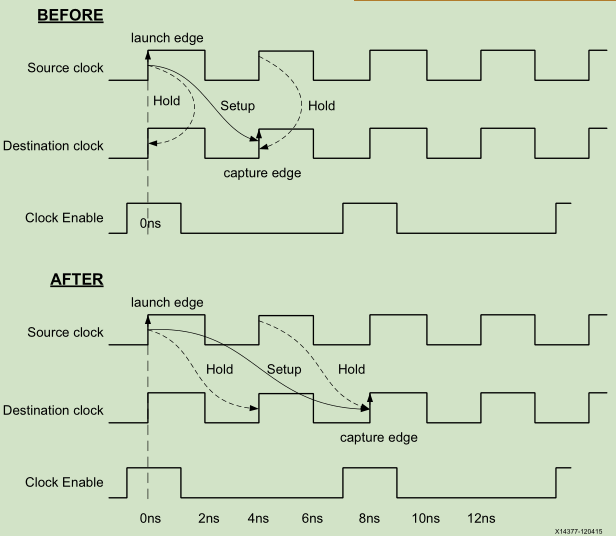

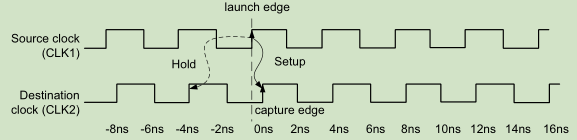

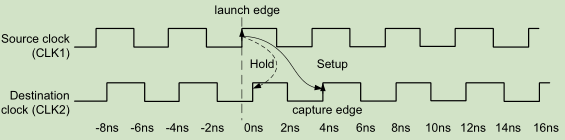

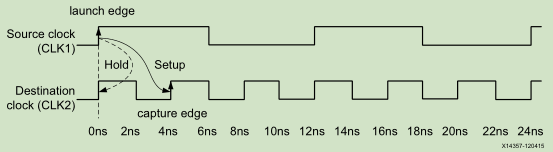

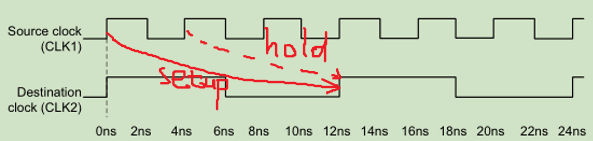

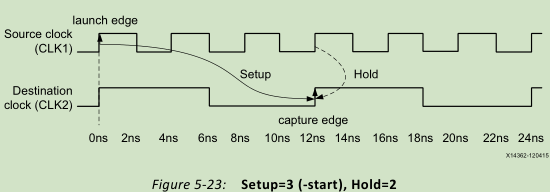

setup和-end搭配使用,hold和-start搭配使用,如图所示:

一旦确定建立时间路径,保持时间路径会自动根据规则做调整。如果保持时间想要回到原来的位置,则需要添加-hold的约束。

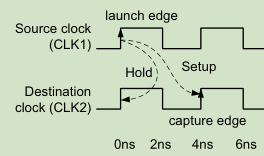

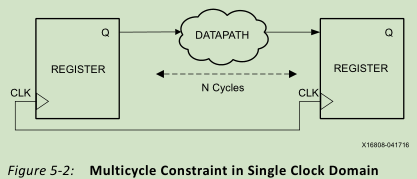

1、同一时钟域的多周期路径

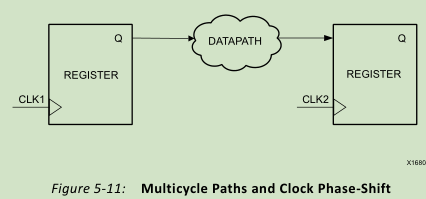

当数据逻辑较为复杂,延时较大时,使得数据无法在一个时钟周期内稳定下来或是需要将数据发送几个周期后才使用。一般会使用时钟使能控制数据捕获,如图所示:

如下图所示显示了每两个周期启用的两个触发器之间的路径。

使用约束:set_multicycle_path 2 -setup -from [get_pins data0_reg/C] -to [get_pins data1_reg/D],表示以目的时钟为基准,往前数,第2个沿作为捕获沿。约束后的时序检查如图所示:

但是此路径不需要再data0_reg中保存一个周期的数据,即更改保持关系在相同的启动和捕获边之间,修改-hold规则命令为:

set_multicycle_path 1 -hold -end -from [get_pins data0_reg/C] -to [get_pins data1_reg/D],表示以目的时钟为基准,相较于默认的hold check edge往后数一个沿作为hold check edge。或者修改命令为:set_multicycle_path 1 -hold -from [get_pins data0_reg/C] -to [get_pins data1_reg/D],表示以源时钟的发射沿为基准,向前数一个沿作为hold check edge,修改后的时序检查为:

对于setup延迟5个周期的情况,约束命令如下:

set_multicycle_path 5 -setup -from [get_pins data0_reg/C] -to [get_pins data1_reg/D]

set_multicycle_path 4 -hold -from [get_pins data0_reg/C] -to [get_pins data1_reg/D]

分别表示以目的时钟为基准,往前数,第5个沿作为捕获沿;以源时钟的发射沿为基准,向前数4个沿作为hold check edge。时序检查如图所示:

约束命令为:set_multicycle_path 5 -setup -from [get_pins data0_reg/C] -to [get_pins data1_reg/D]

set_multicycle_path 4 -hold -end -from [get_pins data0_reg/C] -to [get_pins data1_reg/D]

分别表示以目的时钟为基准,往前数,第5个沿作为捕获沿;以目的时钟为基准,相较于默认的hold check edge往后数4个沿作为hold check edge。时序检查如图所示:

因为源时钟和目的时钟具有相同的波形,并且没有相移,所以上面两个约束方法结果是一样的。

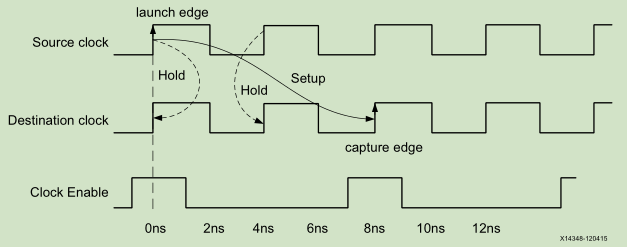

2、相同时钟周期但有相移的多周期路径

对于发送和捕获的两时钟是同周期,但存在相移。有两种情况:clk2较clk1,正相移;clk2较clk1,负相移。

2.1、正相移

假设两个时钟CLK1和CLK2具有相同的波形,但CLK相对CLK1有+0.3ns的相移

时序分析工具通过观察两个波形上的所有边沿和选择发射和捕获时钟上的两个边沿来计算发射关系(setup relationship),从而产生更严格的约束。默认的时序检查如图所示:

由图可知,对于setup的约束是0.3ns,很难时序收敛,而对于hold的检查为-3.7ns,又太宽松了。

添加setup约束:set_multicycle_path 2 -setup -from [get_clocks CLK1] -to [get_clocks CLK2],约束后的时序检查如图所示:

保持检查的约束就按照默认就可以,不用修改。

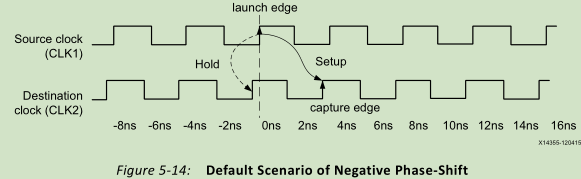

2.2、负相移

在比较小的负相移的情况下,默认时序检查如图下所示,在两个时钟域之间,用于setup和hold检查的发射和捕获边沿类似和单一时钟域,没有相移的很像,不用更改约束。

综上,对于同周期不同相位的两时钟分析,必须要考虑相移方向和相移量。对于负相移,也不是绝对的不用添加约束,如果负相移量太大,实际上就可视为正相移,同样需要添加约束。所以视情况而定。

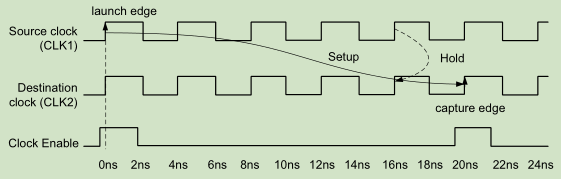

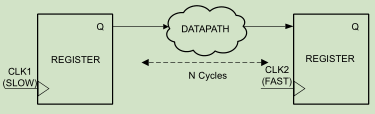

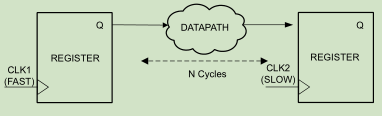

3、从慢时钟到快时钟多周期路径

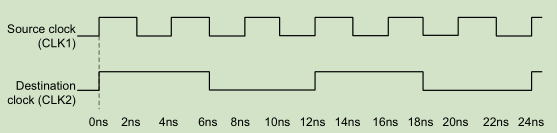

发射时钟比接收时钟更慢,如下所示:

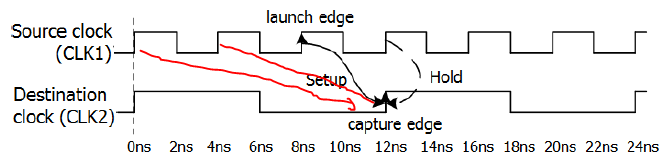

假设CLK2频率是CLK1的三倍,接收寄存器需要一个时钟使能信号才能将数据正确捕获数据,默认的时序检查如下图所示:

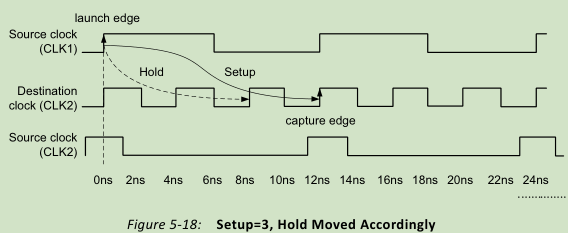

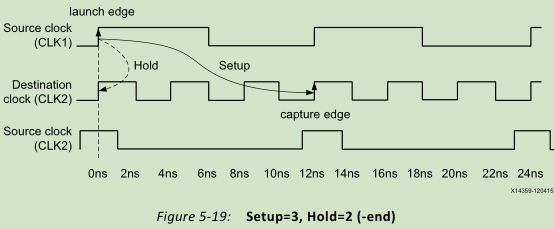

将setup检查推迟三个周期,修改约束为:set_multicycle_path 3 -setup -from [get_clocks CLK1] -to [get_clocks CLK2],时序检查如图所示:

不需要再发射寄存器中保存CLK2的一个周期的数据,这样会增加不必要的逻辑,从而增加面积和消耗电能。因为接收寄存器有一个时钟使能信号,所以放松hold的要求没有亚稳态的风险。修改hold的约束:set_multicycle_path 2 -hold -end -from [get_clocks CLK1] -to [get_clocks CLK2],修改后时序检查如图所示:

如果在使用set_multicycle_path -hold时没有指定-end,那么将沿着源时钟的发射沿将向前移,这将不能满足时序需求。所以此时的-hold一定要添加-end。

综上所述,从慢时钟到快时钟的情况,一般约束如下:

set_multicycle_path N -setup -from [get_pins data0_reg/C] -to [get_pins data1_reg/D]

set_multicycle_path N-1 -hold -end -from [get_pins data0_reg/C] -to [get_pins data1_reg/D]

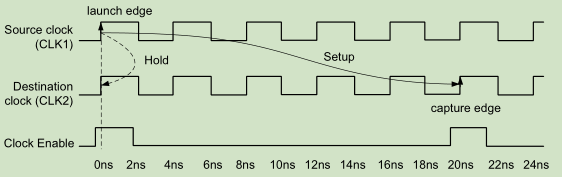

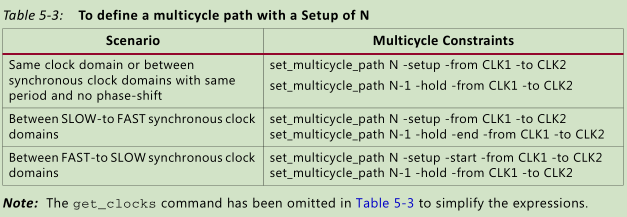

4、从快时钟到慢时钟多周期路径

发射时钟比接收时钟更快,即CLK1比CLK2快,如下图所示:

假设CLK1频率是CLK2的三倍,如下图所示:

原本默认检查规则,满足setup检查的有3条路径(有两条是红线补充),因为最终时序报告只会给出最苛刻的一条,所以只保留黑色这条setup路径。

修改setup约束条件:set_multicycle_path 3 -setup -start -from [get_clocks CLK1] -to [get_clocks CLK2],将setup检查时钟沿着源时钟往后移动N-1即2个周期,约束后的时序检查如图所示的:

再添加hold的约束条件:set_multicycle_path 2 -hold -from [get_clocks CLK1] -to [get_clocks CLK2],将上图中hold的检查边沿沿源时钟往前移动2个时钟周期,约束后的时序检查如图所示:

综上所述,从快时钟到慢时钟的情况,一般约束如下:

set_multicycle_path N -setup -start -from [get_clocks CLK1] -to [get_clocks CLK2]

set_multicycle_path N-1 -hold -from [get_clocks CLK1] -to [get_clocks CLK2]

总结:

参考:https://www.cnblogs.com/rouwawa/p/12491951.html

xilinx手册ug903

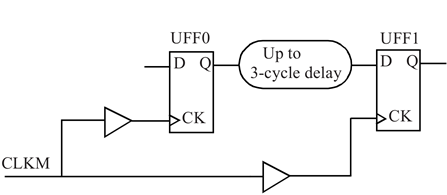

If the data path takes up to three clock cycles, see the circuit below, please specify the multicycle constrains using SDC command. Note that hold check need to stay as it was in a single cycle setup case.

set_muiticycle_path 3 -setup -from [get pins UFF0/Q] -to [get_pins UFF1/D]

set_muiticycle_path 2 -hold -from [get pins UFF0/Q] -to [get_pins UFF1/D]

五、时序裕度

同步电路设计中,逻辑电路的时序模型如下

T1为触发器的时钟端到数据输出端的延时,T2和T4为连线延时,T3为组合逻辑延时,T5为时钟网络延时。1)假设时钟clk的周期为Tcycle;2)假设Tsetup、Thold分别为触发器的setup time和hold time。那么为了保证数据正确采样(该路径为非multi-cycle路径),下面等式是否正确?如果不正确该如何修改?

T1 + T2 + T3 + T4 + T5 < Tcycle – Tsetup

T1 + T2 + T3 + T4 > Thold

一般来说:Tscrclk + Tcko + Tdata + SetupSlack + Tsu = Tdestclk + T;要保证 SetupSlack > 0,即 SetupSlack > Tdestclk + T - Tscrclk - Tcko - Tdata - Tsu;

Tdestclk + Thd + HoldSlack = Tscrclk + Tcko + Tdata;要保证 HoldSlack > 0,即 HoldSlack > Tscrclk + Tcko + Tdata - Tdestclk - Thd

本题中:Tdestclk - Tscrclk = T5,Tcko = T1,Tdata = T2 + T3 + T4;

所以:T + T5 - T1 - T2 - T3 - T4 - Tsutup > 0,即 T1 + T2 + T3 + T4 - T5 < Tcycle – Tsetup

T2 + T3 + T4 - T1 - Thold > 0,即 T1 + T2 + T3 + T4 - T5 > Thold

最后

以上就是善良日记本最近收集整理的关于寒武纪IC2的全部内容,更多相关寒武纪IC2内容请搜索靠谱客的其他文章。

发表评论 取消回复