一、基本原理

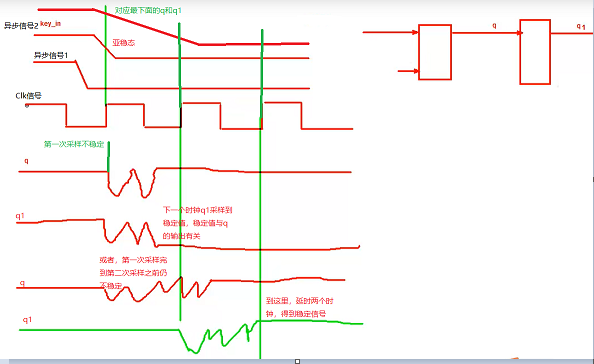

1、时钟信号只在上升沿起作用,异步信号输入时会有个亚稳态(抖动)的过程。

2、时钟信号采样会出现两种情况:异步信号1和异步信号2。对于异步信号1,时钟能够采样到稳定信号,没有任何影响;但是,我们不能确定每次都是刚好采样到稳定时候,例如异步信号2。

3、因此要对异步信号进行处理,通常的做法是:将异步信号连接2级寄存器q和q1,进行两个周期的时延,以获得稳定信号。

4、2级寄存器的输出是个稳定的值(可能是0或1)。

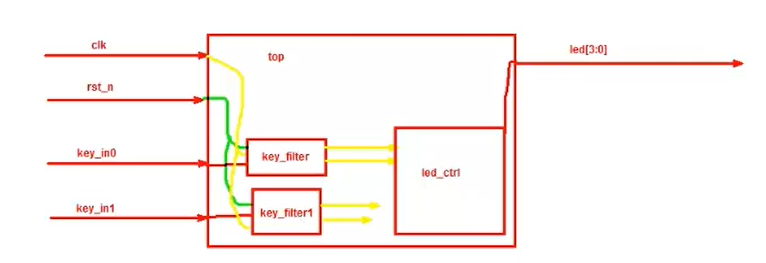

二、对FPGA(八)中key_in进行优化。

与(八)中的边沿检测,代码相同,意义不同。

//通过2级寄存器,消除异步信号的亚稳态

always@(posedge Clk or negedge Rst_n)

if(!Rst_n)begin

key_in_a0 <= 1’b0;

key_in_a1 <= 1’b0;

end

else begin

key_in_a0 <= key_in;

key_in_a1 <= key_in_a0;

end

注意:

1、由于用key_in_a0 和key_in_a1 进行表示,因此在RTL viewer中不能明显看出2级寄存器。改成key_in_sa和key_in_sb就能看到。

2、由于2级寄存器进行亚稳态处理,2级寄存器进行边沿检测,也就是输入的信号经过四个时钟周期之后才输出,对于按键来说没什么影响。但如果系统时钟是100Mhz(周期10ns),输入信号小于25Mhz(周期40ns)那么就会出现:当输入信号是第1个时钟(第0ns)的值时,经过4个系统时钟延时,来到了第40ns,这时下一个输入信号来临,同时第一个信号进行输出。结果我们看到的就是下一时刻的输入对应上一时刻的输出。如何解决?

3、除了提到的寄存器时延造成这种问题之外,当输入信号的时钟大于系统时钟的时候:比如一个系统时钟内,有2个信号周期的来临,但是就只能采样到一个。

三、控制led

**实验现象:**每次按下按键0,4个led灯以二进制格式加1,每次按下按键1,4个led灯以二进制格式减1。

最后

以上就是坚强身影最近收集整理的关于FPGA(九)---异步信号亚稳态处理的全部内容,更多相关FPGA(九)---异步信号亚稳态处理内容请搜索靠谱客的其他文章。

发表评论 取消回复