数字IC设计——跨时钟域篇1

一、时钟域概要

1. CDC介绍

CDC(clock domain crossing)检查(跨时钟域的检查)是对电路设计中同步电路设计的检查。非同步时钟没有固定的相位关系,这样Setup/Hold不满足而产生了亚稳态是无法避免的。我们采用同步设计的方法保证亚稳态不会无序的在电路中传播,从而导致功能问题。

随着当今SOC设计的规模越来越大,时钟越来越多,工作模式越来越复杂。跨时钟域电路不但多,而且非常复杂。 在当今的电路设计中我们通常使用多级同步,异步FIFO,握手等同步设计来保证亚稳态信号不会在电路中无序的传播。

但同步设计中,同步处理不当依然会出现glitch、多路扇出等问题导致电路实际运行出现故障。

目前我们的数字设计大部分是基于RTL设计的,直接通过RTL检查"跨时钟域的同步设计" 很难做到100%覆盖的检查,特别是当今SOC中集成大量IP,直接通过RTL检查几乎不可能的。 电路设计中同步电路设计的检查都是使用专门的EDA工具做静态的CDC检查。

常用的CDC检查工具有Conformal CDC 和 Spyglass CDC。

此外CDC检查也是前端sign off 重要项目和数字IC设计工程师的必备的技能。

二、 时钟介绍

-

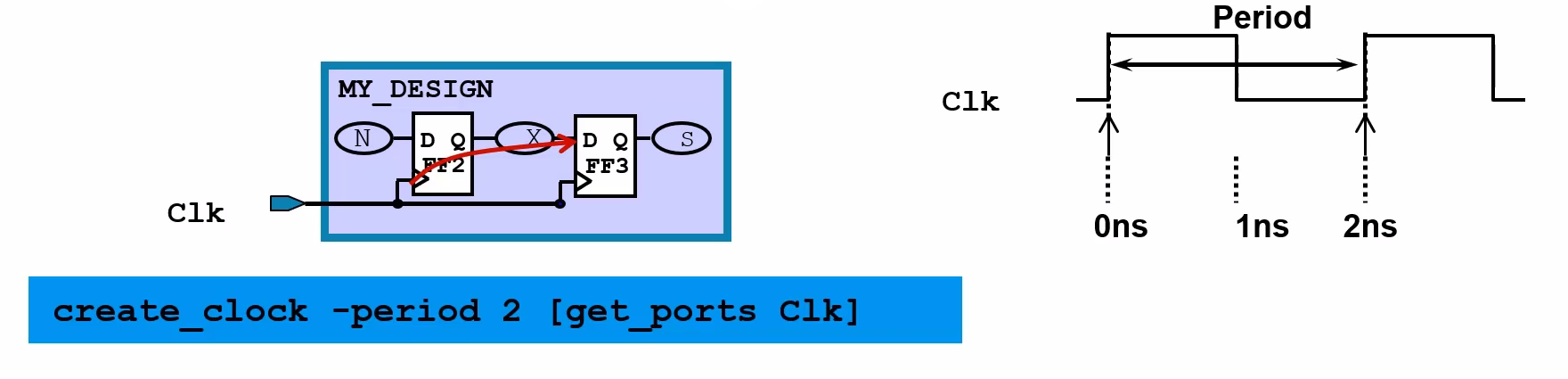

时钟属性

时钟信号是一个按一定电压幅度,一定时间间隔连续发出的脉冲信号。

脉冲信号之间的时间间隔称为周期;

单位时间(如1秒)内所产生的脉冲个数称为频率。频率的标准计量单位是Hz(赫)。数字芯片中众多的晶体管工作在开关状态,它们的导通和关断动作无不是按照时钟信号的节奏进行的。

-

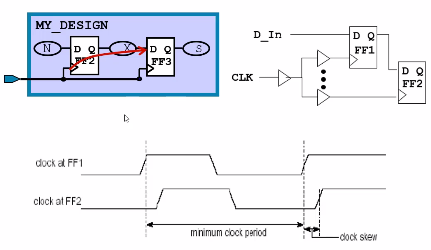

时钟偏斜(Skew)

时钟偏斜指的是同一个时钟信号到达两个不同寄存器之间的时间差值,skew的定义就是最长路径与最短路径差值。

-

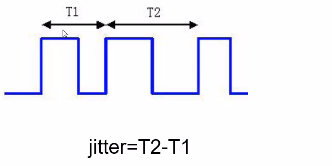

时钟抖动(jitter)

抖动,即指两个时钟周期之间存在的差值,这个误差是在时钟发生器内部产生的,和晶振或者PLL内部电路有关系

刻画时钟偏斜和时钟抖动,即时钟的不确定性:

set_clock_uncertainty Tu [get_clock CLK]

其中,Tu即为时钟偏斜和抖动的和值。通过后端工程师与PLL相关值来确定。

三、 时钟源

-

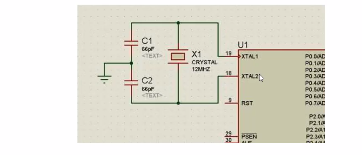

数字电路里一般用晶振提供基本的时钟信号。

从一块二氧化硅晶体上按一定的方位角切下薄片(称为“晶片”),在晶片的两个表面上涂覆一层薄薄的银层后接上一对金属板,焊接引脚,并用金属外壳封装,就构成了石英晶体振荡器(OSC)——基于压电效应。

-

有些芯片的一部分时钟来自于其他芯片。它的时钟源就是外部芯片的输出信号。如SPI,I2C接口就来自外部芯片。

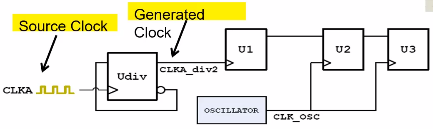

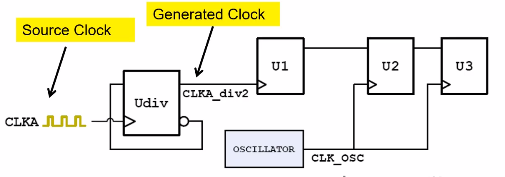

一个时钟源的例子:

电路中有存在其他模块的时钟源CLKA与振荡器CLK_OSC两个时钟源。

四、 同步时钟

-

同步时钟:

a.同源,比如分频电路

b.有固定的相位关系

-

不同步时钟:

如果C1与C2来自不同的晶振,那么就是不同步的时钟 -

ASIC中时钟结构

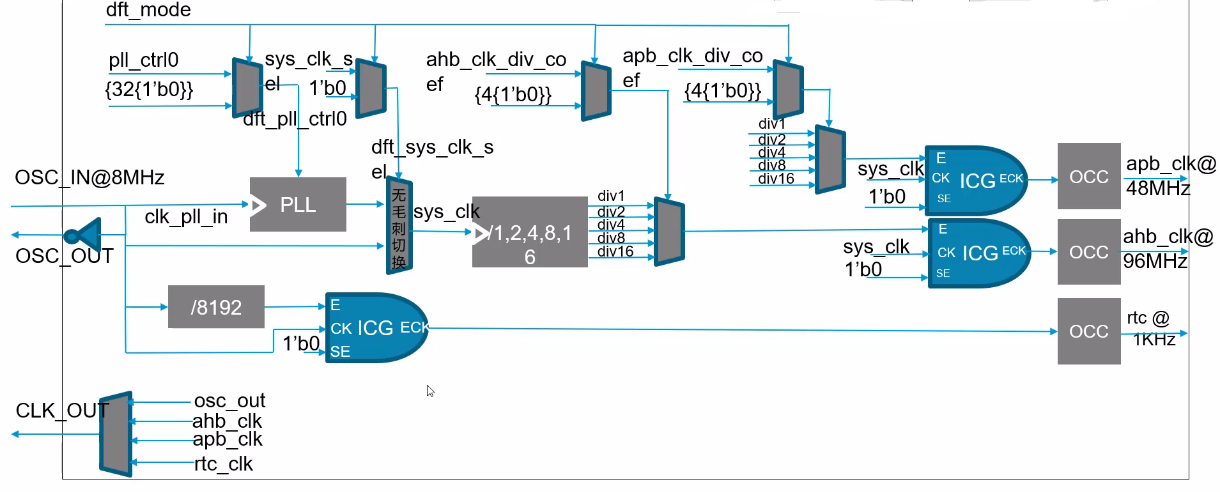

MCU内部时钟结构图:

图中一个8MHz的时钟源OSC_IN经过PLL倍频之后,由无毛刺的MUX选择器选择时钟,在经由分频器,分频出一系列频点的时钟,最后经过ICG门控开关,由OCC(on chip controller)来控制选择那一路时钟,分配test模式和function模式。

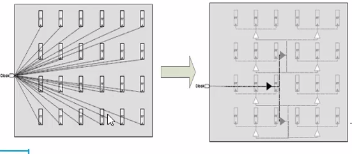

CTS(clock tree synthesize)

ASIC设计时,时钟分布是一个网状结构,为了能够达到时钟到达每个寄存器的路径误差不大,可以利用CTS来确保源头的时钟到达各寄存器延迟差不多。

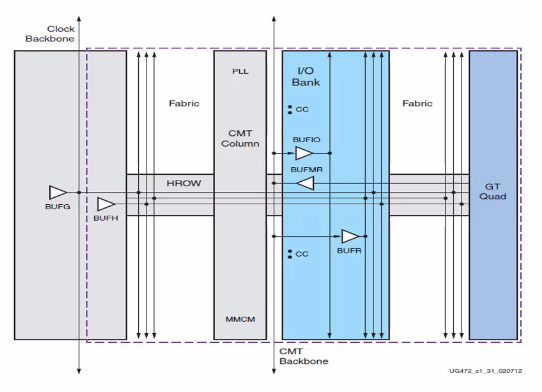

- FPGA中时钟结构

FPGA中的时钟和ASIC时钟结构基本相似。在ASIC中,定制化的通过后端的工具插入clock tree以及其他功能。但是在FPGA中,这些驱动和链接资源已经是做好的,只能利用这些,用这些功能来完成时钟的分配。

以Xilinx 7系列的时钟为例:

- MMCM(Mixed-Mode Clock Manager)混合模式时钟管理器

- High-Performance Clock

- BUFG(全局时钟缓冲器):驱动FPGA全局时钟驱动

- BUFH(horizontal clock buffers横向Bank时钟缓冲器):局部时钟区域驱动

- BUGR (纵向Bank时钟缓冲器):局部区域时钟驱动

- BUFMR (multi-clock region buffers):驱动多个时钟域

- BUFIO (用于IO输出缓冲):BUFH和BUFR也可以驱动BUFIO

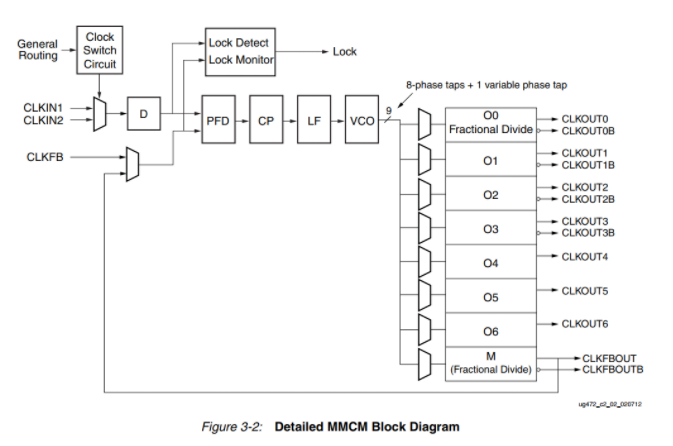

MMCM结构图:

在实际设计中,需要充分考虑有多少时钟资源。来驱动相关的逻辑电路

对于ASIC设计,如何将其设计转到FPGA中:

ASIC设计中有很多同源时钟,但是很多均跨越多个时钟域,但是考虑布局布线,我们将这些同源时钟关系做一些异步处理。代价是增加面积来获取快的开发时间。

或者直接利用MMCM产生ASIC设计中所需的时钟,在通过添加BUFG。

五、 异步时钟

异步时钟

1.不同源

2.没有固定的相位关系

CLKA与CLKA_div2是同步时钟

CLKA与CLK_OSC是异步时钟

考虑两种情况:

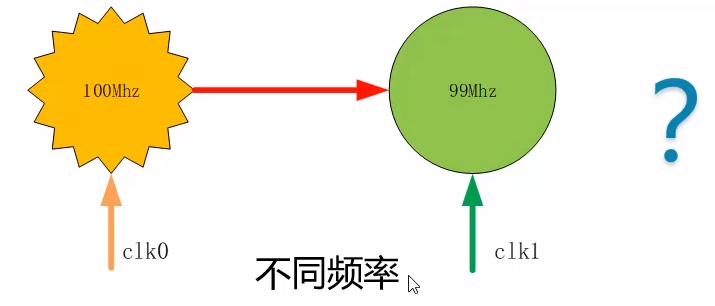

- 对于不同频率的时钟如100M,99M的两个时钟,不一定为异步时钟,即如果来自同一个源,那么即为同步时钟

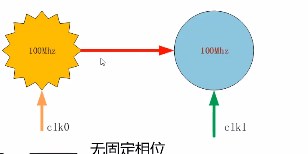

- 如果频率相同,没有固定的相位关系。是否为不同时钟,答案也不一定是同步时钟。如果相位不同,即使频率相同,仍然是异步时钟。

六、时钟域

时钟域(Clock Domain) 以捕获时钟划分时钟域

-

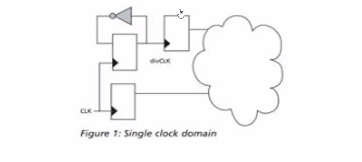

单时钟域:数据发送和接收是同一个时钟

-

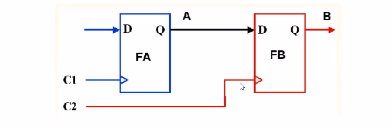

多时钟域:数据发送和接收不是同一个时钟

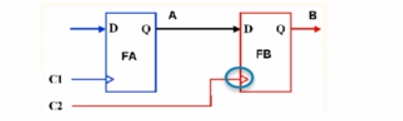

对于改电路,以FB捕获C2时钟为该电路时钟。注意capture时钟和launch时钟的相对定义

七、跨时钟域问题

-

跨时钟域

若一个电路launch时钟和capture时钟不是同一个时钟,就是跨时钟域电路若两个时钟是同步时钟就是同步时钟域

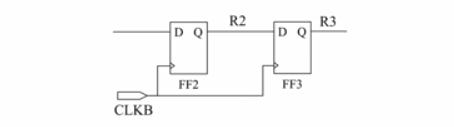

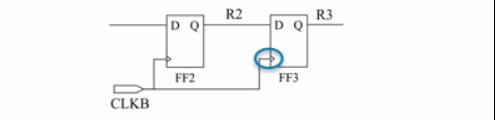

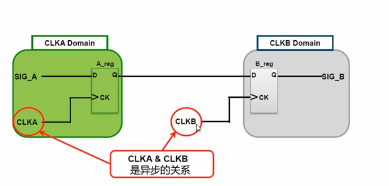

若两个时钟是异步时钟就是异步时钟域例子:

lanch时钟为CLKA,capture时钟为CLKB,该电路为典型的跨时钟域的例子。

跨时钟例子:

单个模块:UART, USB等 -

跨时钟域问题

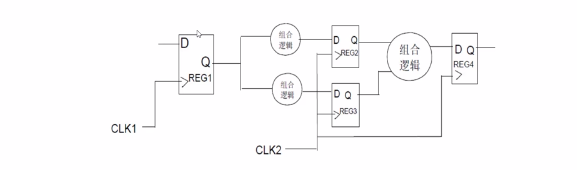

CLK1与CLK2来自不同时钟源,由于时钟源不同,对于REG2和REG3来说,在同一时刻,一个认为REG1的输出是1,另一个认为是0,这将会导致电路判断出现错误,即亚稳态问题。

最后

以上就是传统星星最近收集整理的关于数字IC设计——跨时钟域篇1(时钟域)的全部内容,更多相关数字IC设计——跨时钟域篇1(时钟域)内容请搜索靠谱客的其他文章。

发表评论 取消回复