同步FIFO设计

1.功能定义:

用16*8 RAM实现一个同步先进先出(FIFO)队列设计。由写使能端控制该数据流的写入FIFO,并由读使能控制FIFO中数据的读出。写入和读出的操作由时钟的上升沿触发。当FIFO的数据满和空的时候分别设置相应的高电平加以指示。

2.顶层信号定义:

信号名称 I/O 功能描述 源/目标 备注

Rst In 全局复位(低有效) 管脚

Clk In 全局时钟 管脚 频率10Mhz;

占空比:50%

Wr_en In 写使能 管脚 高有效

Rd_en In 读使能 管脚 高有效

Data_in[7:0]

In 数据输入端 管脚

Data_out[7:0] Out 数据输出端 管脚

Empty Out 空指示信号 管脚 高有效

Full Out 满指示信号 管脚 高有效

3.顶层模块划分及功能实现

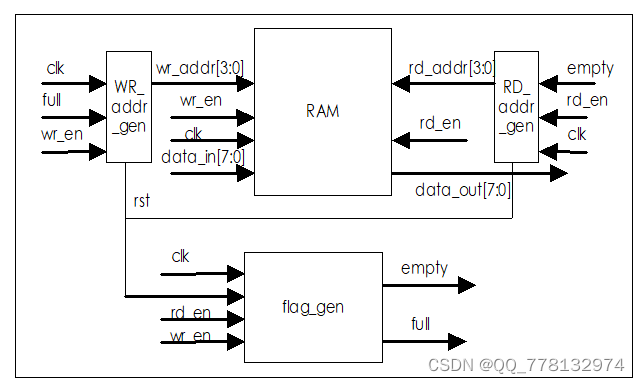

该同步fifo可划分为如下四个模块,如图1所示:

①存储器模块(RAM) ——用于存放及输出数据;

②读地址模块(rd_addr) ——用于读地址的产生;

③写地址模块(wr_addr)——用于写地址的产生

④标志模块(flag_gen) ---- 用于产生FIFO当前空满状态。

1)RAM模块

本设计中的FIFO采用采用16*8双口RAM,以循环读写的方式实现;

根据rd_addr_gen模块产生的读地址&#x

最后

以上就是干净帅哥最近收集整理的关于同步FIFO设计verilog设计及仿真的全部内容,更多相关同步FIFO设计verilog设计及仿真内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复