实验要求:

做一个4选1的mux,并且进行波形仿真 和2选1的mux对比,观察资源消耗的变化

一、4选1数据选择器

4选1数据选择器代码用case语句实现:

module mux4_to_1(

d0,

d1,

d2,

d3,

a0,

a1,

out

);

parameter WL = 16;

input [WL-1:0] d0,d1,d2,d3;

input a0,a1;

output [WL-1:0] out;

reg out;

always @(d0 or d1 or d2 or d3 or a0 or a1)

begin

case({a0,a1})

2'b00: out = d0;

2'b01: out = d1;

2'b10: out = d2;

2'b11: out = d3;

default: out = 1'bx;

endcase

end

endmodule

在case语句中,根据a0和a1的不同值来确定输出信号

当a1a0均为0时,输出out为d0

以此类推

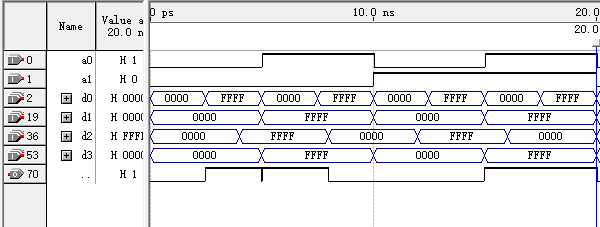

4选1数据选择器功能仿真波形图

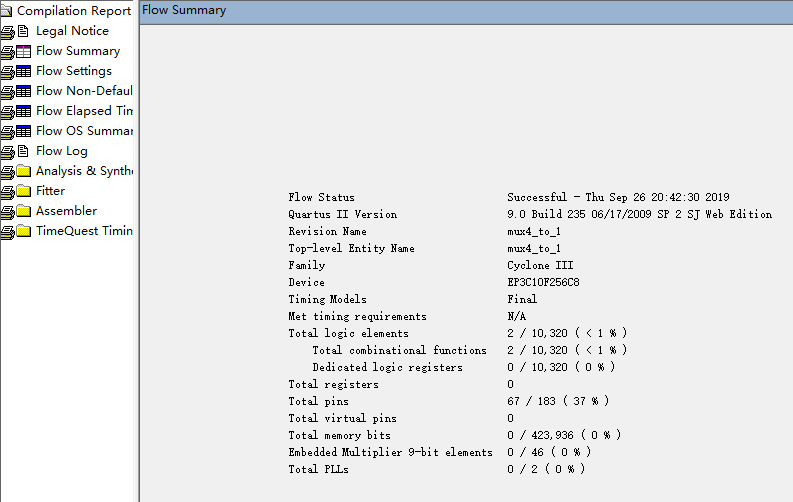

4选1资源消耗图

二、2选1数据选择器

// module mux2_to_1, 选择器的代码,

module mux2_to_1(

IN0 , // input 1

IN1 , // input 2

SEL , // select

OUT ); // out data

parameter WL = 16; // 输入输出数据信号位宽

input [WL-1:0] IN0, IN1;// 选择器的两个输入数据信号

input SEL; // 通道选通的控制信号

output[WL-1:0] OUT; // 选择器的输出数据信号

reg [WL-1:0] OUT;

// 生成组合逻辑的代码

always @ (IN0 or IN1 or SEL) begin

if(SEL) // SEL为1 选择输入1

OUT = IN1;

else // SEL为0 选择输入0

OUT = IN0;

end

endmodule

// endmodule mux2_to_1

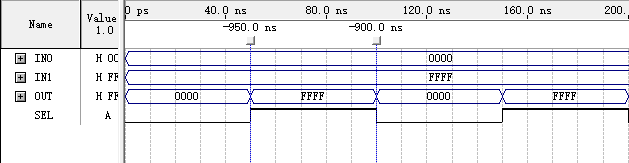

2选1数据选择器功能仿真波形图

2选1数据选择器资源消耗变化如下:

发表评论 取消回复