数字IC设计学习笔记

同步电路,异步电路,同步复位,异步复位

1. 同步电路,异步电路

2. 同步复位,异步复位

2.1 同步复位与异步复位的对比

2.2. 同步复位代码与结构

2.3. 异步复位代码与结构

2.4. 异步复位同步释放代码与结构

1. 同步电路,异步电路

- 同步电路与异步电路的主要区别在于电路的触发是否与驱动时钟同步;

- 从行为角度:所有电路是不是在时钟的有效边沿之下同步处理数据;

| 同步电路 | 异步电路 | |

|---|---|---|

| 时钟个数 | 只有一个 | 可为多个 |

| 时钟类型 | 同源同相 | 1. 不同源;2. 同源不同相 |

| 竞争冒险 | 无 | 有 |

| 设计耦合 | 完全耦合,不利于面积和功耗优化 | 不耦合,设计灵活 |

| 综合/分析 | 简单 | 复杂 |

2. 同步复位,异步复位

- 2.1 同步复位与异步复位的对比

| 同步复位 | 异步复位 | |

|---|---|---|

| 特点 | 复位信号只在时钟有效沿到来时才有效。(来自对DFF-D端的组合逻辑设置) | 无论时钟有效沿是否到来,只要复位信号有效,就复位。(来自对DFF的设置) |

| Verilog | always@(posedge clk) | always@(posedge clk or negedge rst) |

| 优点 | 1. 有利于仿真器仿真 2. 能够滤除高于时钟频率的毛刺 3. 若为完全同步时序电路,则有利于时序分析. | 1. 设计简单 2. 节省资源(部分器件库有异步DFF) 3. 异步信号标识方便,利于使用FPGA的全局复位端口GSR |

| 缺点 | 1. 复位信号的有效时长必须大于时钟周期,否则无法识别,完成复位 2. 考虑组合逻辑延时,复位延时skew的问题 3. 积存的数据输入需要插入组合逻辑,消耗逻辑资源 | 1. 异步信号易受毛刺影响 2. 易产生亚稳态(复位信号释放时正好在时钟信号有效沿附近) |

| 总结 | 推荐使用异步复位,同步释放 |

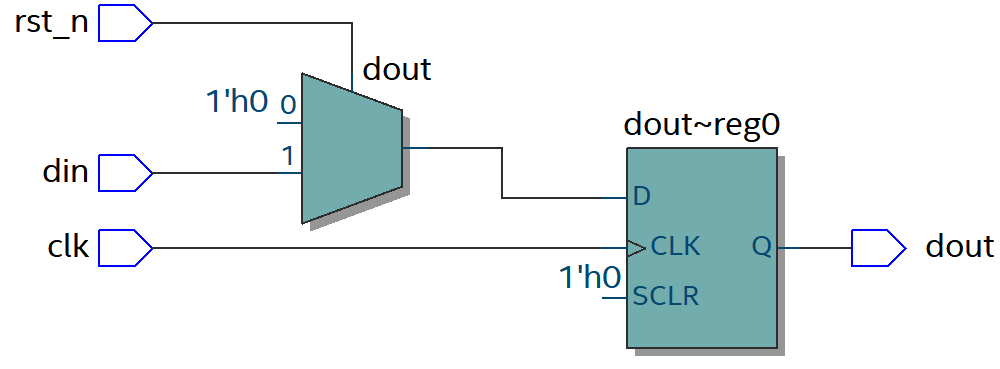

- 2.2 同步复位代码与结构

module dff_syn(

input clk,

input rst_n,

input din,

output reg dout

);

always@(posedge clk)

if(!rst_n)

dout <= 1'b0;

else

dout <= din;

endmodule

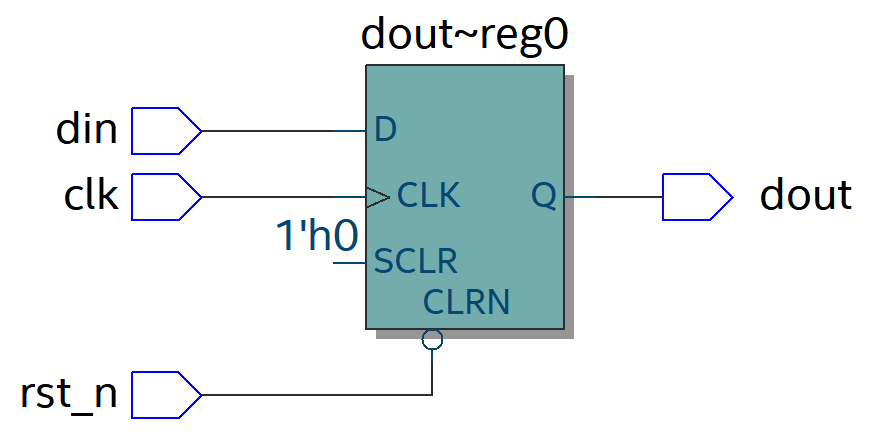

- 2.3 异步复位代码与结构

module dff_asyn(

input clk,

input rst_n,

input din,

output reg dout

);

always@(posedge clk or negedge rst_n)

if(!rst_n)

dout <= 1'b0;

else

dout <= din;

endmodule

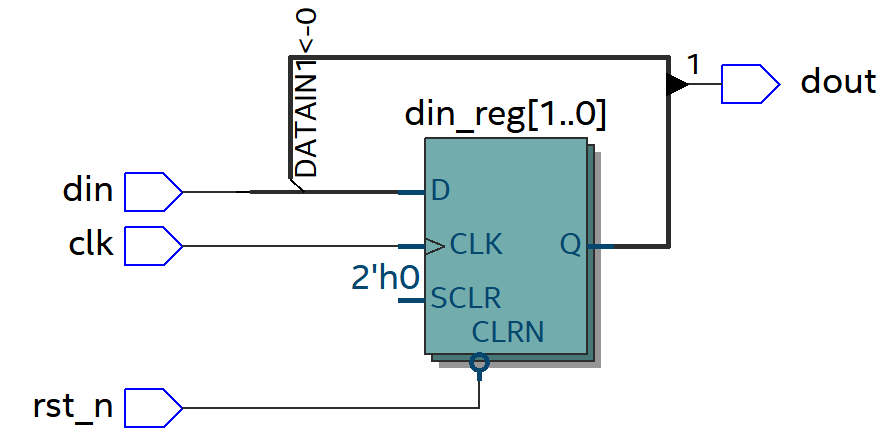

- 2.4 异步复位同步释放代码与结构

module asyn_dff_syn(

input clk,

input rst_n,

input din,

output wire dout

);

reg din_reg0;

reg din_reg1;

always@(posedge clk or negedge rst_n)

if(!rst_n)begin

din_reg0 <= 1'b0;

din_reg1 <= 1'b0;

end

else begin

din_reg0 <= din;

din_reg1 <= din_reg0;

end

assign dout = din_reg1;

endmodule

【注】:个人学习笔记,如有错误,望不吝赐教,这厢有礼了~~~

最后

以上就是如意电脑最近收集整理的关于数字IC设计学习笔记_ 同步电路,异步电路,同步复位,异步复位数字IC设计学习笔记的全部内容,更多相关数字IC设计学习笔记_内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复