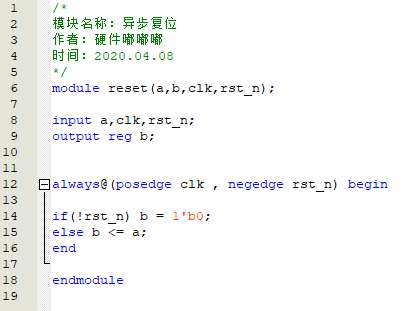

异步复位:

它是指无论时钟沿是否到来,只要复位信号有效,就对系统进行复位。

always@(posedge clk or negedge Rst_n) begin

if(!Rst_n)

…

end

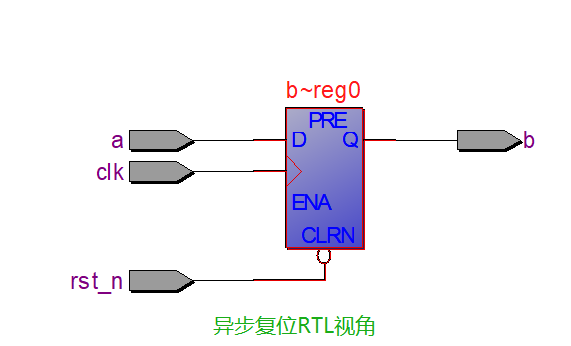

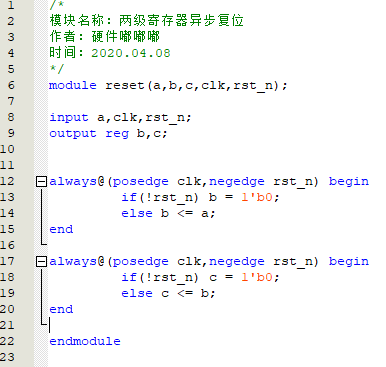

异步复位实例:

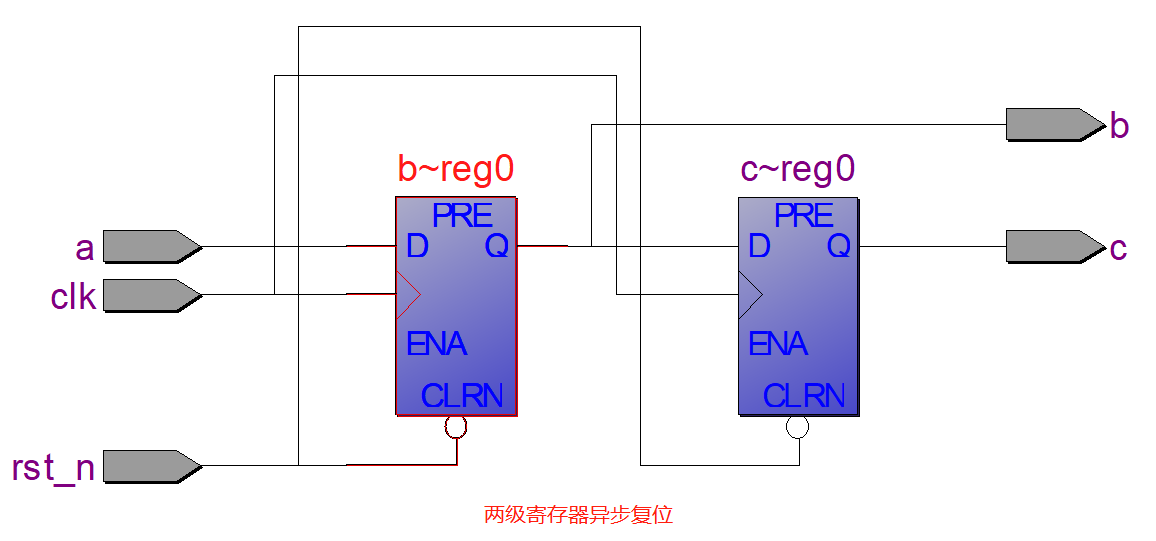

综合后查看RTL视角,可以看出寄存器都会有一个异步清零端(CLRN),在异步复位的设计中,这个端口一般接低电平有效的复位信号rst_n,即使设计中的是高电平,实际综合后也会把异步复位信号反向后接到这个CLRN端。

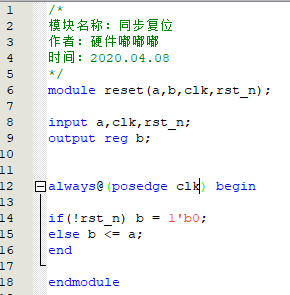

同步复位:

顾名思义,同步复位是指复位信号只有在时钟上升沿到来时,才能有效,否则无法完成对系统的复位工作。

always@(posedge clk) begin

if(!Rst_n)

…

end

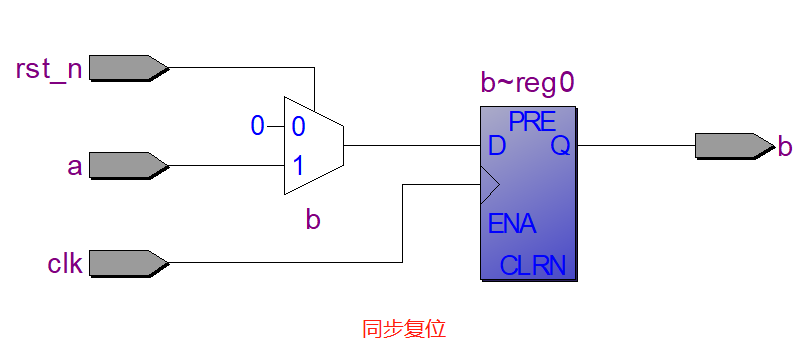

同步复位实例:

综合后查看RTL视角,和异步复位相比,同步复位没有用到寄存器的CLRN清零端,综合出来的实际电路是把复位信号rst_n作为输入逻辑的使能信号,那么同步复位势必导致额外增加FPGA内部的资源消耗。

这样一看似乎采用异步复位更具有优势,因为FPGA寄存器本身支持异步复位专用端口,无需增加器件的额外资源。

两级寄存器的异步复位

但实际上,我们将从两级寄存器的异步复位来分析异步复位的缺陷,并推论在一个大的项目中众多寄存器同时出现又会是怎样的?

下图是综合后的RTL视图逻辑电路。从代码中可以看出,正常情况下,在clk的上升沿将c值更新为b,b更新为a,一旦出现复位rst_n信号,b,c都清零。

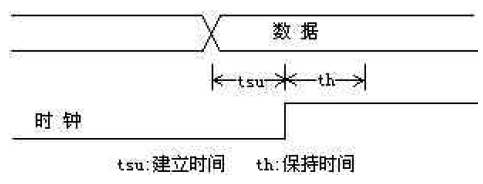

但是我们并不能确定复位信号rst_n会在什么时候结束,如果是结束于breg0和creg0的{tsu+th:建立时间+保持时间}之外的,那么一切都会正常运行,但如果不是,将会出现什么情况呢?

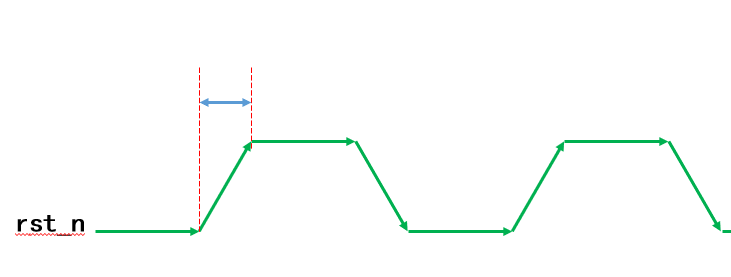

复位信号rst_n的撤销(由低电平变为高电平)出现在建立时间和保持时间内,此时clk检测到rst_n的状态就会是一个亚稳态(不确定是0还是1)。

由于此时rst_n的不确定性,可能会出现4种情况,即breg0和creg0都复位或者都跳出复位,再或者一个复位另一个跳出复位,那么后者将会造成系统工作不同步的问题,可想而知,如果在一个大的项目中,异步信号随机变化将会给系统运行带来隐患。

上述两级寄存器异步复位实例描述的是在异步复位信号和系统时钟信号之间存在着异步时钟域的亚稳态问题,同步复位也仅仅可以降低这种亚稳态出现的概率,并不能完全避免,同步复位的缺点是在于需要更多的器件资源,无法充分利用寄存器专用的复位端口CLRN。

因此多数推荐使用异步复位,同步释放的方式来解决亚稳态时钟域的问题。

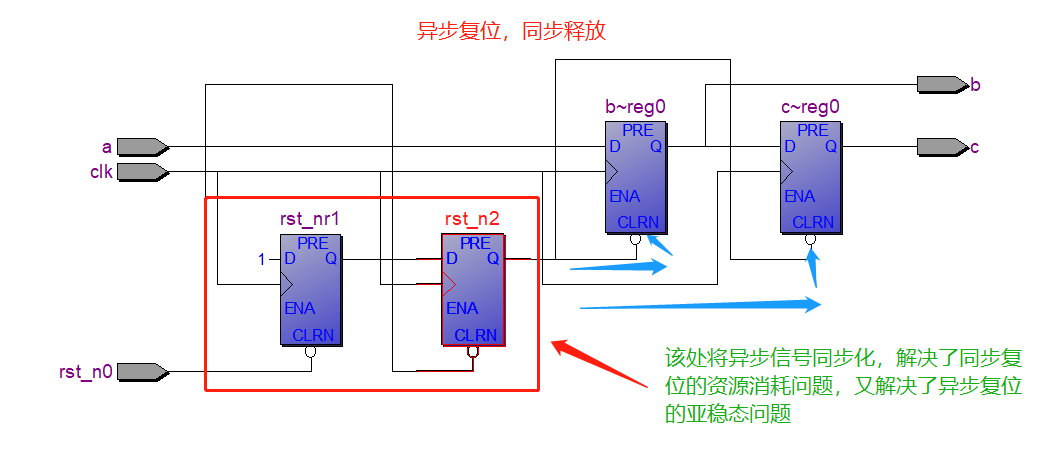

上述两级寄存器异步复位实例是clk检测rst_n状态时不确定到底是1还是0,如果将该rst_n状态用同一个时钟域的寄存器输出确定状态,然后再与目标寄存器(两级寄存器的rst_n状态相连)即可解决亚稳态问题。

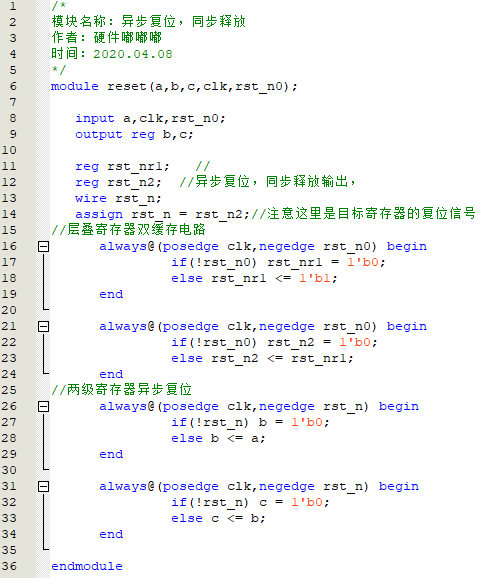

下面就是利用两个同一时钟沿触发的层叠寄存器组成,该时钟与目标寄存器的时钟域一致,实例如下:

PLL配置的复位设计

相信在大多数项目中都会设计到多个时钟,需用到器件内部PLL来产生分频和倍频时钟输入给不同模块,那么它们的系统复位电路融合设计才能更稳定呢?上面提到了异步复位,同步释放的方法又如何应用呢?

首先我们知道在系统复位后和PLL时钟输出前,系统工作时钟都会存在不确定的情况,那么我们设计所需解决的问题就是在PLL时钟有效输出前,系统的其他部分都保持复位状态。

设计思路:先用FPGA的外部输入时钟clk将FPGA的输入复位信号rst_n做异步复位,同步释放处理,然后这个复位信号输入到PLL,同时clk也输入到PLL。

最后

以上就是虚幻悟空最近收集整理的关于verilog中同步复位,异步复位,同步释放优缺点以及PLL配置复位设计的全部内容,更多相关verilog中同步复位内容请搜索靠谱客的其他文章。

发表评论 取消回复