D触发器

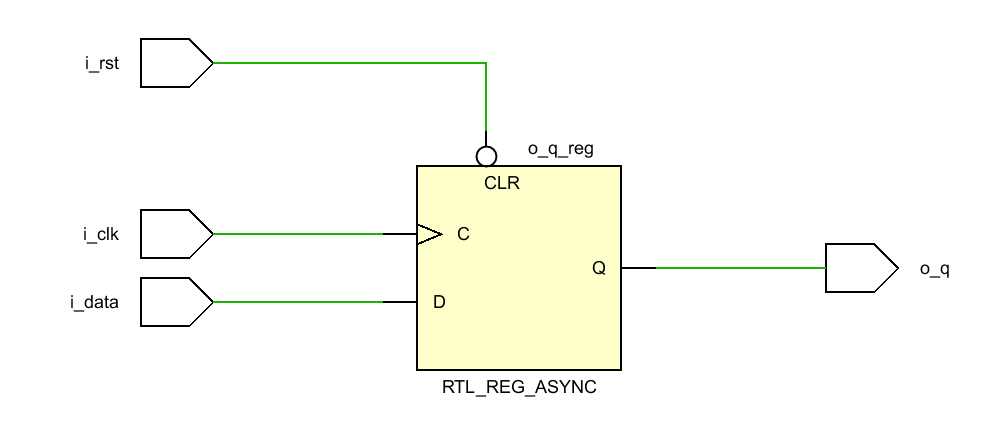

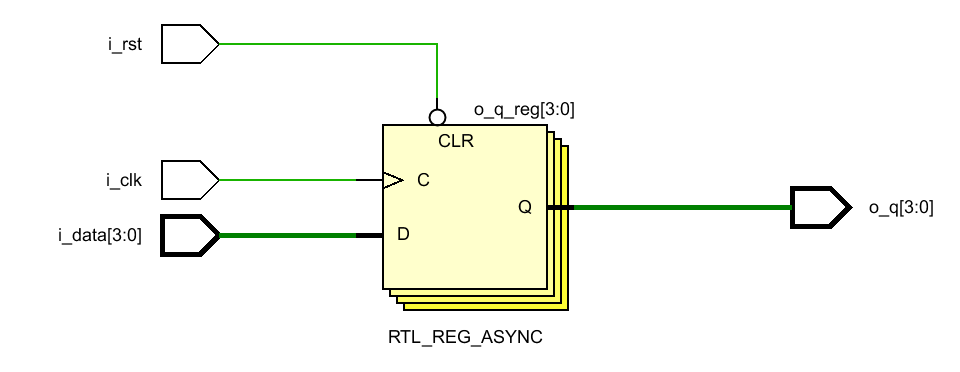

异步复位置零

always@(posedge i_clk or negedge i_rst)begin

if(!i_rst)

o_q<=1'b0;

else

o_q<=i_data;

end

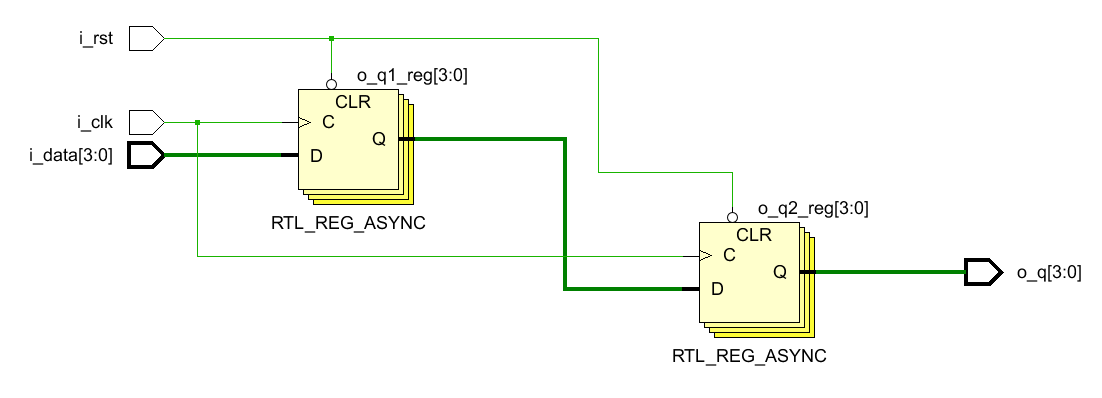

1.真值表:CLR=1(clear)则输出q为0

2.CLR上面的○表示取非

3.这里用到的是异步寄存器(ASYNC),用到一个cell(4bit的为4个cell)

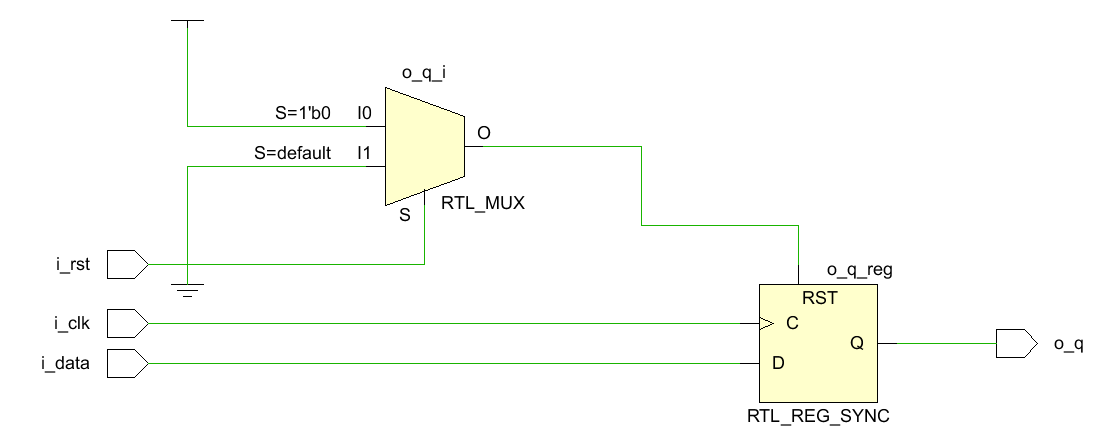

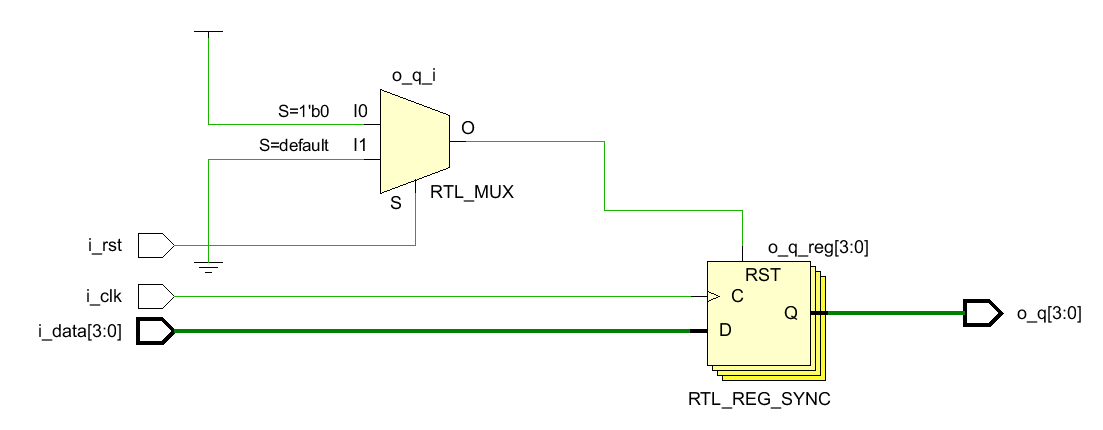

同步复位置零

always@(posedge i_clk)begin

if(!i_rst)

o_q<=1'b0;

else

o_q<=i_data;

end

1.真值表:RST=1则输出q=0

2.这里用到的是同步寄存器(SYNC),用到两个(4bit的为5个cell)cell,增加资源消耗,且复位的寄存器位宽越大消耗的资源越多

3.这里多路选择器MUX(也就是别人说的组合逻辑)的意思是rst(图中S信号)为0是输出POWER即1,rst为1则输出接地GROND(0),MUX的输出为RST

4.图一为单bit输入输出,图二为4bit输入输出

异步复位,同步释放

reg [3:0] o_q1;

reg [3:0] o_q2;

always@(posedge i_clk or negedge i_rst)begin

if(!i_rst)begin

o_q1<=4'd0;

o_q2<=4'd0;end

else begin

o_q1<=i_data;

o_q2<=o_q1;end

end

assign o_q=o_q2;

我想的就是直接做一个同步级联处理,但是下面的才是正确的

//-----------------------------------

//module ex1

//author: wyx

//function: D触发器(异步复位,同步释放)

//version:new creat

//-----------------------------------

module ex1

(

input i_clk ,

input i_rst ,

//input i_data ,

//output reg o_q

input [3:0] i_data ,

output reg[3:0] o_q

);

reg rst1;

reg rst2;

wire syn_rst;

always @ (posedge i_clk)begin

if(!rst)

o_q<=1'd0;

else

o_q<=i_data;

end

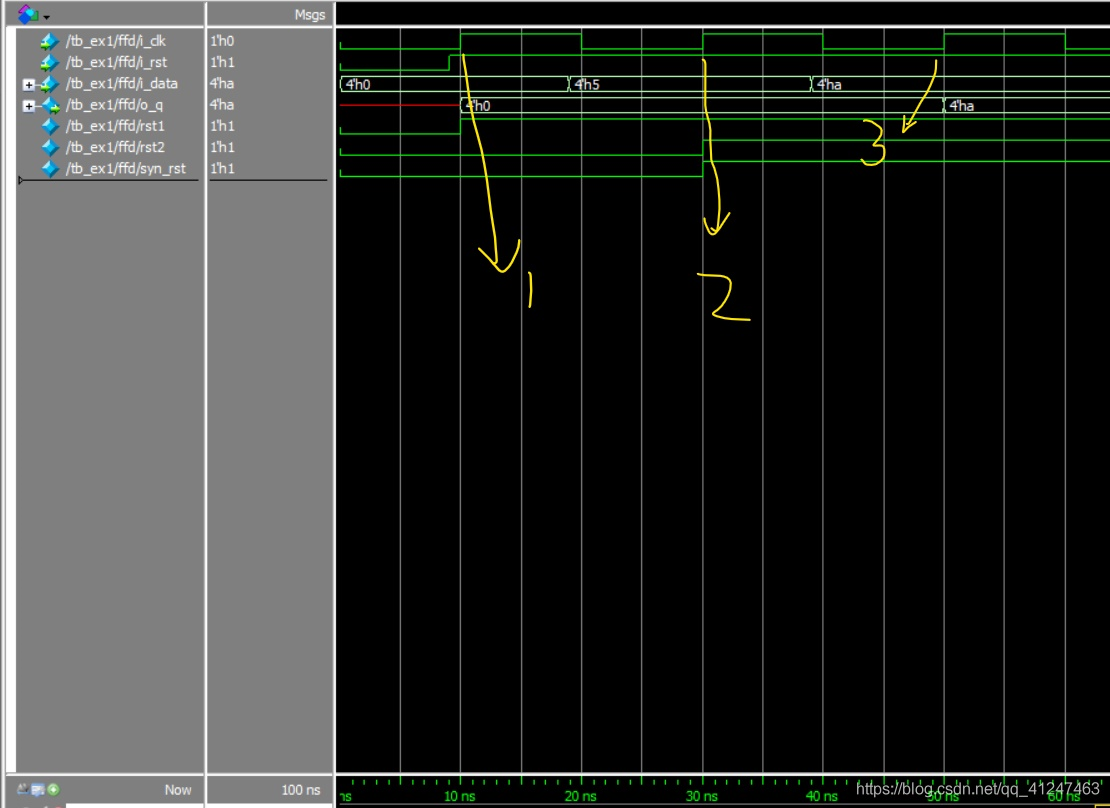

always @ (posedge i_clk or negedge i_rst)begin

if(!i_rst)begin

rst1<=1'd0;

rst2<=1'd0;end

else begin

rst1<=1'b1;//我就是想不通这里为什么是1

rst2<=rst1;

//答:因为这里是低有效复位信号,做的复位信号释放(也就是从0变为1)

//第一个时钟上升沿rst1=1(从0变为1),rst2=0(非阻塞赋值的特性,取的原来的值0);

//第二个上升沿rst1=1,rst2=1,syn_rst(同步复位信号)此时才会从0变为1,也就是释放复位信号

//因此第三个时钟上升沿输入的i_data的值才被赋给输出o_q(此时复位已经释放了)

end

end

assign syn_rst=rst2;

always @ (posedge i_clk)begin

if(!syn_rst)//第二个时钟上升沿做判断的时候,syn_rst还是第一个时钟上升沿时候非阻塞赋值的0,仿真时应该看敏感沿之前的值

o_q<=4'd0;

else//判断条件是第三个时钟上升沿才有效的(这时syn_rst被阻塞赋值rst2,rst2此时被分配到了(也就是得到了)它在第二个时钟上升沿被非阻塞赋值的1)

o_q<=i_data;

end

仿真波形:

仿真tb文件:

`timescale 1ns/1ns

module tb_ex1();

reg i_clk ;

reg i_rst ;

reg [3:0] i_data ;

wire [3:0] o_q ;

initial begin

i_clk<=1'b0;

i_rst<=1'b0;

i_data<=4'd0;

#9 i_rst<=1'b1;

#10 i_data<=4'd5;

#20 i_data<=4'd10;

end

always #10 i_clk=~i_clk;

ex1 ffd(

.i_clk (i_clk ),

.i_rst (i_rst ),

.i_data (i_data ),

.o_q (o_q )

);

endmodule

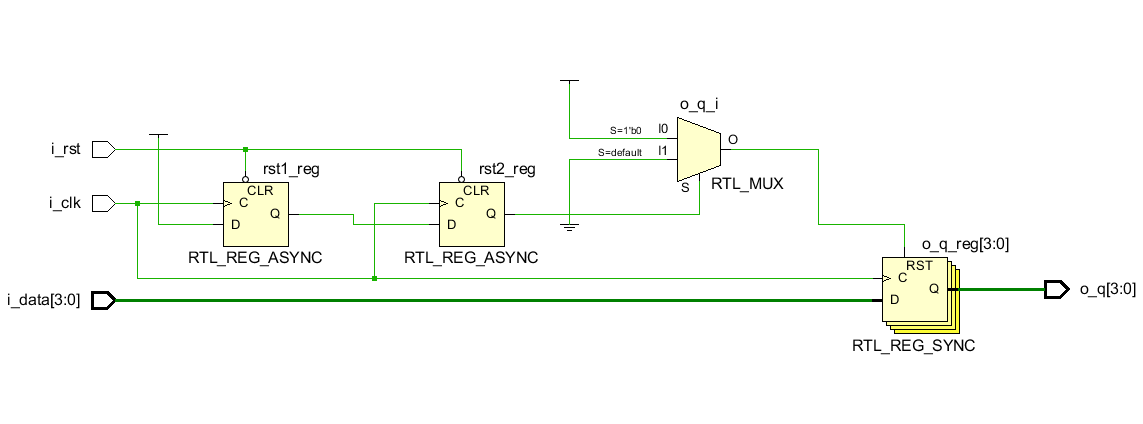

RTL结构:

总结一下就是,我之前想的属于直接将数据打两拍,它其实没有涉及到复位信号的同步释放(从RTL上面看到它只有异步寄存器),而Altera的标准版本是将复位信号做了打两拍处理,新的复位信号受本时钟域时钟信号的控制,也就是同步释放了,RTL结构上有同步和异步寄存器两种

资料夹

书目:FPGA深度解析的复位部分

李锐博恩/阻塞和非阻塞/这个专栏值得复习

老蒙蒙版本

李锐博恩版本/这里Altera综合出来的RTL更好看

表格对比版本

summer_awn版本/仿真

最后

以上就是称心小蘑菇最近收集整理的关于D触发器/同步异步复位/异步复位同步释放详细解释的全部内容,更多相关D触发器/同步异步复位/异步复位同步释放详细解释内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复