触发器电路简介

触发器有很多种类,这里主要论述D触发器。D触发器是CMOS数字集成电路单元中时序逻辑电路中的重要组成部分之一,学习D触发器具有十分重要的意义,可以帮助了解数字集成电路的单元。

D触发器属于时钟控制触发器,一般而言,时钟控制的触发器可以分成三大类:

第一类时钟控制触发器要求时钟信号的脉冲宽度小于触发器的传输延迟,即时钟信号先为高,接着必须在触发器的输出状态改变之前变为低。

第二类时钟控制触发器的特点是,时钟信号为高电平时触发器改变输出状态,通常称这种触发器为电平敏感触发器(锁存器Latch)。

第三类触发器的特点是边沿触发,时钟信号的上升/下降沿会使触发器改变输出状态(寄存器Register)。

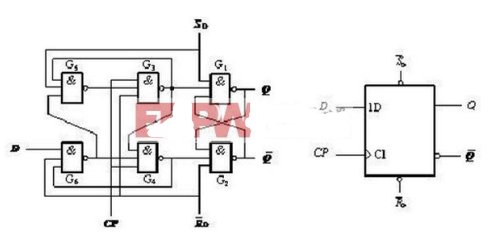

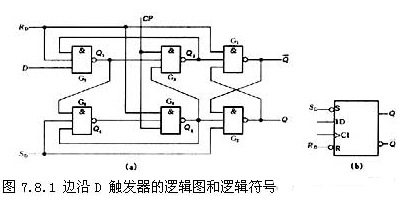

D触发器(data flip-flop)也称为维持-阻塞边沿D触发器,由六个与非门组成,其电路图及其逻辑符号如下图所示。其中G1和G2构成基本的RS触发器,G3和G4构成时钟控制电路,G5和G6组成数据输入电路。由于 分别为复位端和置位端,在分析D触发器工作原理时均视为高电平,以保证不影响电路工作。

D触发器(data flip-flop)也称为维持-阻塞边沿D触发器,由六个与非门组成,其电路图及其逻辑符号如下图所示。其中G1和G2构成基本的RS触发器,G3和G4构成时钟控制电路,G5和G6组成数据输入电路。由于 分别为复位端和置位端,在分析D触发器工作原理时均视为高电平,以保证不影响电路工作。

D触发器工作原理

边沿D 触发器:

负跳沿触发的主从触发器工作时,必须在正跳沿前加入输入信号。如果在CP 高电平期间输入端出现干扰信号,那么就有可能使触发器的状态出错。而边沿触发器允许在CP 触发沿来到前一瞬间加入输入信号。这样,输入端受干扰的时间大大缩短,受干扰的可能性就降低了。边沿D触发器也称为维持-阻塞边沿D触发器。

电路结构: 该触发器由6个与非门组成,其中G1和G2构成基本RS触发器。

工作原理:

SD 和RD 接至基本RS 触发器的输入端,它们分别是预置和清零端,低电平有效。当SD=0且RD=1时,不论输入端D为何种状态,都会使Q=1,Q=0,即触发器置1;当SD=1且RD=0时,触发器的状态为0,SD和RD通常又称为直接置1和置0端。我们设它们均已加入了高电平,不影响电路的工作。工作过程如下:

1.CP=0时,与非门G3和G4封锁,其输出Q3=Q4=1,触发器的状态不变。同时,由于Q3至Q5和Q4至Q6的反馈信号将这两个门打开,因此可接收输入信号D,Q5=D,Q6=Q5=D。

2.当CP由0变1时触发器翻转。这时G3和G4打开,它们的输入Q3和Q4的状态由G5和G6的输出状态决定。Q3=Q5=D,Q4=Q6=D。由基本RS触发器的逻辑功能可知,Q=D。

3.触发器翻转后,在CP=1时输入信号被封锁。这是因为G3和G4打开后,它们的输出Q3和Q4的状态是互补的,即必定有一个是0,若Q3为0,则经G3输出至G5输入的反馈线将G5封锁,即封锁了D通往基本RS 触发器的路径;该反馈线起到了使触发器维持在0状态和阻止触发器变为1状态的作用,故该反馈线称为置0维持线,置1阻塞线。Q4为0时,将G3和G6封锁,D端通往基本RS触发器的路径也被封锁。Q4输出端至G6反馈线起到使触发器维持在1状态的作用,称作置1维持线;Q4输出至G3输入的反馈线起到阻止触发器置0的作用,称为置0阻塞线。因此,该触发器常称为维持-阻塞触发器。总之,该触发器是在CP正跳沿前接受输入信号,正跳沿时触发翻转,正跳沿后输入即被封锁,三步都是在正跳沿后完成,所以有边沿触发器之称。与主从触发器相比,同工艺的边沿触发器有更强的抗干扰能力和更高的工作速度。

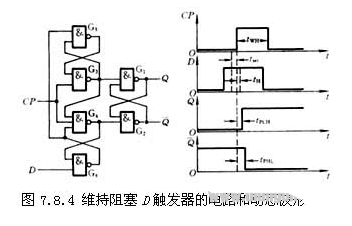

脉冲特性:

1.建立时间:由图7.8.4维持阻塞触发器的电路可见,由于CP信号是加到门G3和G4上的,因而在CP上升沿到达之前门G5和G6输出端的状态必须稳定地建立起来。输入信号到达D端以后,要经过一级门电路的传输延迟时间G5的输出状态才能建立起来,而G6的输出状态需要经过两级门电路的传输延迟时间才能建立,因此D端的输入信号必须先于CP的上升沿到达,而且建立时间应满足: tset≥2tpd。

2.保持时间:由图7.8.4可知,为实现边沿触发,应保证CP=1期间门G6的输出状态不变,不受D端状态变化的影响。为此,在D=0的情况下,当CP上升沿到达以后还要等门G4输出的低电平返回到门G6的输入端以后,D端的低电平才允许改变。因此输入低电平信号的保持时间为tHL≥tpd。在 D=1的情况下,由于CP上升沿到达后G3的输出将G4封锁,所以不要求输入信号继续保持不变,故输入高电平信号的保持时间tHH=0。

3.传输延迟时间:由图7.8.3不难推算出,从CP上升沿到达时开始计算,输出由高电平变为低电平的传输延迟时间tPHL和由低电平变为高电平的传输延迟时间tPLH分别是:tPHL=3tpd tPLH=2tpd

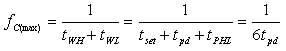

4.最高时钟频率:为保证由门G1~G4组成的同步RS触发器能可靠地翻转,CP高电平的持续时间应大于 tPHL,所以时钟信号高电平的宽度tWH应大于tPHL。而为了在下一个CP上升沿到达之前确保门G5和G6新的输出 电平得以稳定地建立,CP低电平的持续时间不应小于门G4的传输延迟时间和tset之和,即时钟信号低电平的宽度tWL≥tset+tpd,因此得到:

最后

以上就是正直鞋子最近收集整理的关于D触发器基本原理的全部内容,更多相关D触发器基本原理内容请搜索靠谱客的其他文章。

发表评论 取消回复