明德扬有完整的时序约束课程与理论,接下来我们会一章一章以图文结合的形式与大家分享时序约束的知识。要掌握FPGA时序约束,了解D触发器以及FPGA运行原理是必备的前提。今天第一章,我们就从D触发器开始讲起。

一、D触发器的基本概念

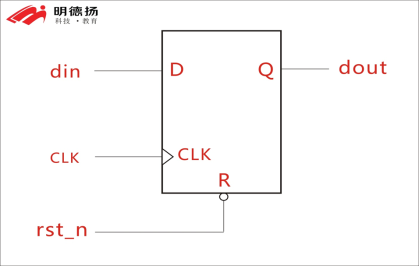

1、D触发器结构

首先是D触发器的结构,其硬件电路图如下所示,可以看到D触发器包含复位、时钟、输入和输出;信号由D端输入,clk给到上升沿的指示,Q端输出信号。

D触发器的功能很简单。

当R等于0时,q固定输出0;

当R等于1时,遇到CLK的上升沿时,将D的值赋给Q,D是什么Q就是什么;非CLK的上升沿,Q保持不变。

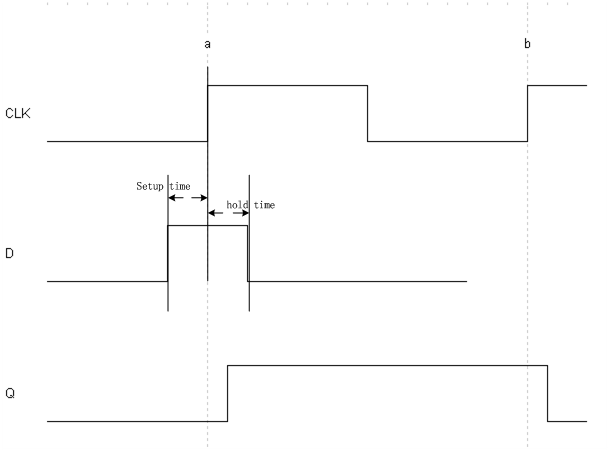

2、D触发器代码

D触发器的代码也很简单,如下图所示,从代码的描述来看,依旧是

当rst_n等于0时,q固定输出0;

当rst_n等于1时,遇到clk的上升沿时,将d的值赋给q,d是什么q就是什么;非clk的上升沿,q保持不变。

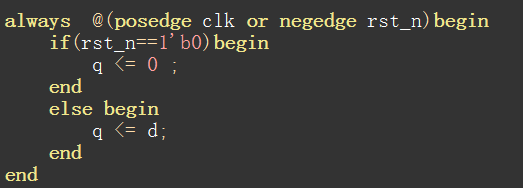

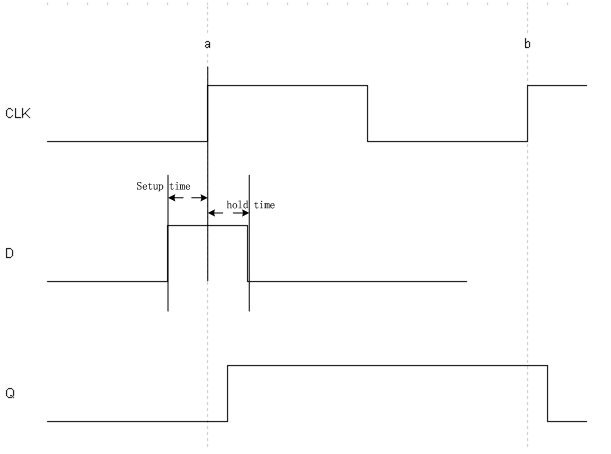

3、D触发器波形

D触发器工作波形如下所示,时钟处于上升沿的时,如果输入信号D为1,输出信号Q也为1;如果输入信号D为0,那么输出信号Q也为0。

4、建立时间和保持时间

前面波形图可以看到,D触发器在上升沿处进行信号采集,为了保证采集到的数据准确性,信号D在上升沿前后会保持状态一段时间。在上升沿前的这段时间为setup_time,叫做建立时间;上升沿后的这段时间为hold_time部分,叫做保持时间。

关于建立时间和保持时间有几个关键点需要注意。

首先D触发器的数据输入端必须在建立时间前到达,并且要保持到持续时间以后,这样才可以保证FPGA可以采集到正确的数据。

其次建立时间和保持时间是D触发器的固有属性,是不可改变的。注意,这里说的不可改变,是指不能从代码层次去改变。例如我们买了一个FPGA开发板,其FPGA芯片的D触发器建立时间和保持时间就是固定的,没办法从VERILOG去修改,除非换一个芯片。

二、电路的延时

1、电路延时原理

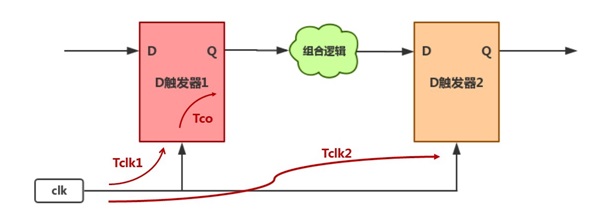

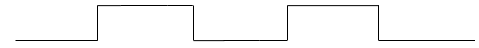

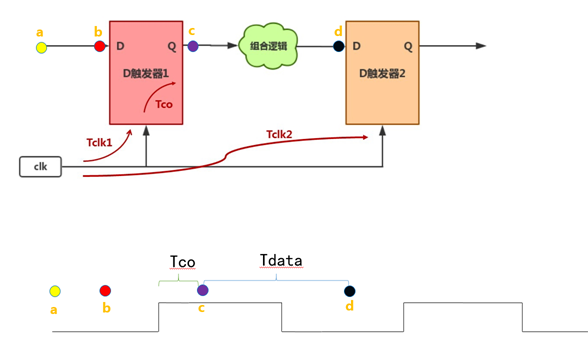

我们知道从物理层面看电平通过每个阶段都是需要一段时间的,这就是电路的延时,我们通过FPGA中最经典的结构来学习一下电路的延时。使用了两个D触发器,中间由组合逻辑进行相连,即通过一个组合逻辑电路将两个D触发器相连。电路图如下图所示:

从图中可以看出,一个有效信号经过D触发器1之后,接着经过一段组合逻辑(可以是加法器、选择器、乘法器这些电路,也可以仅仅是连线)然后到达另一个D触发器2,D触发器2对信号进行判断后继续进行输出。下面逐个分析这个基本结构里面包含的时间参数。

首先Tclk1是时钟到D触发器1的时间。Tclk2为时钟到达D触发器2的时间,在真实的物理情况下,因为有线路的延时,两个时钟采到的上升沿其实是不同的,有一点微小的差别;但是FPGA里面,我们经常把这个时间忽略掉,因为我们FPGA时钟时专门优化过的,它们之间的差别会比较小,因此在这里我们先忽略不计。Tclk1和Tclk2是时钟延时。

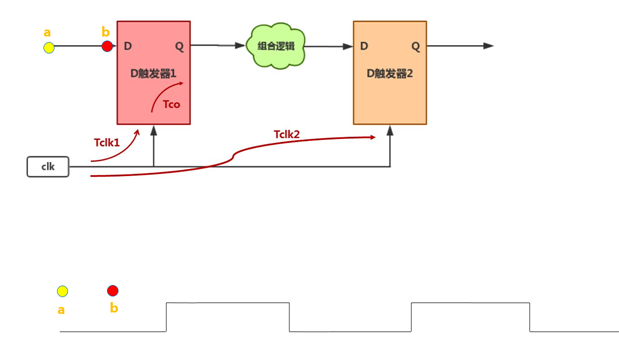

还有一段时间为D触发器的传输延时,即上升沿之后,采集到的数据从进入到出来这段时间延时。如下图所示,输出信号Q在上升沿后一段时间由0变1,这段为D触发器的传输延时。

接着D触发器1之后信号需要通过组合逻辑赋到D触发器2之前的位置,这段时间是组合逻辑的延时,即信号通过组合逻辑这段时间的延时为组合逻辑延时Tdata。

最后还有前面讲到的建立时间和保持时间,信号在D触发器2会有建立时间和保持时间,这就是D触发器本身的延时。

2、时序表示电路的延时

这里我们可以用时序来表示这组结构中的信号变化。如下所示,比如我们有两个时钟上升沿,在最开始,所有位置的信号都为0。

假设一个由0变1的信号需要通过前面的组合逻辑,首先D触发器1前面一段由0变1,即图中点a到点b变为1,这段时间在时序中如下图中点a与点b的位置。

1)D触发器传输延时

接着是D触发器的传输延时,在时钟上升沿处,信号1从D触发器1后输出,即下图中信号从c点输出,这段时间的延时在时序中为时钟上升沿处到信号输出的延时,即下面时序图中Tco部分。

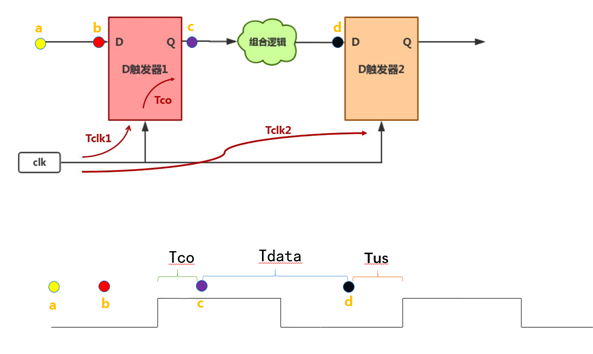

2)组合逻辑延时间

之后信号会通过组合逻辑,这段时间为组合逻辑的延时Tdata。如下图所示,此信号由点c通过组合逻辑接着传输到点d,在时序图中为Tdata部分。

3)建立时间

当然不要忘记我们前面讲的D触发器传输信号会有一段的建立时间,因此在时序中信号1会提前到达d点,即信号到达d点时,到达下一个时钟上升沿还有一段时间,如下面时序图中Tus部分所示。

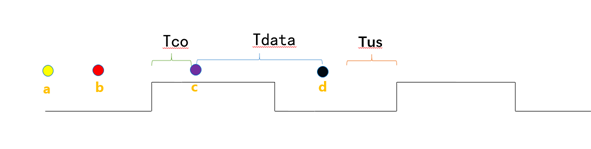

当然像上图中这样信号到达d点的时间与建立时间相等的情况是比较理想的状态,现实工程中大多数情况下信号1都会提前到达d点,等待建立时间的到来,即时间预量。实际的时序图如下所示,可以看到信号达到d点的时间与D触发器建立时间并不重合,中间会有一段时间预量,这才是实际工程中可以见到的情况。

以上就是由0变1的信号通过两个D触发器和一段组合逻辑的流程。在理想状态下整个过程的延时与时间周期是相等的,但是实际情况下会有一定的变化,这时需要我们具体问题具体分析。

三、D触发器在FPGA中的使用

1、FPGA的电路结构

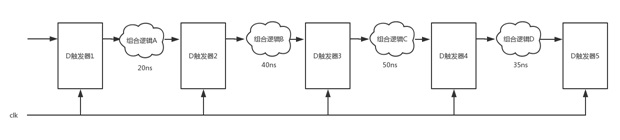

了解了两个D触发器的组合使用,下面学习FPGA的基本电路结构。

FPGA的基本电路结构如上图所示。我们可以把电路分成两个部分:D触发器和组合逻辑。每两个D触发器之间,都会有或多或少的组合逻辑。组合逻辑可以是乘法器、加法器、RAM,甚至就是一条简单的连线。前一个D触发器的输出端,经过组合逻辑运算后,给了下一个D触发器的输入端,等待时钟上升沿的时候,再传递给D触发器的输出端。

上图中,所有的D触发器都统一受时钟CLK的控制,都是在CLK的上升沿把输入的值传递给输出端。

FPGA中有4个组合逻辑A、B、C、D ,逻辑与逻辑之间,共使用了5个D触发器传输数据。其中组合逻辑A持续20纳秒,组合逻辑B持续40纳秒,组合逻辑C持续50纳秒,组合逻辑D持续35纳秒。时钟周期为100纳秒,即上升沿100纳秒产生一次;每个触发器的建立时间为5纳秒,保持时间为25纳秒。

2、现实案例

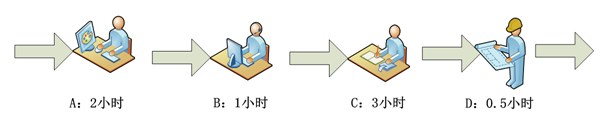

为了便于理解,我们用一个生活中的例子类比一下D触发器与组合逻辑的关系。如下图所示,现在有一个生产线生产一款产品,一共需要4个步骤,分别由员工ABCD来完成,其中A做完一个工序需要2小时,B需要1小时,C需要3小时,D是0.5小时。工厂统一规定每隔5个小时交接一次;为了避免交接混乱,要求交接点前5分钟交接,交接点后10分钟才能继续工作。

此生产线就像是前面我们讲到的FPGA电路结构,四个员工就相当于FPGA中四个组合逻辑,大家在同一个环境下工作,被同一个时钟所支配,相互间又有着传输关系。

要求每5个小时交接一次相当于100纳秒产生一次时钟上升沿;每一位员工交接给下一位员工的这个过程就相当于D触发器将输入的值赋给输出。

所有员工在交接点前5分钟都停下手中工作,进入准备交接状态,5分钟相当于D触发器的建立时间5纳秒;交接点后10分钟,大家依旧保持交接状态,10分钟相当于D触发器的保持时间25纳秒。

公司的规定必须提前5分钟,等待10分钟进行交接,就和D触发器的硬件特性相同,交接时间是不能因为个人改变的;不论工作什么时候完成,在交接点前5分钟一定要准备交接,交接点后保持交接状态10分钟才可以继续工作,这样才可以保证整个生产线可以流畅进行。

我们用了一个简单的案例比较清晰的理解了D触发器,通俗来说就是需要传输的数据等待在D触发器前,D触发器每个时钟都会在门口进行检测,检测到了有效数据后,在此时钟上升沿进行数据输出。

以上就是明德扬时序约束课程中D触发器部分的相关知识,想要获取时序约束相关资料的同学可以(加W:MDYfpga003 )陈老师

最后

以上就是花痴手链最近收集整理的关于时序约束系列之D触发器原理和FPGA时序结构的全部内容,更多相关时序约束系列之D触发器原理和FPGA时序结构内容请搜索靠谱客的其他文章。

发表评论 取消回复