不知道在学完数电第四章——组合逻辑电路之后,大家一开始有没有跟我一样的感觉:这些芯片功能是啥??那些控制信号是啥??我应该怎么连接??但是,当题目做的有了一定的量之后,发现考来考去无非是几种类型,下面博主就和大家一起总结一下,也当作自己的复习

文章目录

- 1. 编码器

- 2. 译码器

- 3. 数据选择器

- 4. 超前进位加法器

- 5. 数值比较器

- 6.组合逻辑电路的竞争冒险现象:

- 6.1 消除竞争冒险现象的方法:

1. 编码器

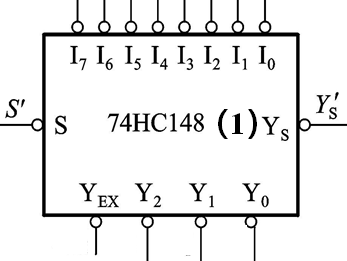

74HC148优先编码器

和普通编码器有类似之处,它也是对输入的二进制信号进行编码,但是它允许多个高电平输入,但是只会对优先级最高的输入进行编码,正常工作时应使S’ = 0。

下面是它的功能表:

关于编码器的题型解读:

最常见的就是用几篇编码器连成一个更多位的编码器了,比如用4片8线-3线编码器组合成32线-5线编码器,这种问题不难:我们把编码器从高位芯片到低位芯片串联起来(比如说高位芯片的S’接到下一个低位芯片的

Y

s

′

Y_s'

Ys′端这样),至于输出里面多出来的两位应该怎么连出来呢?

我们需要从

Y

E

X

′

Y_{EX}'

YEX′引出:

我们看看啊,本来我们的输出是不是

Y

2

Y

1

Y

0

Y_2Y_1Y_0

Y2Y1Y0三位对吧,我们现在考虑

Y

4

Y

3

Y_4Y_3

Y4Y3:因为4片芯片串联在了一起,所以最低位(我们约定为第4个芯片)所能够编码的二进制数的范围就是:0~7;第3个芯片所能够编译的二进制数的范围就是8 ~ 15,同理后面两个芯片的范围依次是:16 ~ 23、24 ~ 31。

那么我们就想啊,如果 Y 4 Y 3 Y_4Y_3 Y4Y3 = 11,那么表示输入的信号最小就是11000 = ( 24 ) 10 (24)_{10} (24)10,属于第一个芯片的工作范围,那么此时应该让第一个工作,其他芯片工作但无有效输入,即:

| Y E X 1 ′ Y_{EX1}' YEX1′ | Y E X 2 ′ Y_{EX2}' YEX2′ | Y E X 3 ′ Y'_{EX3} YEX3′ | Y E X 4 ′ Y'_{EX4} YEX4′ | Y 4 Y_4 Y4 | Y 3 Y_3 Y3 |

|---|---|---|---|---|---|

| 0 | 1 | 1 | 1 | 1 | 1 |

当 Y 4 Y 3 Y_4Y_3 Y4Y3 = 10,那么输入的最小值就是16,最大值为10111 = ( 23 ) 10 (23)_{10} (23)10,属于第二个芯片的工作范围,那么应该只让2芯片有有效输入:

| Y E X 1 ′ Y_{EX1}' YEX1′ | Y E X 2 ′ Y_{EX2}' YEX2′ | Y E X 3 ′ Y'_{EX3} YEX3′ | Y E X 4 ′ Y'_{EX4} YEX4′ | Y 4 Y_4 Y4 | Y 3 Y_3 Y3 |

|---|---|---|---|---|---|

| 1 | 0 | 1 | 1 | 1 | 0 |

后面的情况类似,这样,我们就可以通过真值表得到新增的输出 Y 4 , Y 3 Y_4, Y_3 Y4,Y3与 Y E X ′ Y'_{EX} YEX′的关系,从而用门电路表示出来

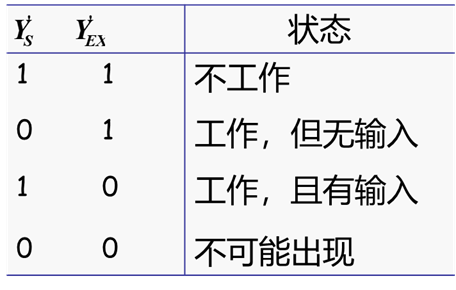

2. 译码器

【基本功能】这是比较常见的3线-8线译码器,输入是一个三位二进制数:

A

0

A

1

A

2

A_0A_1A_2

A0A1A2,然后把这个三位二进制数译成0~7其中一个十进制数,并且在对应位置输出

Y

′

Y'

Y′

【正常工作条件】当

S

1

S_1

S1 = 1,

S

2

′

+

S

3

′

S_2' + S_3'

S2′+S3′ = 0时,该译码器才会正常工作

【输出表达式】:这个是很重要的,译码器的输出

Y

′

Y'

Y′满足:

Y

i

′

=

(

m

i

)

′

Y_i' = (m_i)'

Yi′=(mi)′

例如:

Y

0

′

=

(

A

0

′

A

1

′

A

2

′

)

′

Y_0' = (A_0'A_1'A_2')'

Y0′=(A0′A1′A2′)′、

Y

5

′

=

(

A

0

A

1

′

A

2

)

′

Y_5' = (A_0A_1'A_2)'

Y5′=(A0A1′A2)′

关于译码器的题型解读:

- 用几片译码器连接成一个更大的译码器

- 用译码器产生给定的逻辑函数式

举个例子我来试着把它说明白:

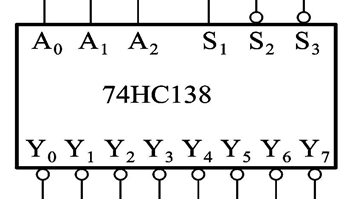

一,试用两片3线-8线译码器组成一个4线-16线译码器

首先,译码器原本就是有三个输入

D

0

,

D

1

,

D

2

D_0,D_1,D_2

D0,D1,D2的,这些我们不用管,直接把他们连起来就行,现在重点来看看第四个输入,也就是最高位的输入

D

3

D_3

D3:我们这里定义芯片(2)位高位芯片,那么,当

D

3

D_3

D3 = 1时,输入的四位二进制数最小就是1000,译出来就是8,因此,我们应该让(2)芯片工作,而(1)芯片禁止工作。 而结合我们刚刚说的,当

S

1

S_1

S1 = 1、

S

2

′

+

S

3

′

S_2'+S_3'

S2′+S3′ = 0时,译码器正常工作,因此,

S

1

S_1

S1直接接

D

3

D_3

D3(这里就有了一个通法:当我们有新增的输入时,我们就先看当这个新增的输入为1时,二进制数最小是多少,然后看这个最小的二进制数对应的十进制数在那个芯片的范围,就把这个新增信号和该芯片的

S

1

S_1

S1连在一起)

然后,

S

2

′

,

S

3

′

S_2',S_3'

S2′,S3′接在

D

3

D_3

D3也满足了当

D

3

D_3

D3 = 1时,(1)芯片不工作

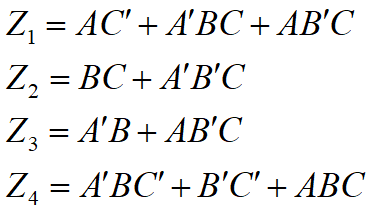

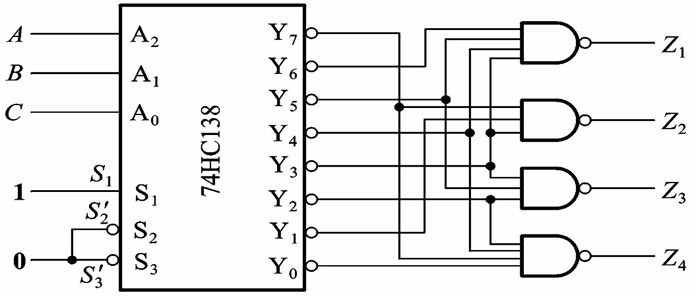

二,用3线-8线译码器74HC138设计一个多输出的组合逻辑电路,电路的逻辑函数式为:

这种题目的套路是:

将每一个输出化简为最小项之和:

Z

1

=

A

B

C

′

+

A

B

′

C

′

+

A

′

B

C

+

A

B

′

C

=

m

6

+

m

4

+

m

3

+

m

5

Z

2

=

A

B

C

+

A

′

B

C

+

A

′

B

′

C

=

m

7

+

m

3

+

m

1

Z

3

=

A

′

B

C

+

A

′

B

C

′

+

A

B

′

C

=

m

3

+

m

2

+

m

5

Z

4

=

A

′

B

C

′

+

A

B

′

C

′

+

A

′

B

′

C

′

+

A

B

C

=

m

2

+

m

4

+

m

0

+

m

7

Z_1 = ABC'+AB'C'+A'BC+AB'C = m_6 + m_4 + m_3 + m_5\ Z_2 = ABC+A'BC+A'B'C = m_7 + m_3 + m_1\ Z_3 = A'BC+A'BC'+AB'C = m_3 + m_2 + m_5\ Z_4 = A'BC'+AB'C'+A'B'C'+ABC = m_2 + m_4 + m_0 + m_7\

Z1=ABC′+AB′C′+A′BC+AB′C=m6+m4+m3+m5Z2=ABC+A′BC+A′B′C=m7+m3+m1Z3=A′BC+A′BC′+AB′C=m3+m2+m5Z4=A′BC′+AB′C′+A′B′C′+ABC=m2+m4+m0+m7

那么,我们就可以写出译码器的输出:

Z

1

=

(

Y

6

Y

4

Y

3

Y

5

)

′

Z

2

=

(

Y

7

Y

3

Y

1

)

′

Z

3

=

(

Y

3

Y

2

Y

5

)

′

Z

4

=

(

Y

2

Y

4

Y

0

Y

7

)

′

Z_1 = (Y_6Y_4Y_3Y_5)'\ Z_2 = (Y_7Y_3Y_1)'\ Z_3 = (Y_3Y_2Y_5)'\ Z_4 = (Y_2Y_4Y_0Y_7)'\

Z1=(Y6Y4Y3Y5)′Z2=(Y7Y3Y1)′Z3=(Y3Y2Y5)′Z4=(Y2Y4Y0Y7)′

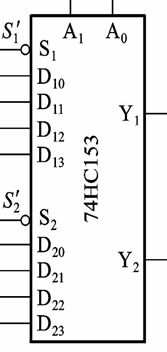

3. 数据选择器

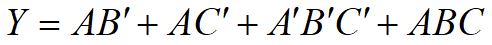

我们来看看双四选一数据选择器的样子:

其实它只用一班也是可以的,就是变成四选一的数据选择器,我们就以上面一半的四选一为例分析

【各个引脚的作用】

D

10

D

13

D_{10}~D_{13}

D10 D13是数据的输入端,

A

1

,

A

0

A_1,A_0

A1,A0是选通地址输入端(作为确定选择哪一个的信号),

Y

1

Y_1

Y1是选择之后的输出

【正常工作条件】:

S

1

′

S_1'

S1′ = 0

【输出表达式】这个是相当重要的:

Y

=

D

10

(

A

0

′

A

1

′

)

+

D

11

(

A

0

′

A

1

)

+

D

12

(

A

0

A

1

′

)

+

D

13

(

A

0

A

1

)

Y = D_{10}(A_0'A_1') + D_{11}(A_0'A_1) + D_{12}(A_0A_1') + D_{13}(A_0A_1)

Y=D10(A0′A1′)+D11(A0′A1)+D12(A0A1′)+D13(A0A1)

记忆方法:括号()里面的地址项是最小项!外面就是按照

m

i

m_i

mi的这个i的顺序乘上输入

关于数据选择器器的题型解读:

- 用几片数据选择器组成更大的数据选择器

- 用数据选择器产生给定的逻辑函数式

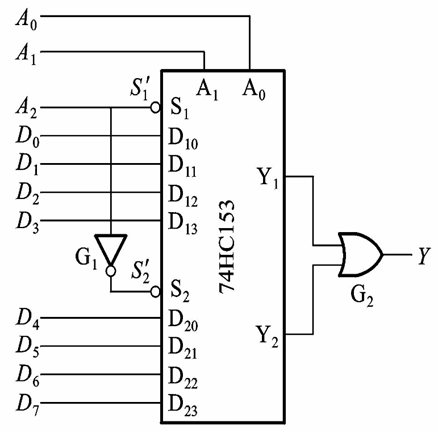

一,用双四选一数据选择器组成8选1数据选择器:

我们知道四选一数据选择器有2个地址输入,而八选一数据选择器有3个地址输入,因此,这多出来的一个地址输入就要从

S

′

S'

S′里面拿来:由于数据选择器正常工作的要求是

S

′

=

0

S' = 0

S′=0,

下面的四选一是选高位数的,当 A 2 A_2 A2 = 1时,数据最小就是100,也就是4,在下面那片数据选择器,因此,我们就要保证上面那篇数据选择器不工作。这就是本题的思路了

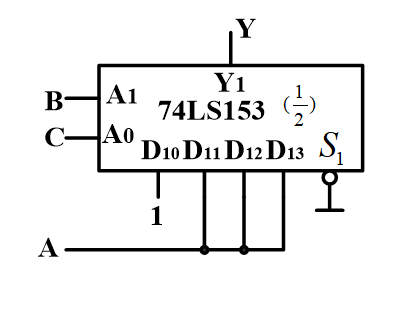

二,分别用四选一和八选一实现下面的逻辑函数:

首先,先把函数式化为最小项之和:

Y

=

A

B

′

C

+

A

B

′

C

′

+

A

B

C

′

+

A

B

′

C

′

+

A

′

B

′

C

′

+

A

B

C

=

A

B

′

C

+

B

′

C

′

+

A

B

C

′

+

A

B

C

Y = AB'C+AB'C'+ABC'+AB'C'+A'B'C'+ABC\ = AB'C + B'C'+ABC'+ABC

Y=AB′C+AB′C′+ABC′+AB′C′+A′B′C′+ABC=AB′C+B′C′+ABC′+ABC

由于我们要先使用四选一数据选择器,那么,有两个地址输入端,我们选BC好了,那么Y可以化为:

Y

=

1

∗

(

B

′

C

′

)

+

A

(

B

′

C

)

+

A

(

B

C

′

)

+

A

(

B

C

)

Y = 1*(B'C')+A(B'C) + A(BC') + A(BC)

Y=1∗(B′C′)+A(B′C)+A(BC′)+A(BC)

如果使用八选一,那么情况就不一样了,因为我们将要有3个地址输入端了,这样A,B,C就得全部用上,这样一来,D的数值也就随之确定了,Y可以写成这样的形式:

Y

=

1

∗

A

′

B

′

C

′

+

0

∗

A

′

B

′

C

+

0

∗

A

′

B

C

′

+

0

∗

A

′

B

C

+

1

∗

A

B

′

C

′

+

1

∗

A

B

′

C

+

1

∗

A

B

C

′

+

1

∗

A

B

C

Y = 1*A'B'C' + 0*A'B'C +0*A'BC'+ 0*A'BC + 1*AB'C' + 1*AB'C + 1*ABC' + 1*ABC

Y=1∗A′B′C′+0∗A′B′C+0∗A′BC′+0∗A′BC+1∗AB′C′+1∗AB′C+1∗ABC′+1∗ABC

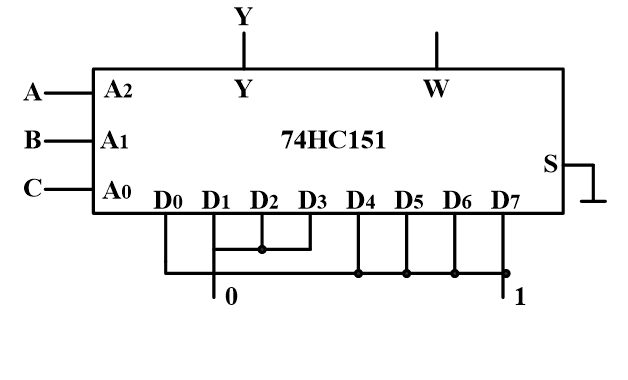

4. 超前进位加法器

【各引脚的功能】 A 0 A 3 A0~A_3 A0 A3, B 0 B 3 B_0~B_3 B0 B3是两个加数, C I CI CI是来自前一位的进位, C O CO CO是向高位的进位, S 0 S 3 S_0~S_3 S0 S3表示当前各位置的和(这里特别提醒一下:如果只是用了一篇超前进位加法器芯片,也就是说没有低位向高位的进位,又或者说这个芯片就是做的最低位的加法运算时,那么这个芯片的CI端要接地!!)

超前进位加法器老是喜欢考察:用加法器实现减法。但是大家不用害怕,减法是可以变为加法的,方法就是把减数写成补码的形式,再和原来的被减数相加

大家还记得一个二进制数的补码怎么求吗?正数的:原码=反码=补码;而对于负数,补码等于其数值位按位j取a反,然后+1

首先来说说怎么实现按位取反:我们可以用异或门实现,异或门就是可以用来取反的

那么+1怎么实现?我们可以令CI = 1,即低位有向高位进1,那不就完成+1的操作了吗?

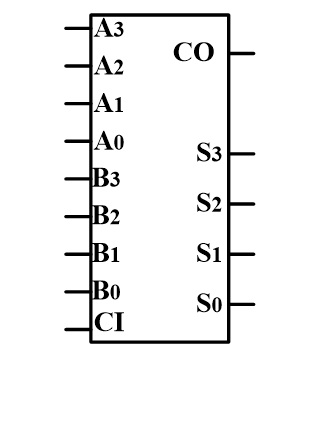

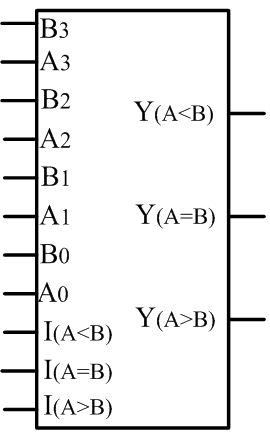

5. 数值比较器

我们来看看最后一个数值比较器:

【各引脚的功能】 A 0 A 3 A_0~A_3 A0 A3, B 0 B 3 B_0~B_3 B0 B3分别是待比较的两个三位二进制数, I I I表示低位比较的结果(因为我们比较是先从低位开始比较的)注意:如果没有低位了,我们就可以令 I ( A = B ) = 1 , I ( A > B ) = I ( A < B ) = 0 I_{(A=B)} = 1,I_{(A>B)} = I_{(A<B)} = 0 I(A=B)=1,I(A>B)=I(A<B)=0,Y表示比较的结果

常考的题型:

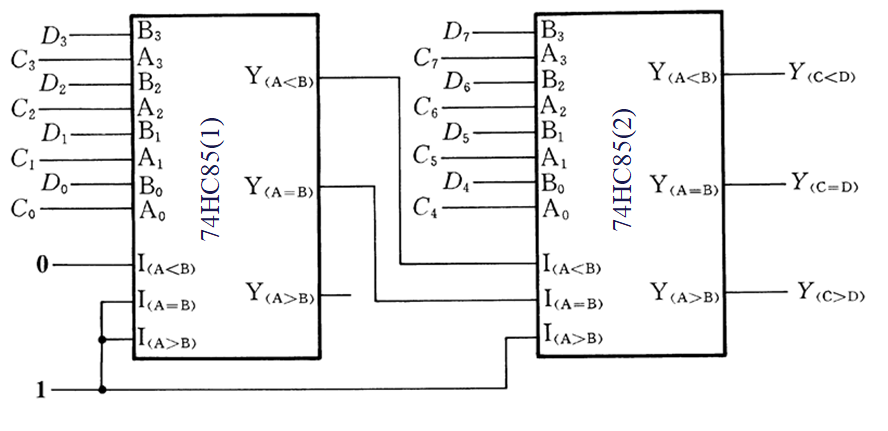

- 用多个数值比较器连接成一个更大的数值比较器

- 用一个数据比较器比较三个数的大小等等

一,用两片四位二进制数比较器连接成一个八位二进制数比较器

6.组合逻辑电路的竞争冒险现象:

这里先暂时简单提一下:如果这个组合逻辑电路输出的逻辑函数式可以化为: Y = A A ′ Y = AA' Y=AA′或者是 Y = A + A ′ Y = A + A' Y=A+A′的形式,那么说明该组合逻辑电路存在竞争冒险现象。

6.1 消除竞争冒险现象的方法:

- 接入滤波电容

- 引入选通脉冲

- 修改电路逻辑设计

最后

以上就是任性大神最近收集整理的关于【数字电子技术 Digital Electronic Technology 5】—— 组合逻辑电路设计题解题技巧归纳1. 编码器2. 译码器3. 数据选择器4. 超前进位加法器5. 数值比较器6.组合逻辑电路的竞争冒险现象:的全部内容,更多相关【数字电子技术内容请搜索靠谱客的其他文章。

发表评论 取消回复