一. 定义

-

在同步时序电路中,各触发器的时钟端全部连接到同一个时钟源上,只有当时钟脉冲到来时,电路的状态才能改变。(注意不要求是同一时钟,而是同源时钟。所谓的同源时钟是指同一个时钟源衍生频率比值为2的幂次方,且初相位相同的时钟。)

同步逻辑是指时钟之间有固定的因果关系逻辑, -

异步时序逻辑电路不存在统一的时钟,触发条件由多个控制因素组成,任何一个因素的跳变都可以触发寄存器的变化。

异步逻辑是指各时钟之间没有固定的因果关系逻辑。

比如有些触发器的时钟输入端与时钟脉冲源相连,这些触发器的状态变化就与时钟脉冲同步,而其他的触发器的状态变化不与时钟脉冲同步。比如用一个触发器的输出连结到另一个触发器的时钟端去触发的就是异步时序逻辑。

主要是用于产生地址译码器、FIFO和异步RAM的读写控制信号脉冲。

比如异步D触发器:

module D_yb(

always @(posedge clk or negedge rst or negedge set)

begin

if(!rst) q<= 0;

else if(!set) q<= 1;

else q<=d;

end

endmodule

同步D触发器:

module D_tb();

always @(poedge clk )

begin

if(rst) q<= 0;

else if(set) q<=1;

else q<=d;

endmodule

二. 同步时序设计的原则

为了保证稳定可靠的数据采样,要满足寄存器的Setup 时间和Hold 时间。

在进行组合逻辑设计时,always 组合逻辑信号敏感表应包括always 模块中使用到的所有输入信号和条件判断信号;避免组合逻辑反馈环路

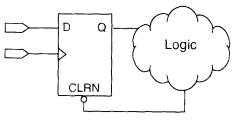

如图 所示即为一个典型的组合逻辑反馈环路,寄存器的Q 输出端直接通过组合逻辑反馈到寄存器的异步复位端,如果Q 输出为 0,经组合逻辑运算后为异步复位端有效,则电路将会进入不断清零的死循环。

三. 同步时序电路的优点:

1, 用异步时序逻辑很难控制由组合逻辑和延迟所产生的冒险和竞争。所以同步时序可以避免毛刺,

2, 工艺、环境的细微变化也会造成异步时序逻辑电路的失效。同步时序提高设计可靠性

3, 容易组织流水线,提高芯片的运行速度,

4, 所有的触发器可以同时运行,使静态时序分析变得简单

5, 有利于器件移植,包括FPGA 器件族之间的移植和从FPGA向结构化ASIC的移植.

四. 异步时序电路的优点:

异步电路具有:无时钟偏移(Skew)问题、低电源消耗、平均效能而非最差效能、模块性、可组合和可复用性等优点,因此近年来对异步电路研究增加快速,论文发表数以倍增

异步电路设计具有以下优点: 1 、低功耗。由于精细度时钟门控和零备耗功;

2 、高速。运算速度有实际局部延时决定,而不是有全局最差( worstcase) 延时决定;

3 、低电磁噪声辐射。局部时钟倾向于在随机时刻启动;

4、对于电源电压、温度以及制作过程中参数的变化具有鲁棒性。时序是基 于匹配延时的(并且能够对电路和导线延迟不敏感);

5 、更好的可重组性(composability )和模块化( modularity )。采用简单的握手接口和局部时钟;

6、没有时钟分配和时钟偏移( skew)问题。因为没有全局时钟信号,所以 不需要在整个电路中以最小相位偏斜来分配时钟。

最后

以上就是标致煎饼最近收集整理的关于同步时序电路和异步时序电路的全部内容,更多相关同步时序电路和异步时序电路内容请搜索靠谱客的其他文章。

发表评论 取消回复