文章目录

- 同步复位

- 异步复位

- 异步复位,同步释放

同步复位

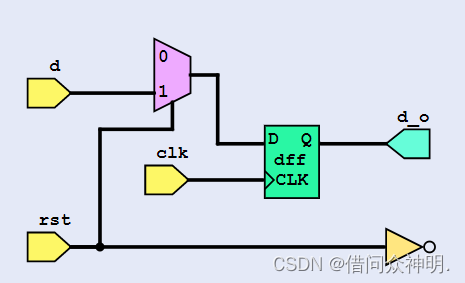

在同步复位中,复位信息的传递由时钟信号控制,仅当时钟上升沿到来时才会将复位信息和数据d存入寄存器中。电路图如下:

同步复位优缺点:

- 确保电路为同步的

- 减少毛刺的产生

- 由于实际中的电路器件一般为异步复位,故使用同步复位会消耗更多资源

- 需要更长的保持复位状态时间,至少要大于时钟周期

代码实现

/*

* @Author: yaohao

* @Date: 2022-06-10 10:45:05

* @Last Modified by: yaohao

* @Last Modified time: 2022-06-10 10:45:40

*/

module syn_rst(input clk, input rst, input d, output reg d_o);

always @ (posedge clk) begin

if (!rst) begin

d_o <= 1'b0;

end

else begin

d_o <= d;

end

end

endmodule

异步复位

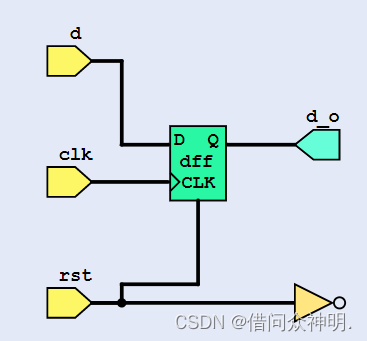

与同步复位相对应的异步复位则不受时钟的控制,由下图看出,异步复位多了一个rst复位线,于是电路可以随时进行复位。不受限于时钟上升沿的到来。

异步复位优缺点:

- 易于收敛数据,因为不需要时钟控制复位,功耗更低

- 毛刺的产生会导致电路异常复位

- 更容易产生亚稳态(当复位释放在时钟有效边沿附近时)

代码实现:

/*

* @Author: yaohao

* @Date: 2022-06-10 10:36:38

* @Last Modified by: yaohao

* @Last Modified time: 2022-06-10 10:39:50

*/

module asy_rst(input clk, input rst, input d, output reg d_o);

always @ (posedge clk or negedge rst) begin

if (!rst) begin

d_o <= 1'b0;

end

else begin

d_o <= d;

end

end

endmodule

异步复位,同步释放

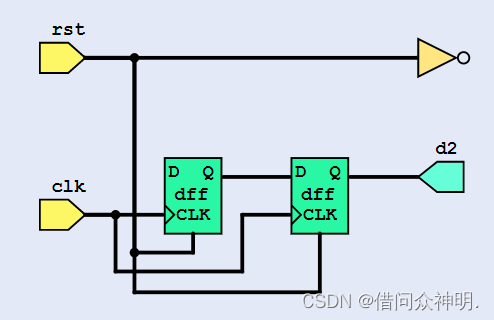

异步复位同步释放其实相当于将信号打两拍,避免异步复位释放引起的亚稳态。即使Q1输出信号为亚稳态,但是从触发器此时的数据输入接收的还是主触发器输出的Q1稳态的复位状态0。所以从触发器Q2的输出是稳定的复位状态0。打拍以后,主触发器已经从亚稳态状态恢复,输出的是稳定的工作状态电平了(d1=1)。此时从触发器采样的是稳定的工作状态电平,输出也是稳定的工作状态电平,复位完成。

代码实现:

/*

* @Author: yaohao

* @Date: 2022-06-10 11:14:36

* @Last Modified by: yaohao

* @Last Modified time: 2022-06-10 11:14:36

*/

module asyn_rst(input clk, input rst, output reg d2);

reg d1;

always @ (posedge clk or negedge rst) begin

if (!rst) begin

d1 <= 1'b0;

d2 <= 1'b0;

end

else begin

d1 <= 1'b1;

d2 <= d1;

end

end

endmodule

最后

以上就是英俊鼠标最近收集整理的关于异步复位同步释放的理解的全部内容,更多相关异步复位同步释放内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复