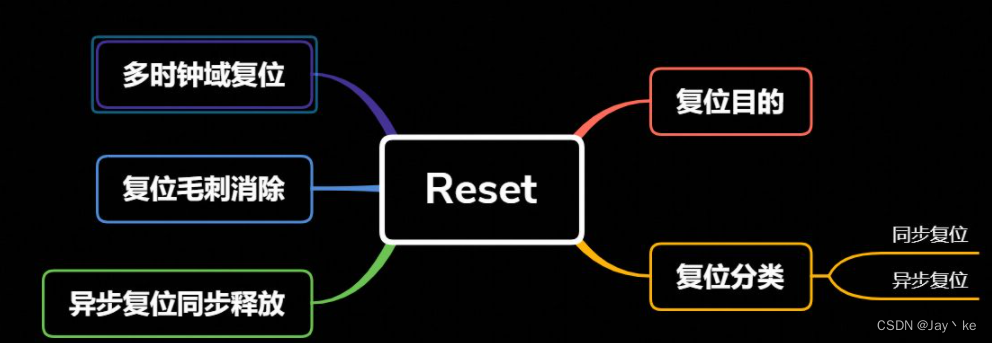

目录:

- 异步复位同步释放

- 1.复位目的:

- 2.同步复位:

- 3.异步复位:

- 4.异步复位同步释放:

异步复位同步释放

1.复位目的:

对一个芯片来说,复位的主要目的是使芯片电路进入一个已知的,确定的状态。主要是触发器进入确定的状态。在一般情况下,芯片中的每个触发器都应该是可复位的.

- 复位可以使电路从确定的初始状态开始运行

- 复位可以使电路从错误状态回到可以控制的确定状态

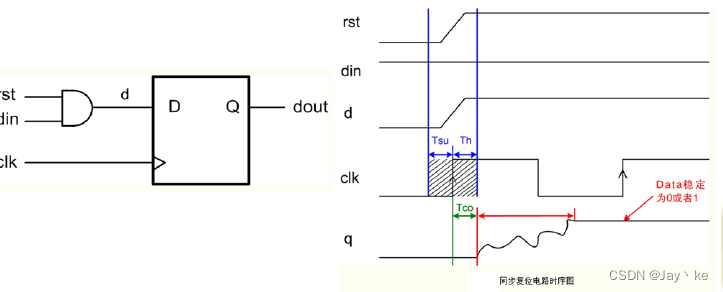

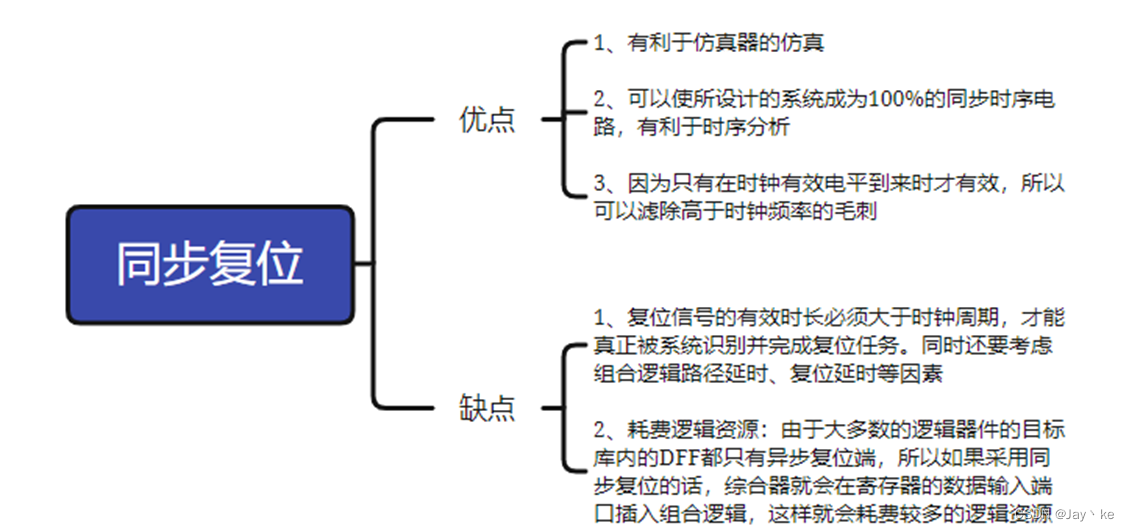

2.同步复位:

当reset信号为active的时候,寄存器在下一个时钟沿到来之后被复位,时钟沿到来之前寄存器还是保持其之前的值

Q:同步复位电路也会产生亚稳态吗

A:当复位信号的撤销时间在建立时间和保持时间以内时,也会产生亚稳态。

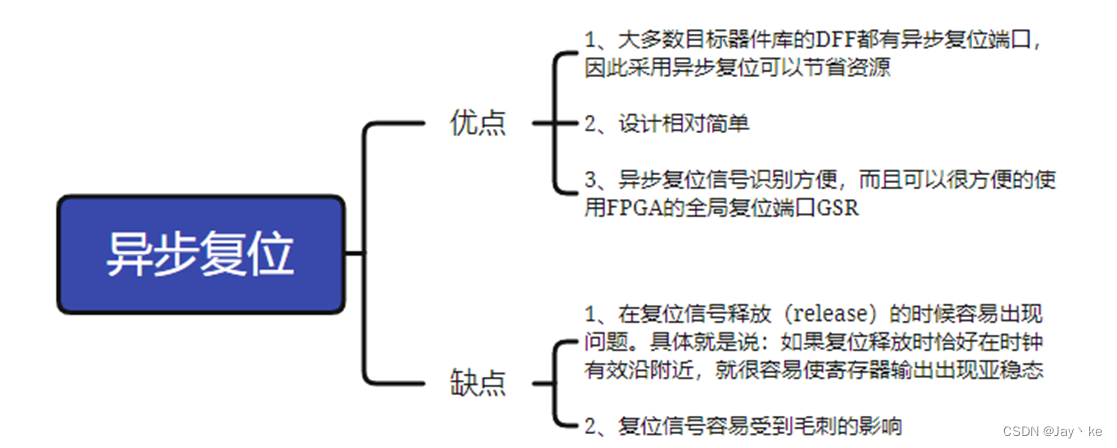

3.异步复位:

当reset信号为active的时候,寄存器立刻被复位,与时钟沿到来与否没有关系

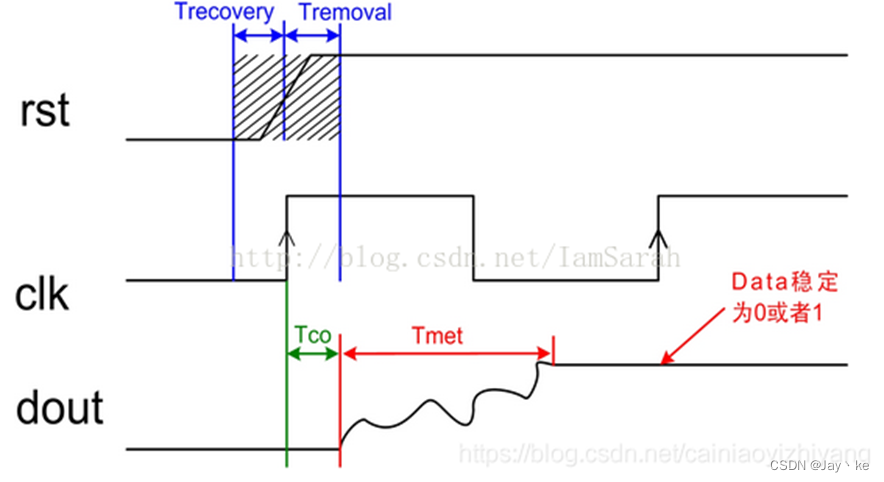

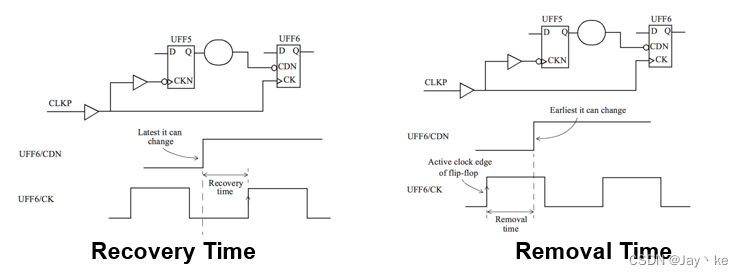

异步复位的亚稳态:当异步复位信号的撤销时间在Trecovery(恢复时间)和Tremoval(移除时间)之间时,输出结果就会出现亚稳态,造成复位失败

- recovery time和removal time都是检查异步信号(reset或preset或set)的释放沿,释放沿必须在时钟沿前面提前recovery time释放,或者在时钟沿后removal time之后释放

- 由于异步复位信号与时钟无必然联系,两者都是独立的,所以复位信号的释放将有一定的概率导致电路出现亚稳态

4.异步复位同步释放:

(1)异步复位,同步释放的含义

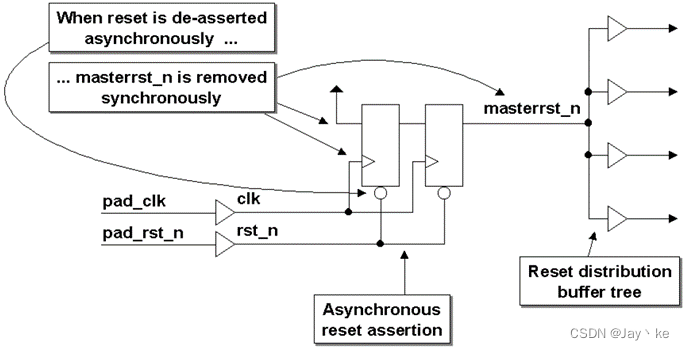

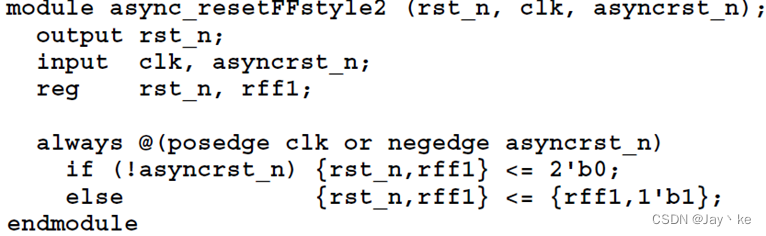

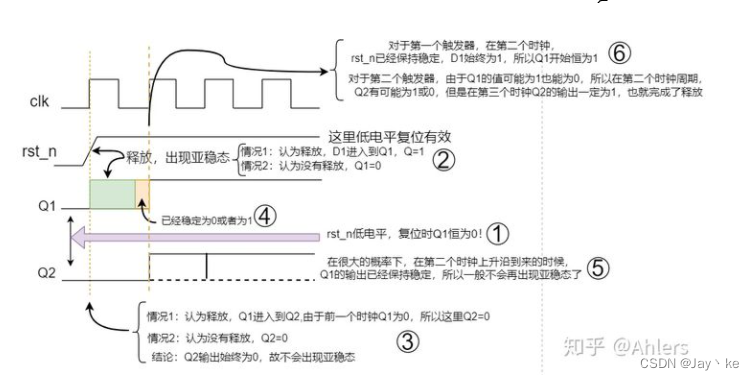

所谓异步复位同步释放,就是在rst_n信号为低时,立刻进行复位,即复位信号与时钟相互独立;而rst_n信号由低到高释放时,为了防止亚稳态的出现,将rst_n信号用DFF向后延一周期,外部复位信号不会在出现释放时与clk信号竞争,整个系统将与全局时钟clk信号同步

简单理解:第2级DFF释放信号与时钟clk边沿同步,所以释放信号在clk上升沿后需经过Tco(Tsu+thd)才能到达下一级DFF的复位端口,所以可以满足下一级DFF的recovery time和removal time,从而不会出现亚稳态

(2)异步复位,同步释放的优点

- 避免复位信号释放的时候造成亚稳态问题

- 只要复位信号一有效,电路就处于复位状态,与时钟沿无关

- 有效捕捉复位,即使是短脉冲复位也不会丢失

- 有明确的复位撤销行为。复位的撤离是同步信号,因此有良好的的撤离时序和足够的恢复时间

第一级FF的输入固定为“1”,第二级的FF用来消除解复位时可能带来的的亚稳态:

-

在resetn释放前,2个DFF的Q端都是0。

-

在resetn释放时,两个DFF的recovery/removal可能都出现不满足的情况,于是第1个DFF的Q会产生x值。

-

但对于第2个DFF来说,由于它的D/Q都是0,即使resetn会导致recovery/removal不满足,它的Q也依然是0,它的D端并不能马上就能看到第1个DFF的Q端产生的x值,而是会在下一个clk沿处才能看到这个x值。

-

很大概率在下一个clk沿处Q1会恢复稳定,一般不会出现亚稳态,若稳定后的值为1,则下一拍同步释放;若稳定后的值为0,则同步释放会延迟一拍,不会影响到后续电路

最后

以上就是深情百褶裙最近收集整理的关于异步复位同步释放异步复位同步释放的全部内容,更多相关异步复位同步释放异步复位同步释放内容请搜索靠谱客的其他文章。

发表评论 取消回复