同步复位、异步复位、异步复位同步释放笔记

一般来说,竞争-冒险是由于组合电路竞争冒险产生毛刺,从而影响整个逻辑电路。其实时序电路中也是存在竞争-冒险的,而这一特性主要是由D触发器输入端信号之间的竟争产生的。存在以下两种竞争-冒险。

1)clk上升沿与rstn下降沿同时到达

实际上对于D触发器而言,rstn信号的优先级高于clk信号,这样在rstn到来时,实现的是复位操作。因此,D触发器属于异步复位器件。

2)clk上升沿与rst n上升沿同时到达

当 rstn上升沿达到时,D触发器在理论上完成复位了,但是此时如果ck恰好在rstn 信号释放的周围,系统听谁的?此时在电路运行中,将会出现短暂的竞争一冒险问题,系统不稳定。

设计FPGA 电路时,由于rstn的优先级别比较高,所以电路通过全局时钟引脚输入。rstn信号与全局时钟elk称为异步时钟。异步时钟也有很多种类,以下是项目中经常遇到的几种∶

(1)系统异步复位信号;

(2)由其他处理器输入的时钟;

(3)内部组合逻辑产生的时钟。

为了解决这一问题,我们需要处理好异步复位信号的优先级,同时又要保证时钟信号的同步性。最简单的同步方案可以使用主时钟去打一拍,实现信号的同步。下面根据异步复位与同步复位的优缺点,分析外部复位信号,解决异步复位信号的同步化问题。

1.异步复位

always @ (posedge Clk or negedge Reset)

begin

if ( ~Reset)

Q <= 1’b0 ;

else

Q <= Data ;

end

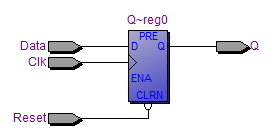

综合后的电路如下图:

这样的设计,没有对外部复位信号进行处理,设计上比较简单,无论时钟沿是否有效,都会立即对目标(如寄存器、RAM等)复位。异步复位的应用要点如下:

●指定异步复位时,只需在 always的敏感表中加入复位信号的有效沿即可,当复位信号有效沿到达时,无论时钟沿是否有效,复位都会立即发挥其功能。

异步复位的优点如下∶

●由于多数目标器件(如 FPGA和CPLD)和ASIC库的触发器都包含异步复位端口,异步复位会节约逻辑资源

●异步复位设计简单

● 对于大多数 FPGA,都有专用的全局异步复位/置位资源(GSR,Global Set Reset),使用GSR资源,异步复位到达所有寄存器的偏斜(skew)最小

尽管我们简化了电路,精简了设计,但由于外部复位信号与时钟信号存在一定程度的竞争,所以还是存在一些不预知的问题,如下所示。

(1)在复位信号释放(Release)时容易出现问题。具体来说,倘若复位释放时恰恰在时钟有效沿附近,就很容易使寄存器输出出现亚稳态,从而导致不稳定。

何为亚稳态?亚稳态就是数据处于最不稳定,将变未变的时刻。如图所示,当一个小球处于抛物面顶端时,它可能往左掉,也可能往右掉。这就好像一个信号在clk上升沿与 rstn下降沿同时到达时,2个改变的条件同时满足,会不知所措,这个问题会严重影响系统的稳定性。

亚稳态示意图

(2)复位信号容易受到毛刺的影响。这是由于时钟抖动或按键触发时的硬件原因造成的。复位信号如果抖动,上图中的这个小球将不断在顶部的一个区域内徘徊,这时系统处于极不稳定的状态,因此,这也是我们需要考虑的一个问题。

2.同步复位

为了解决异步复位的竞争冒险问题,将复位信号作为外部信号去采样,而非时钟信号;

always @ (posedge Clk )

begin

if ( ~Reset)

Q <= 1’b0 ;

else

Q <= Data ;

end

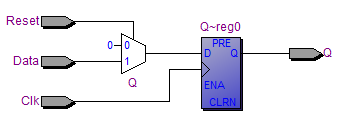

综合后电路图如下所示:

在上述代码中,复位信号作为一个使能信号进行采样,不再作为D触发器的复位端口,这样设计电路不存在竞争-冒险问题,因为Reset由全局时钟clk采样,整个设计中不存在优先级问题,全都是clk 说了算,它是一个具有权力与威望的"CEO"。

所谓同步复位是指当复位信号发生变化时,并不立即生效,只有当有效时钟沿采样到已变化的复位信号后,才对所有寄存器复位。同步复位的应用要点如下:

●指定同步复位时,always的敏感表中仅有时钟沿信号,仅仅当时钟沿采到同步复位的有效电平时,才会在时钟沿到达时刻进行复位操作。如果目标器件或可用库中的触发器本身包含同步复位端口,则在实现同步复位电路时可以直接调用同步复位端,然而很多目标器件(如PLD)和ASIC库的触发器本身并不包含同步复位端口,这样复位信号与输入信号组成某种组合逻辑(比如复位低电平有效,只需复位与输入信号两者相与即可),然后将其输入到寄存器的输入端.为了提高复位电路的优先级,一般在电路描述时使用带有优先级的if.else结构、复位电路在第一个if下描述,其他电路在else或else.if分支中描述。

同步复位电路的优点如下∶

(1)降低了亚稳态的出现概率;

(2)可以使所设计的系统成为100%的同步时序电路,这将大大有利于时序分析、而且综合出来的Fmax一般较高∶

(3)因为它只有在时钟有效电平到来时才有效,所以可以滤除高于时钟频率的毛刺。

在D触发器中,本身就有一个时钟输入端与复位端口。rst_n作为使能时钟采样信号,而数据则通过一个选择器输入,即当rst_n=1时,D触发器输入a∶而当rst_n=0时,D 发器输入0,这样理论上已经解决了clk与rst_n竞争-冒险的问题,但是将rst_n作为使能信号来操作,额外地消耗了FPGA 组合电路的资源。而整个系统都采用这种方式实现同步时,FPGA 消耗的总组合逻辑资源可想而知。

因此,同步复位电路也不是完美的,它的缺点如下∶

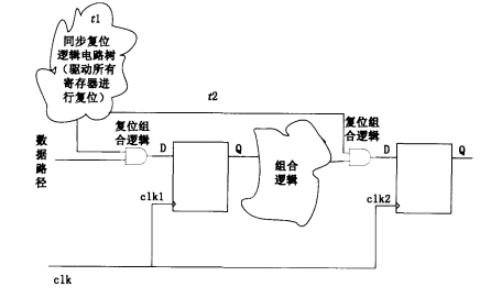

(1)同步复位的最大问题在于必须保证复位信号的有效时间足够长,这样才能保证所有触发器都能有效地复位。由于同步复位仅当时钟沿采样到复位信号时才会进行复位操作,所以其信号的持续时间起码要大于设计的最长时钟周期,以保证所有时钟的有效沿都能采样到同步复位信号.事实上,仅仅保证同步复位信号的持续时间大于最慢的时钟周期还是不够的,设计中还要考虑到同步复位信号树通过所有相关组合逻辑路径时的延时,以及由于时钟布线产生的偏斜(skew)。这样,只有同步复位大于时钟最大周期,加上同步信号穿过的组合逻辑路径延时,再加上时钟偏斜时,才能保证同步复位可靠、彻底。如图 所示,假设同步复位逻辑树组合逻辑的延时为t1,复位信号传播路径的最大延时为t2,最慢时钟的周期为Period max,时钟的skew为clk2-clk1,则同步复位的周期 T_ rst 应该满足如下公式。

T_rst>Period max +(clk2-clk1)+ t1+ t2;

(2)由于大多数的逻辑器件的目标库内的DFF 都只有异步复位端口,所以倘若采用同步复位,综合器就会在寄存器的数据输入端口插入组合逻辑,这样就会耗费较多的逻辑资源。

3.异步复位、同步释放

综上所述,异步复位存在亚稳态问题,同步复位存占用资源问题,都不是理想的解决方案,都存在一定的弊端。

D触发器有支持异步复位专用的端口,采用异步复位的端口无须额外增加器件资源。为了解决这一问题,以避免资源的浪费,我们还是希望处理外部复位信号,以实现直接或间接地控制D触发器的复位端。这样充分利用了D触发器,同时也节约了组合电路的消耗。因此,可以在将复位信号作为使能时钟的基础上,人为地生成另一个同步化后的同步复位信号。这需要我们用D触发器打一拍,然后直接提供给剩下的时序电路使用。修改后的同步化复位设计如下所示∶

module no_block1 (Data, Clk, Reset, Q);

input Data, Clk, Reset;

output Q;

reg Q;

reg rst_n;

always@(posedge Clk)

begin

if(~Reset)

rst_n<=1’b0;

else

rst_n<=Reset;

end

always @ (posedge Clk or negedge rst_n)

begin

if ( ~rst_n)

Q <= 1’b0 ;

else

Q <= Data ;

end

endmodule

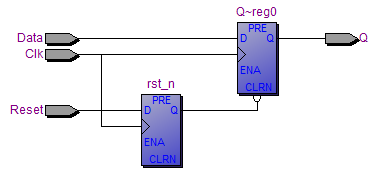

综合后的RTL如下图所示:

首先,第一个D触发器将Reset打了1拍(通过DEF将Reset同步到clk上去),这一过程将Reset信号同步到了ck时钟域∶接着输出的 rst_n信号直接作为第二个D触发器的复位信号。这样设计电路的好处在于只用了1个D触发器实现了异步复位信号的同步,在功能上实现了异步复位信号的同步化,在资源上大大减少了组合逻辑的使用。

事实上,这种方式也是最常见的异步时钟的处理方法。对于"异步复位,同步释放"、理解如下。

(1)所谓"异步复位"是针对D触发器的复位端口,它是异步的,但是设计中已经同步了异步复位信号,所以这只是某种意义上的"异步复位"。

(2)所谓"同步释放",实际上是由于我们设计了同步逻辑电路,外部复位信号不会在出现释放时与clk 信号竞争,整个系统将与全局时钟clk 信号同步。

最后

以上就是丰富金针菇最近收集整理的关于同步复位、异步复位、异步复位同步释放笔记的全部内容,更多相关同步复位、异步复位、异步复位同步释放笔记内容请搜索靠谱客的其他文章。

发表评论 取消回复