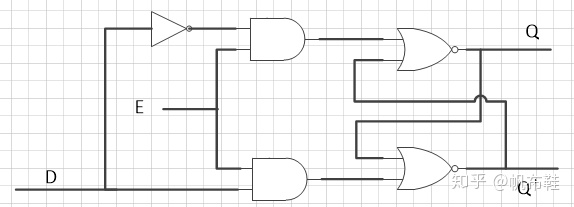

大多数D触发器在逻辑电路中是用来存储数据的。那么存在的问题是D Latch(D锁存器)和D-Flip-Flop(D触发器)有着什么样的区别呢?

最明显的区别就是,D锁存器的使能端是高电平使能,而在D触发器中是使用上升沿有效来进行使能的。

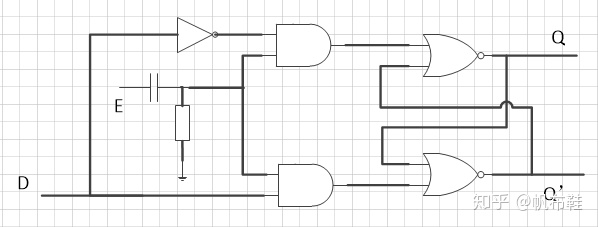

如果在ENABLE端口,电容取值

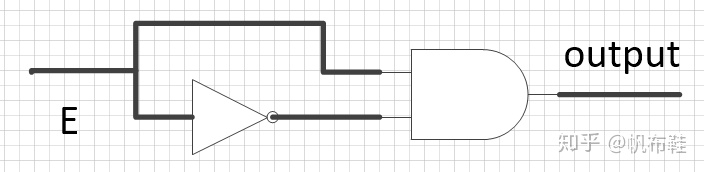

同时应当注意的是,这个上升沿有效的表达(脉冲形式)也可以使用逻辑电路非门和与门来实现,

当初始状态,即输入为0时,与门的两个输入量分别是0和1,输出自然是0。但是当有一个高电平来时,由于与门需要一定的时间去进行状态转换(几个ns的时间),则会存在几个ns的时间让与门的两个输入同时保持在高电平,这时就会产生一个高电平,也就是会形成一个几ns的脉冲。

值的注意的是,如果需要改变这一个时间,可以在与门的第二个输入串入3个/5个非门,来改变时间。

从时序图来看D触发器和D锁存器的不一样的情况

对于D Latch:在ENABLE为高电平期间,输出Q状态同输入D状态变化一致;

而对于D-Flip-Flop:仅仅在ENABLE的上升沿,输出Q会随着输入的D一致,其余情况保持不变。

上述电路的实现可以使用74LS08(与门)和74LS02(或非门)来实现。

最后

以上就是美满刺猬最近收集整理的关于双 JK 触发器 74LS112 逻辑功能。真值表_C08. D触发器的全部内容,更多相关双内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复