真双口RAM IP练习

真双口RAM可以说是灵活性最大的RAM IP核,因为它赋予了用户最大的设计空间,两个可以独立读写地址空间的端口,充分释放了FPGA程序设计上的可能。 但是实际上真双口RAM在工程项目中还是和单双口RAM一样使用频率比较低的,因为其太过灵活自由了,就导致了用户在设计程序的过程中,比较难以驾驭,最大的苦恼即来自于两个独立读写端口的不可避免的读写冲突,当然也有一些FPGA工程师单独做了一个相对复杂的读写状态机,在程序设计上可以规避读写冲突,但是笔者也和大部分朋友们一样,比较青睐于简单的设计方式,在大部分情况下简单的就是最好的,在保证设计效果的同时,兼顾代码的易读性和实用性可能是一名优秀的FPGA工程师必备技能。

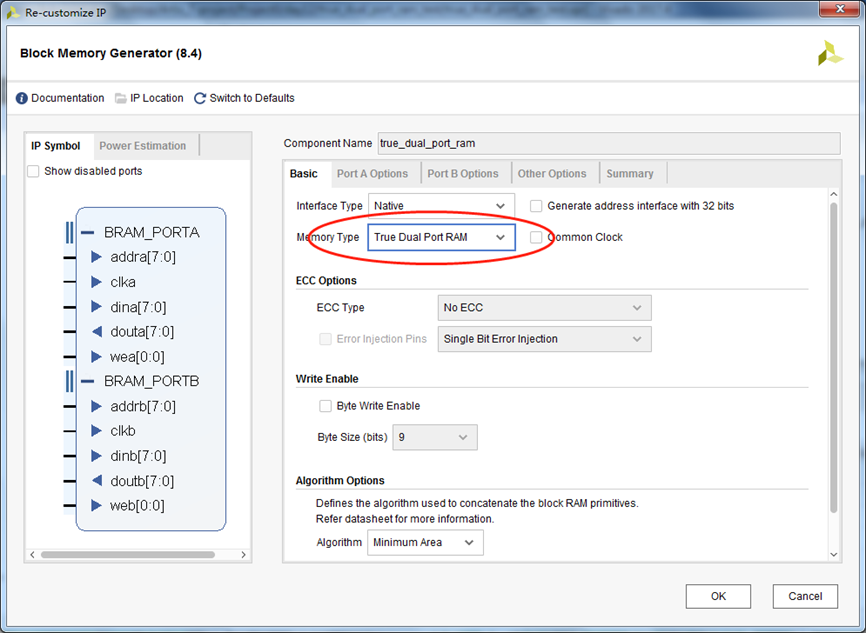

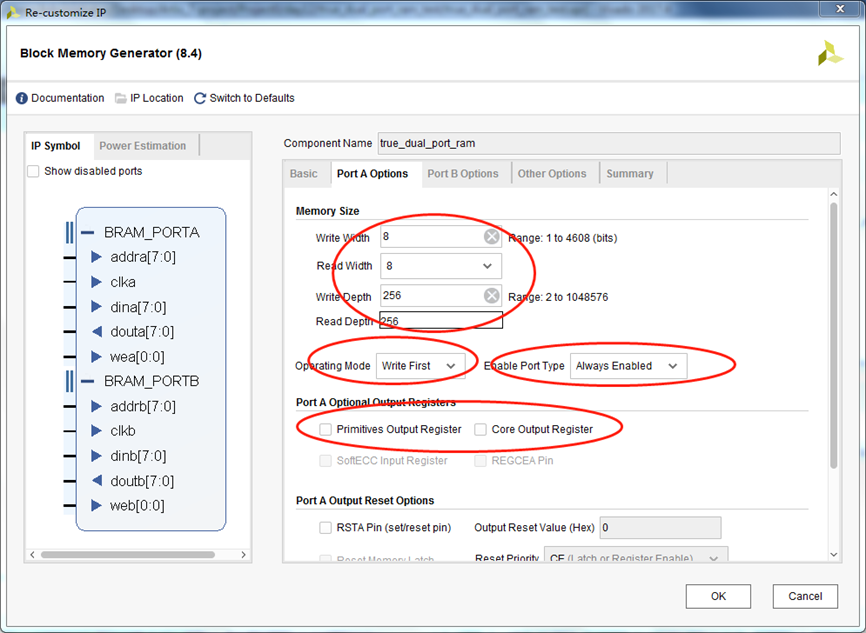

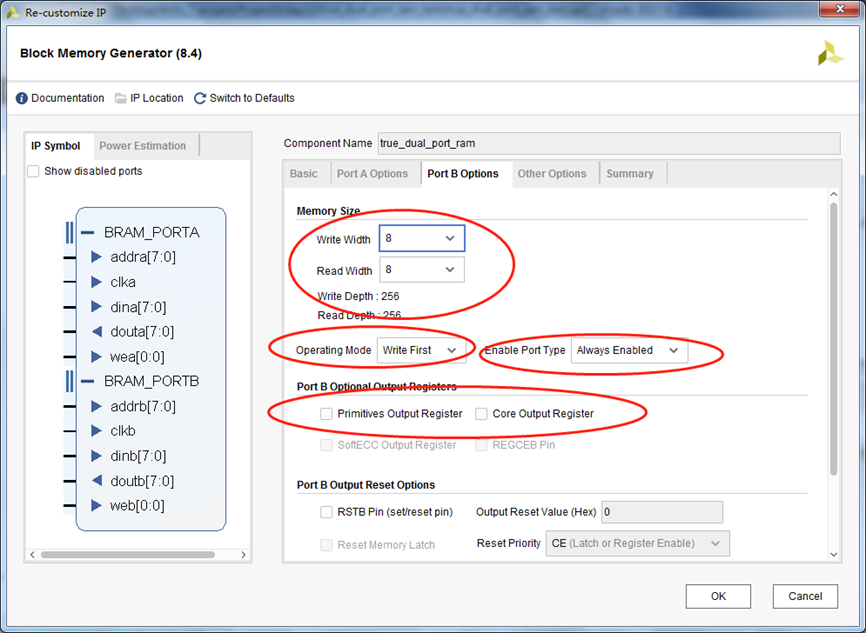

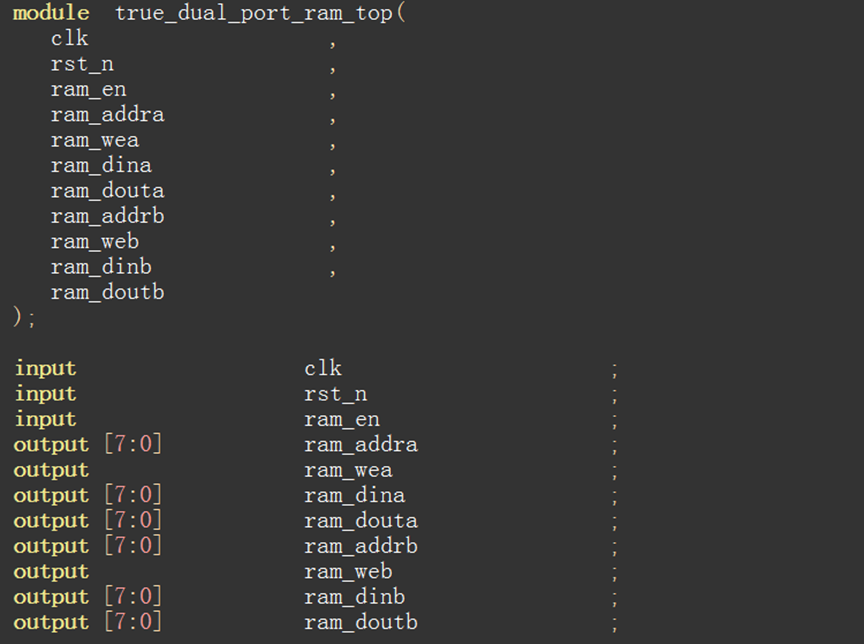

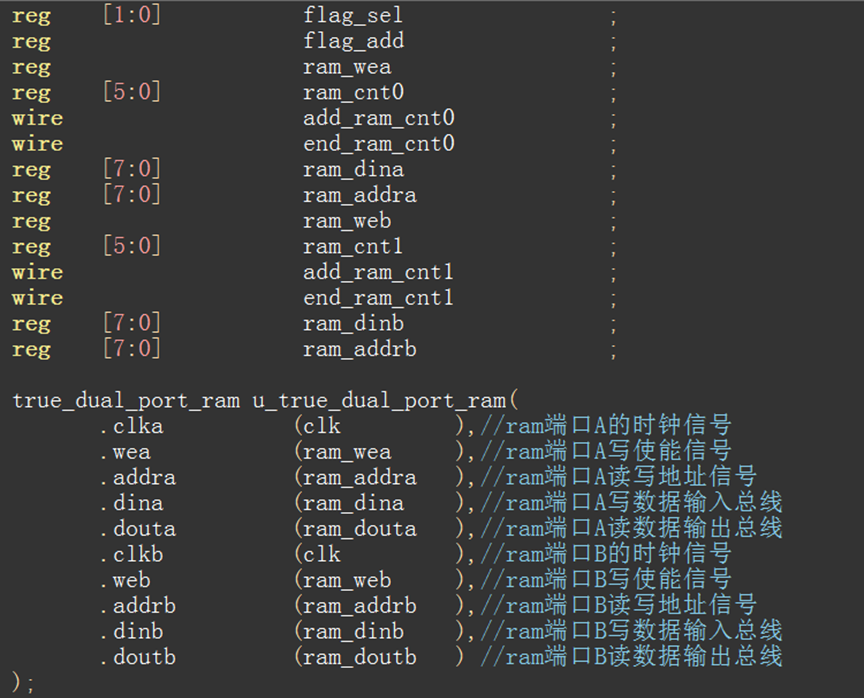

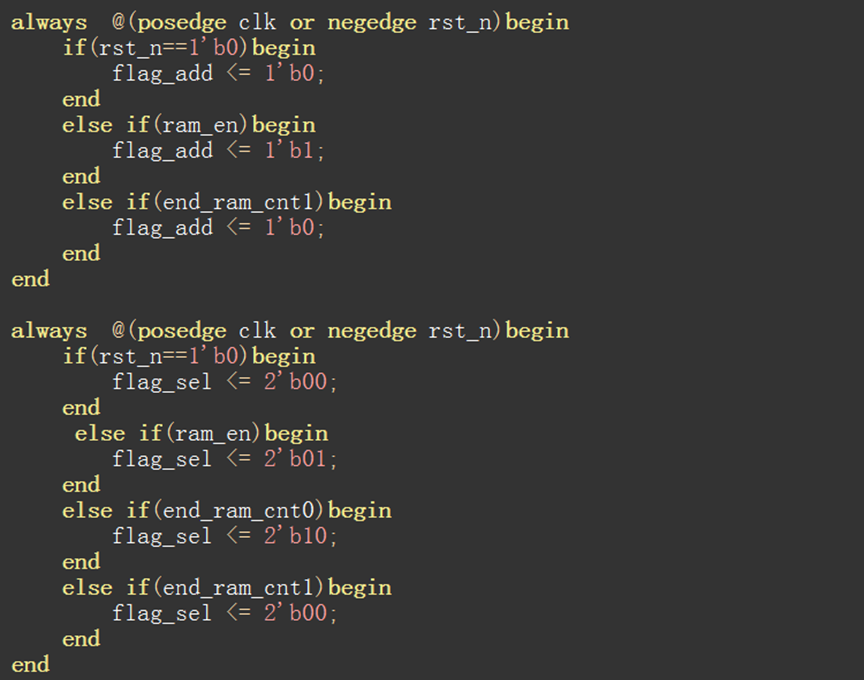

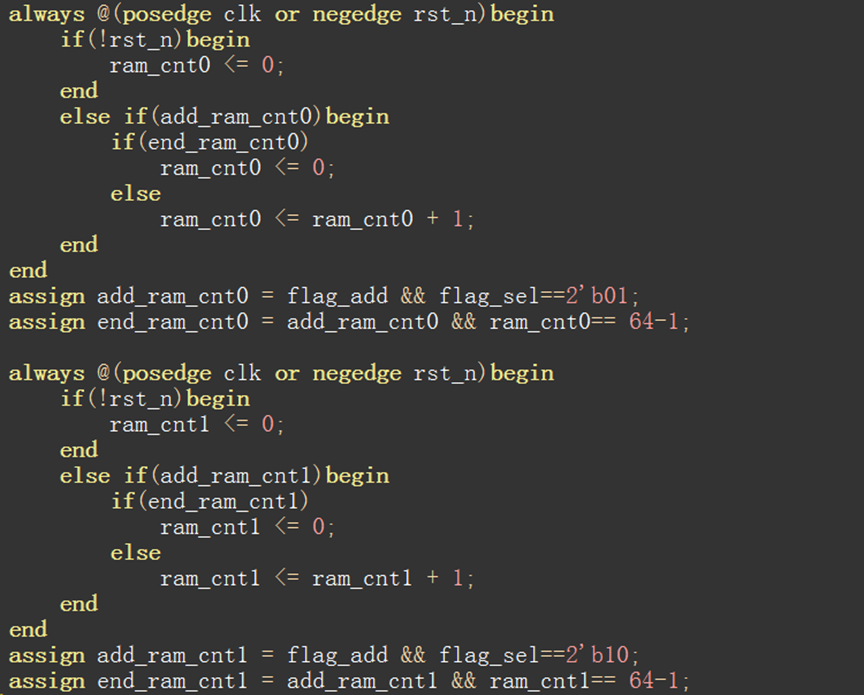

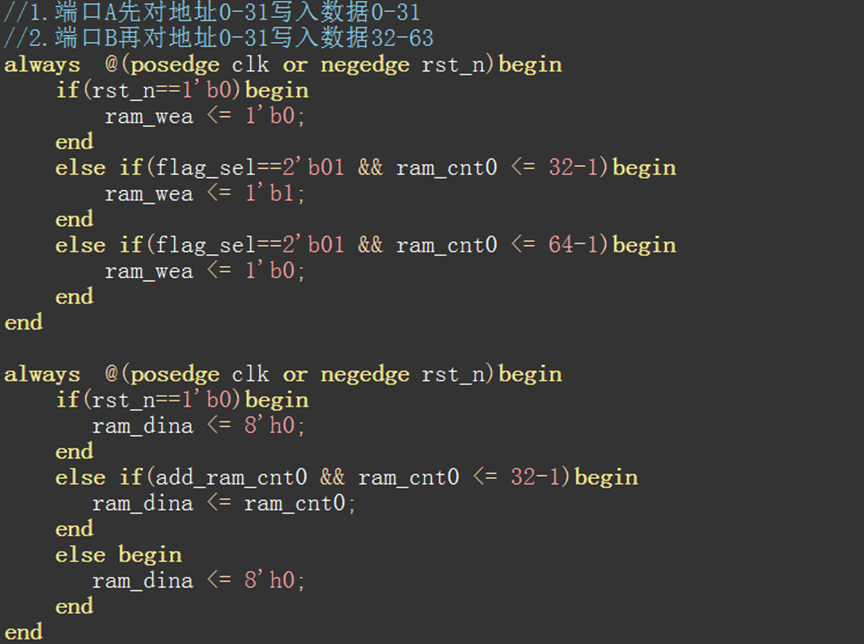

这里也设计一个简单的模块用以测试真双口RAM的各个输入信号接口的功能,本模块包含读写位宽均为8位,读写深度是256的真双口RAM,先通过端口A对0-31地址写入数据0-31,然后读0-31地址的数据,再通过端口B再对0-31地址写入数据32-63,然后读0-31地址的数据,如表1真双口RAM IP练习设计中的信号列表,如图1至图3,是对真双口RAM IP核的内存类型、端口AB的初始化配置。

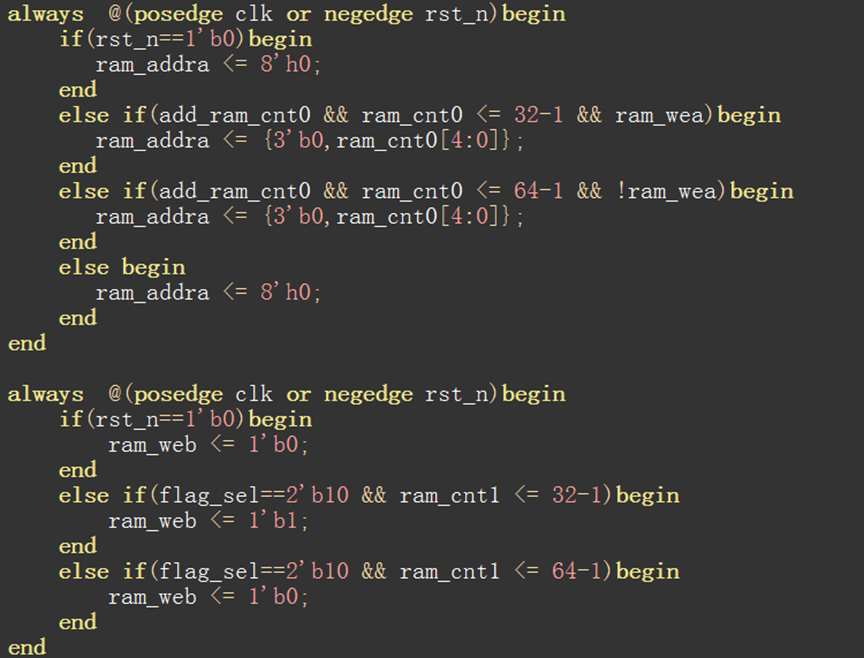

因为在IP核初始化时候选择的是写优先模式,所以当端口通过ram_din信号写入RAM的同时,ram_dout也会输出同样的写入数据,本模块的功能相对简单些,所以在这里笔者用了flag_sel信号量指示各个状态,而不再使用状态机去实现,简化了代码逻辑,当本模块收到了上游模块发来的ram_en使能信号,flag_sel由0置为1;接着当端口A完成了写入0-31地址的数据,且读完0-31的数据后,flag_sel由1置为2;最后当端口B完成了写入0-31地址的数据,且读完0-31的数据后,flag_sel由2置为0,完成整个对真双口RAM的模拟测试,整个代码设计不难理解,如图4是真双口RAM IP练习的代码设计。

| 信号列表 | ||

| 信号名 | I/O | 位宽 |

| clk | I | 1 |

| rst_n | I | 1 |

| ram_en | I | 1 |

| ram_addra | O | 8 |

| ram_wea | O | 1 |

| ram_dina | O | 8 |

| ram_douta | O | 8 |

| ram_addrb | O | 8 |

| ram_web | O | 1 |

| ram_dinb | O | 8 |

| ram_doutb | O | 8 |

表1 真双口RAM IP练习设计中的信号列表

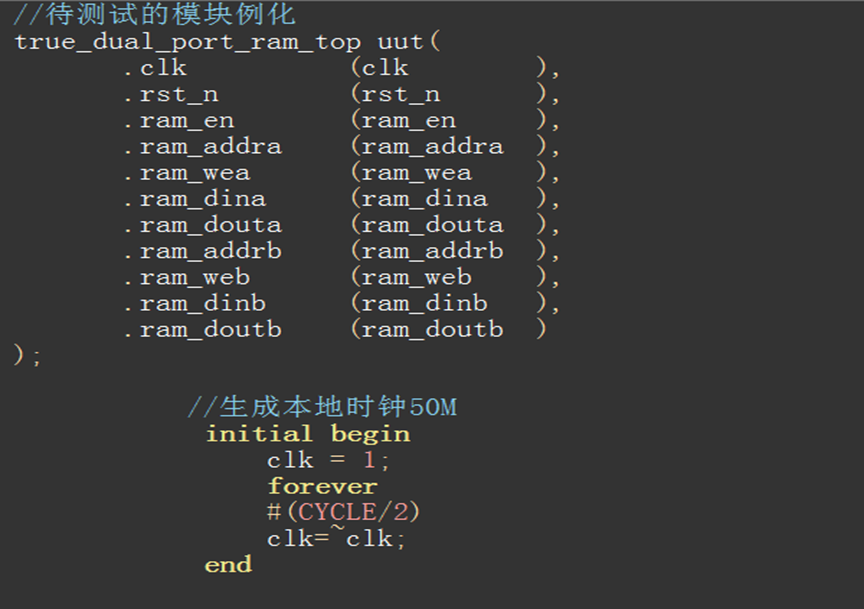

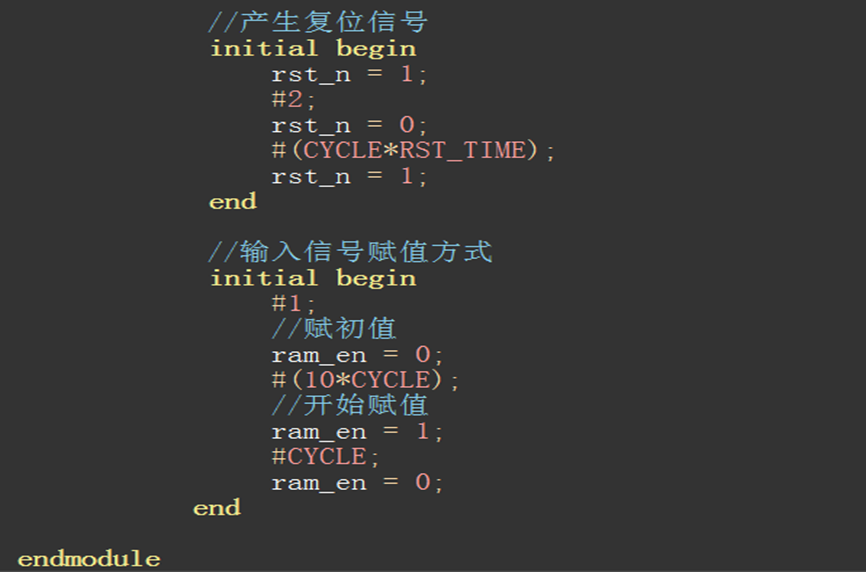

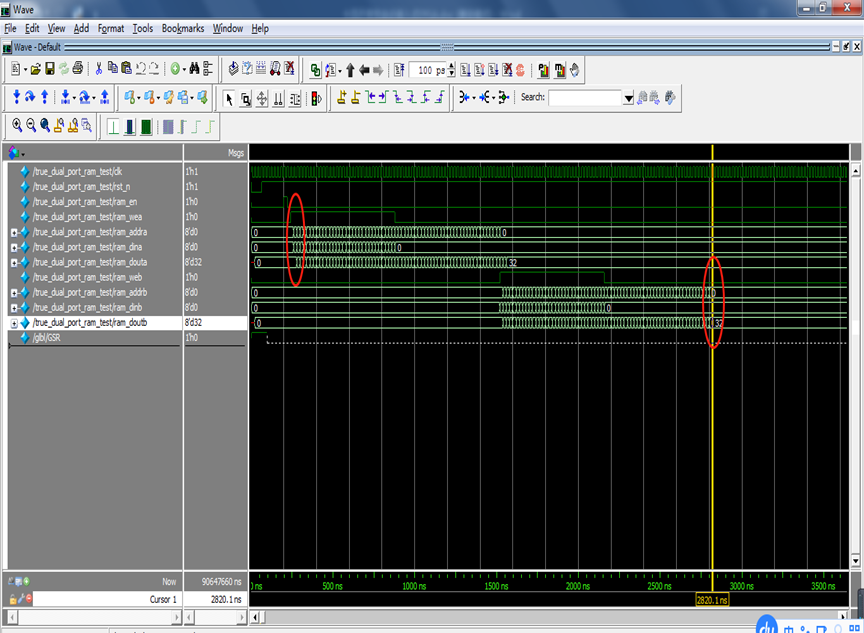

如图5真双口RAM IP核练习的输入信号激励设计,这里和单口RAM IP练习一样,只需要Testbench里给出模拟的ram_en使能信号即可。如图6所示是真双口RAM IP核练习的仿真结果,大家代入Modelsim后可以清楚地观察到,真双口RAM的两个端口均可以独立控制读写地址中的数据。

图1 真双口RAM IP核的内存类型配置

图2 真双口RAM IP核的端口A配置

图3 真双口RAM IP核的端口B配置

图4 真双口RAM IP练习的代码设计

图5 真双口RAM IP核练习的输入信号激励设计

图6 真双口RAM IP核练习的仿真结果

源工程代码下载链接:

链接:https://pan.baidu.com/s/15UnoNlERugOPGlJ9ROd1rA

提取码:rtgd

最后

以上就是喜悦衬衫最近收集整理的关于FPGA之RAM详解,真双口RAM的使用真双口RAM IP练习的全部内容,更多相关FPGA之RAM详解,真双口RAM的使用真双口RAM内容请搜索靠谱客的其他文章。

发表评论 取消回复