我是靠谱客的博主 大力小蚂蚁,这篇文章主要介绍XILINX Ultrascale+ FPGA学习(3)——多通道 高速12-bit ADC LVDS信号解串LVDS信号解串思路结果代码,现在分享给大家,希望可以做个参考。

LVDS信号

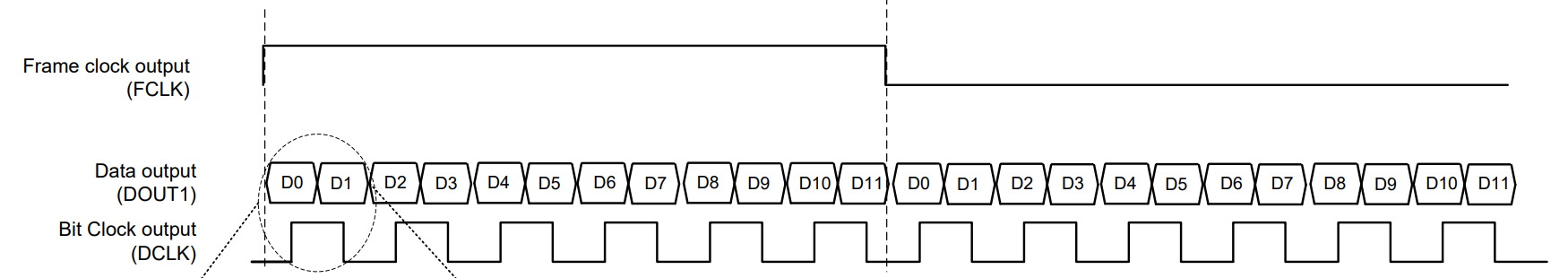

LVDS信号广泛的应用在高速传输中,下图是一个12位的ADC的输出LVDS信号,其中包括帧信号,数据时钟还有数据信号。

1个ADC输出两个通道或者4个通道的数据。 这里以2位为例子,帧信号的高位为奇通道,低位为偶通道

解串思路

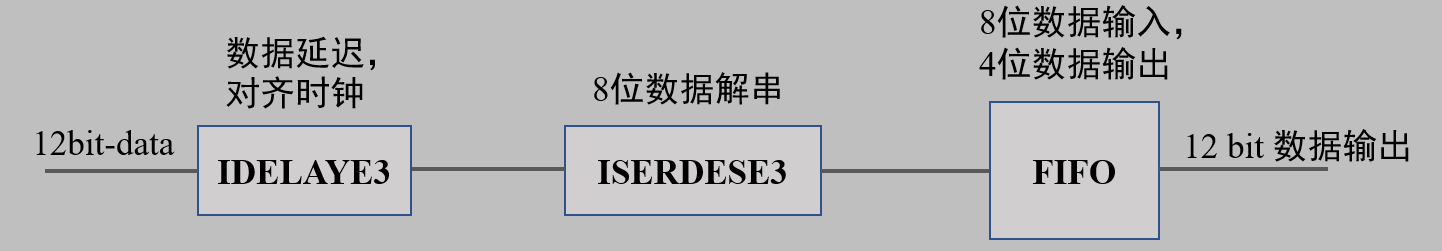

高速信号一般使用HP引脚,解串思路大概为:

ISERDESE3原语与ISERDESE2原语不一样,不再支持级联和bitship。我这里使用寄存器将数据重新整合位12bit,欢迎大佬提更好的办法~。

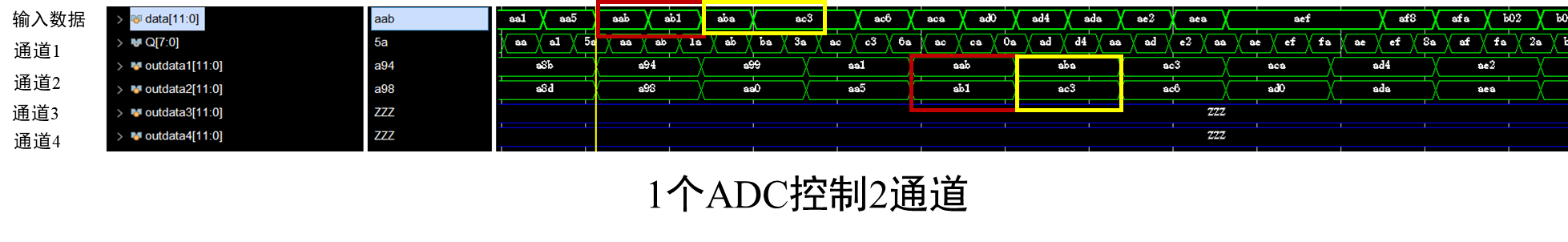

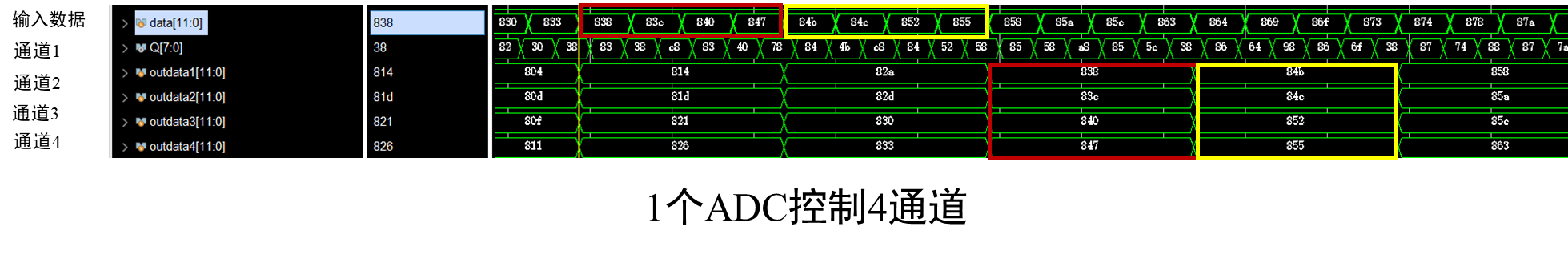

结果

代码中的TX_trig信号是同步信号,用来定义第一个采用的通道。

代码

`timescale 1ns / 1ps

//

module Decode_LVDS #(

parameter ADC_Sample_channel=4, // ADC Spamle channel,the value is 2 or 4.

parameter fc=66.66 //covert frequency of ADC

)(

input LVDS_data, //input data

input Dclk, //input data clock

input Fclk, //input data frame

input Delay_CLK, //delay clock

input rst, //input reset

input clk_decode, //input decode clock ,the triple of clock is Fclk ; this clock is generated by MMCMs or PLLs.

input rd_clk, //

input TX_trig, // synchronize clock, minimum 6 clk_decode

output wire[12*ADC_Sample_channel-1:0] LVDS_outdata, // the output of odd channel

output data_clk

);

localparam CLK_PER=1000/(6*fc); // the period of data clock (ns)

localparam DataDelay=((CLK_PER/4)*1000<=1100)?(CLK_PER/4)*1000:1100; // data delay 1/4 period of data clock

localparam [3:0] channel_nem=ADC_Sample_channel*3;

localparam [3:0] twi_channel=6;

localparam [3:0] qua_channel=12;

wire[7:0] Q;

wire data_delay;

wire fifo_wr_en;

wire fifo_rd_en;

wire [4:0] rd_data_count;

wire [3:0] wr_data_count;

wire empty;

wire counter_flag;

reg [4:0] Q_count;

reg WE;

reg WE1;

reg dataclk;

integer i;

wire [3:0]fifo1_out;

reg [3:0] data[channel_nem-1:0];

reg [11:0] outdata1;

reg [11:0] outdata2;

reg [11:0] outdata3;

reg [11:0] outdata4;

generate

case (ADC_Sample_channel)

4:

begin

assign LVDS_outdata[11:0]=outdata1;

assign LVDS_outdata[23:12]=outdata2;

assign LVDS_outdata[35:24]=outdata3;

assign LVDS_outdata[47:36]=outdata4;

end

default:

begin

assign LVDS_outdata[11:0]=outdata1;

assign LVDS_outdata[23:12]=outdata2;

end

endcase

endgenerate

assign data_clk=dataclk;

// delay data

IDELAYCTRL #(

.SIM_DEVICE("ULTRASCALE") // Set the device version for simulation functionality (ULTRASCALE)

)

IDELAYCTRL_inst (

.REFCLK(Delay_CLK), // 1-bit input: Reference clock input

.RST(rst) // 1-bit input: Active-High reset input. Asynchronous assert, synchronous deassert to

);

IDELAYE3 #(

.CASCADE("NONE"), // Cascade setting (MASTER, NONE, SLAVE_END, SLAVE_MIDDLE)

.DELAY_FORMAT("TIME"), // Units of the DELAY_VALUE (COUNT, TIME)

.DELAY_SRC("DATAIN"), // Delay input (DATAIN, IDATAIN)

.DELAY_TYPE("FIXED"), // Set the type of tap delay line (FIXED, VARIABLE, VAR_LOAD)

.DELAY_VALUE(DataDelay), // Input delay value setting

.IS_CLK_INVERTED(1'b0), // Optional inversion for CLK

.IS_RST_INVERTED(1'b0), // Optional inversion for RST

.REFCLK_FREQUENCY(400.0), // IDELAYCTRL clock input frequency in MHz (200.0-800.0)

.SIM_DEVICE("ULTRASCALE_PLUS"), // Set the device version for simulation functionality (ULTRASCALE,

// ULTRASCALE_PLUS, ULTRASCALE_PLUS_ES1, ULTRASCALE_PLUS_ES2)

.UPDATE_MODE("ASYNC") // Determines when updates to the delay will take effect (ASYNC, MANUAL,

// SYNC)

)

IDELAYE3_inst (

.DATAOUT(data_delay), // 1-bit output: Delayed data output

.CLK(Delay_CLK), // 1-bit input: Clock input

.DATAIN(LVDS_data), // 1-bit input: Data input from the logic

.RST(rst) // 1-bit input: Asynchronous Reset to the DELAY_VALUE

);

// decode from 12bit to 8 bit

ISERDESE3 #(

.DATA_WIDTH(8), // Parallel data width (4,8)

.FIFO_ENABLE("FALSE"), // Enables the use of the FIFO

.FIFO_SYNC_MODE("FALSE"), // Always set to FALSE. TRUE is reserved for later use.

.IS_CLK_B_INVERTED(1'b0), // Optional inversion for CLK_B

.IS_CLK_INVERTED(1'b0), // Optional inversion for CLK

.IS_RST_INVERTED(1'b0), // Optional inversion for RST

.SIM_DEVICE("ULTRASCALE_PLUS") // Set the device version for simulation functionality (ULTRASCALE, // ULTRASCALE_PLUS, ULTRASCALE_PLUS_ES1, ULTRASCALE_PLUS_ES2)

)

ISERDESE3_inst (

// disabled (do not connect)

.Q(Q), // 8-bit registered output

.CLK(Dclk), // 1-bit input: High-speed clock

.CLKDIV(clk_decode), // 1-bit input: Divided Clock

.CLK_B(~Dclk), // 1-bit input: Inversion of High-speed clock CLK

.D(data_delay), // 1-bit input: Serial Data Input

.RST(rst) // 1-bit input: Asynchronous Reset

);

fifo_generator_0 fifo1 (

.rst(rst), // input wire rst

.wr_clk(clk_decode), // input wire wr_clk

.rd_clk(rd_clk), // input wire rd_clk

.din(Q), // input wire [7 : 0] din

.wr_en(fifo_wr_en), // input wire wr_en

.rd_en(1'd1), // input wire rd_en

.dout(fifo1_out), // output wire [3 : 0] dout

.full(full), // output wire full

.empty(empty), // output wire empty

.rd_data_count(rd_data_count), // output wire [4 : 0] rd_data_count

.wr_data_count(wr_data_count), // output wire [3 : 0] wr_data_count

.wr_rst_busy(wr_rst_busy), // output wire wr_rst_busy

.rd_rst_busy(rd_rst_busy) // output wire rd_rst_busy

);

always @(posedge clk_decode)

begin

if(rst || TX_trig)

WE1<=1'd0;

else

if(WE & !TX_trig)

WE1<=1'd1;

end

assign counter_flag=(fifo_wr_en & !empty)?1'd1:1'd0;

assign fifo_wr_en=(WE1)?1'd1:1'd0;

always @(posedge Fclk)

begin

if(rst || TX_trig)

WE<=1'd0;

else if(!TX_trig)

WE<=1'd1;

end

always@(posedge rd_clk)

begin

if(rst || (!rst && TX_trig))

begin

Q_count<=4'd0;

outdata1<=12'dz;

outdata2<=12'dz;

outdata3<=12'dz;

outdata4<=12'dz;

dataclk<=1'd0;

for(i=0;i<=channel_nem;i=i+1)

data[i] <= 4'd0;

end

else

if(!TX_trig)

begin

if(Q_count>=1'd1)

data[Q_count-1]<=fifo1_out;

if(counter_flag)

if(Q_count<channel_nem)

Q_count<=Q_count+1'd1;

else

Q_count<=1'd1;

end

if((Q_count==1'd1) && WE)

begin

case(channel_nem)

twi_channel: begin

outdata1<={data[3],data[0],data[1]};

outdata2<={data[4],data[5],data[2]};

dataclk<=~dataclk;

end

qua_channel: begin

begin

outdata1={data[3],data[0],data[1]};

outdata2={data[4],data[5],data[2]};

outdata3={data[9],data[6],data[7]};

outdata4={data[10],data[11],data[8]};

dataclk<=~dataclk;

end

end

default:

begin

outdata1<=12'dz;

outdata2<=12'dz;

outdata3<=12'dz;

outdata4<=12'dz;

end

endcase

end

end

endmodule

最后

以上就是大力小蚂蚁最近收集整理的关于XILINX Ultrascale+ FPGA学习(3)——多通道 高速12-bit ADC LVDS信号解串LVDS信号解串思路结果代码的全部内容,更多相关XILINX内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复