一、异步复位易造成输出为亚稳态(即输出不稳定)

如果异步复位信号释放时间和时钟的有效沿到达时间几乎一致,则容易造成触发器输出为亚稳态,形成逻辑错误。

了解几个概念。

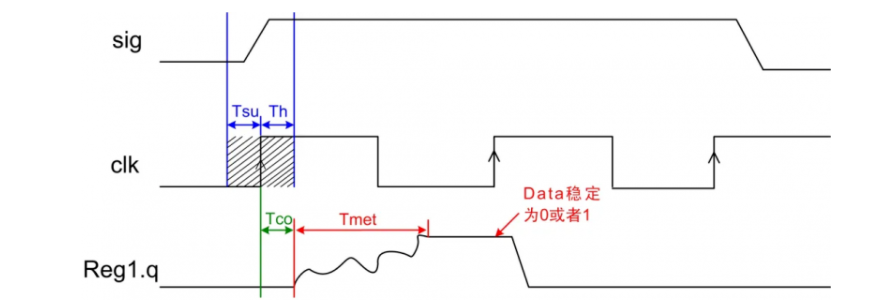

1)亚稳态(metastability):此时触发器输出端 Q 在有效时钟沿之后比较长的一段时间处于不确定的状态,在这段时间里 Q 端在 0 和 1 之间处于振荡状态,而不是等于数据输入端 D 的值。这段时间称为决断时间(resolution time),最终稳定到“0”或者“1”。

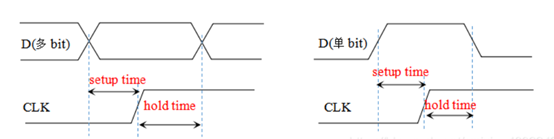

2)同步信号中的建立时间(SetupTime/Tsu)和保持时间(Hold time/Th)

建立时间是指在时钟边沿前,数据信号需要保持不变的时间。

保持时间是指时钟跳变边沿后数据信号需要保持不变的时间。

如果数据信号在时钟沿触发前后持续的时间均超过建立和保持时间,那么超过量就分别被称为建立时间裕量和保持时间裕量。

图1 建立时间和保持时间

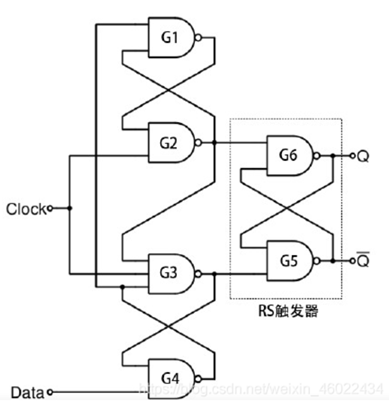

需要满足建立时间(SetupTime)和保持时间(Hold time)的原因:与D触发器内部结构有关。

图2:D触发器的内部结构

输入信号在到达G2和G3之前经过了G1和G4的延迟,建立时间就是为了补偿信号在G1和G4上的延迟。也就是数据在时钟沿来临之前,需要足够的建立时间让信号经过G1和G4到达G2和G3。

上升沿来临时,数据通过G2和G3传输至后面的RS触发器,但G2和G3也会存在延时,保持时间就是为了补偿信号在G2和G3上的延迟。也就是数据在时钟沿来临之后,需要足够的保持时间让信号正确的从G2和G3传输至RS触发器。

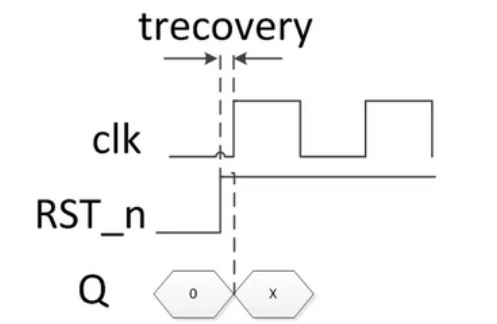

3)异步信号中的恢复时间(recovery time)和撤销时间(removal time)

恢复时间 recovery time : 对于异步信号(比如异步复位/置位),信号变无效的边沿和下一个时钟沿之间必须满足一个最小的间隔。如果保证不了这个最小时间,也就是异步信号无效边离时钟边沿太近了,异步信号解除(无效)之后,没有给 DFF 足够的时间来恢复(recovery)到正常状态,那么就不能保证在时钟沿到来时 DFF 可以正常工作。

即异步复位信号释放(对低电平有效的复位来说就是上升沿)与紧跟其后的第一个时钟有效沿之间,有一个必须间隔的最小时间,称为恢复时间。

图3 恢复时间

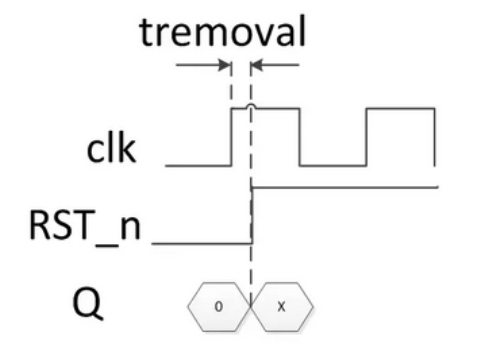

撤销时间 removal time : 对于异步信号(比如异步复位/置位),信号变有效的边沿和前一个时钟沿之间必须满足一个最小的间隔。如果保证不了这个最小时间,也就是异步信号的有效沿离时钟太近了,在时钟信号去除(无效)之前,异步信号提前有效了,可能会造成 DFF 处于不确定状态。

即时钟有效沿与紧跟其后的异步复位信号释放之间所必须间隔的最小时间称为撤销时间。

图4 撤销时间

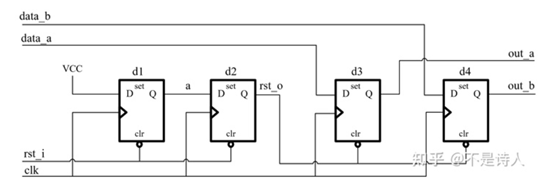

二、如何防止复位信号撤除时产生亚稳态事件(异步复位,同步释放)

用两级D触发器做两级同步器,对异步复位进行同步,得到了根复位信号之后,再对其用复位同步电路进行分发。

用d1,d2产生一个信号rst_o,用做电路的复位信号。

假设在d1输出产生了亚稳态,由于亚稳态的时间较短,可能在下一个clk上升沿来之前就进入了稳定状态,所以d2的输出是稳定的且已经被同步了。(当然如果在下一个clk上升沿来之前d1还是亚稳态,则d2也会进入亚稳态,但这种概率比较小。随着D触发器个数的增加亚稳态产生的概率是成平方倍的减少的,在大部分的同步化设计中,两级同步器足以消除所有可能的亚稳态了)

此处我不理解的地方是d1和d2的复位和时钟信号都是同一个,难道d2不会产生亚稳态吗(请大佬们指教)

图5

下面分析一下上述电路:

当rst_i=0时,Q1,Q2被清0,rst_o=0, 使Q3,Q4也被清零,实现异步复位。

当rst_i由0到1时,在第一个clk上升沿来时,Q1<=VCC, Q2<=Q1(此处是非阻塞赋值),所以Q1=1, Q2=0,rst_0=0,Q3,Q4仍处于清零状态,直到下一个clk上升沿到来,Q2=1,rst_o=1,实现了同步释放,由于此时rst_o上升沿与clk同步,不会产生亚稳态。

下面附上Verilog代码:

module sync_async_reset (

input clk,

input rst_i,

input data_a,

input data_b,

output out_a,

output out_b

);

reg Q1,Q2;

reg Q3, Q4;

assign out_a = Q3;

assign out_b = Q4;

assign rst_o = Q2;

always @ (posedge clock, negedge rst_i) begin

if (!rst_i) begin

Q1 <= 1'b0;

Q2 <= 1'b0;

end

else begin

Q1 <= 1'b1;

Q2 <= Q1;

end

end

always @ (posedge clock, negedge rst_o) begin

if (!rst_o) begin

Q3 <= 1'b0;

Q4 <= 1'b0;

end

else begin

Q3 <= data_a;

Q4 <= data_b;

end

end

endmodule

参考:

1、异步复位同步释放_异步复位,同步释放

2、FPGA中复位电路产生亚稳态概述与理论分析

3、Setup Time 、Hold Time、Setup check、Hold check,同步异步 及违例修复

最后

以上就是秀丽外套最近收集整理的关于异步复位和同步释放问题的全部内容,更多相关异步复位和同步释放问题内容请搜索靠谱客的其他文章。

发表评论 取消回复