一、什么是同步清零?什么是异步清零?两者的区别是什么?

-

同步复位是指复位信号只有在时钟沿到来时,才能有效。否则,无法完成对系统的复位工作。

-

异步复位是指无论时钟沿是否到来,只要复位信号有效,就对系统进行复位。

-

同步复位的复位信号持续的时间应该超过一个时钟周期才能保证系统复位。异步复位抗干扰能力差,有些噪声也能使系统复位,因此有时候显得不够稳定,要想设计一个好的复位最好使用异步复位同步释放,而且复位信号低电平有效。

二、异步清零的设计

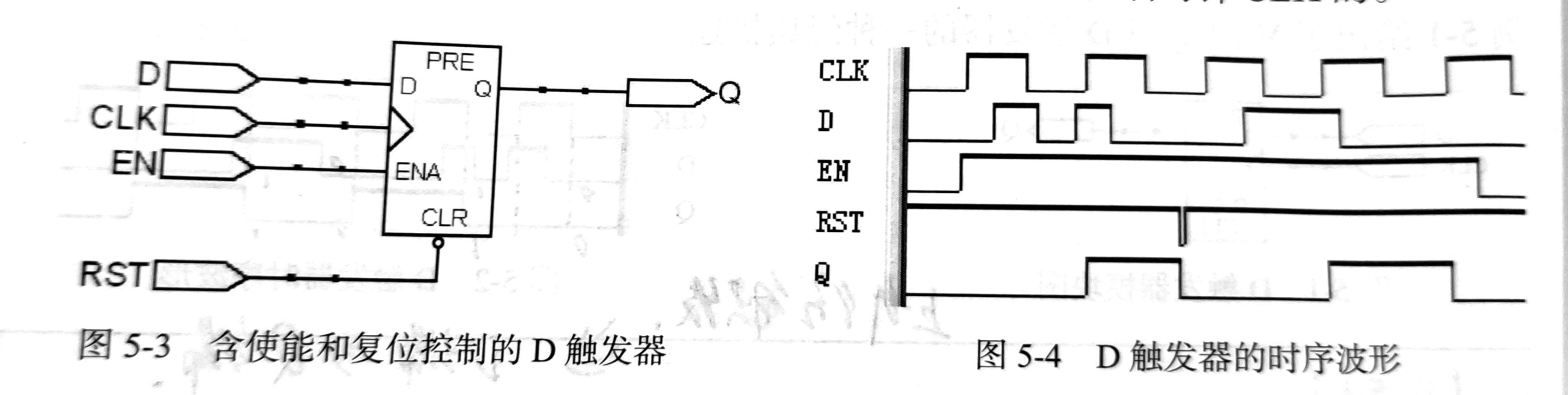

以D触发器为例,标准模块如图5-3所示,时序图如图5-4所示。

有数据端D、时钟端CLK、输出端Q、异步复位端RST和时钟使能端EN。

module DFF2(CLK, D, Q,RST, EN);

input CLK, D, RST, EN;

output Q;

reg Q;

always @(posedge CLK or negedge RST)

begin

if(!RST)

Q <= 0;

else if(EN)

Q <= D;

end

endmodule

程序执行过程:

无论CLK是否跳变,只要RST有一个下降沿的动作,即刻启动过程,执行if语句。此时RST=0,因此满足条件(!RST)=1,于是执行语句Q<=0,对Q清0,然后跳出if语句。此时如果RST一直保存为0,则无论是否有CLK的边沿跳变信号,Q恒输出0,这就是RST的异步清0功能。

若RST一直为1,且CLK有一次上升沿(要求此时EN = 1),则必定执行赋值操作Q<=D,从而更新Q值,否则(CLK无上升沿)将保持Q值不变。

三、同步清零的设计

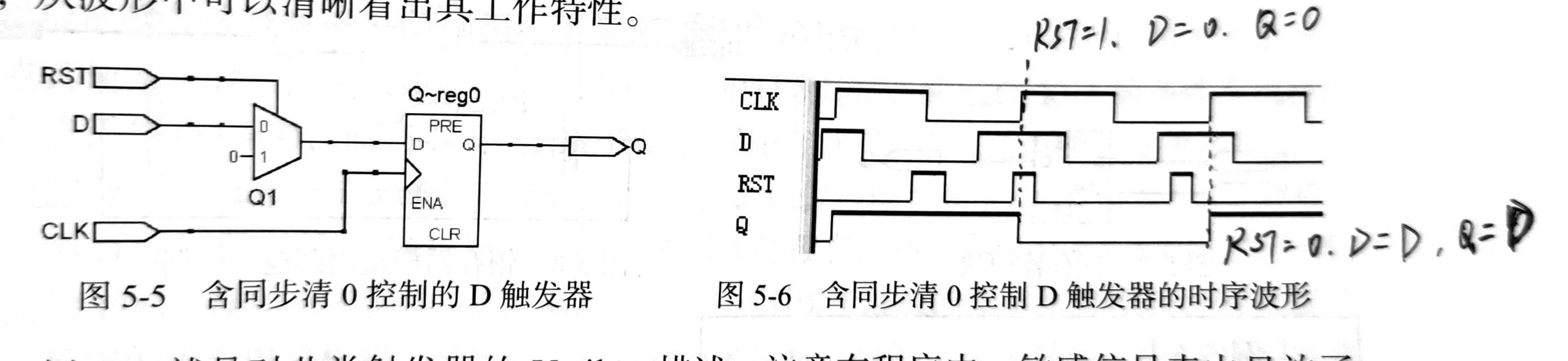

图5-5所示的就是一个含同步清0的D触发器电路,时序图如图5-4所示。

即在输入端口D处加了一个2选1多路选择器。

module DFF3(CLK, D, Q, RST);

input CLK, D, RST;

output Q;

reg Q;

always @(posedge CLK)

begin

if(RST == 1)

Q = 0;

else if(RST == 0)

Q = D;

end

endmodule

工作时,当RST=1时,选通“1”端的数据0,使0进入触发器的D输入端。如果这时CLK有一个上升沿,便将此0送往输出端Q,这就实现了同步清0的功能;

而当RST=0时,则选通“0”端的数据D,使数据D进入触发器的D输入端,然后Q = D。

注意在程序中,敏感信号表中只放了对CLK上升沿的敏感表述。这就表明,此过程中的所有其他输入信号都随时钟CLK而同步。

最后

以上就是粗心鸵鸟最近收集整理的关于EDA技术实用教程 | 复习七 | 异步清零和同步清零的时序设计的全部内容,更多相关EDA技术实用教程内容请搜索靠谱客的其他文章。

发表评论 取消回复