描述

题目描述:

请使用异步复位同步释放来将输入数据a存储到寄存器中,并画图说明异步复位同步释放的机制原理。

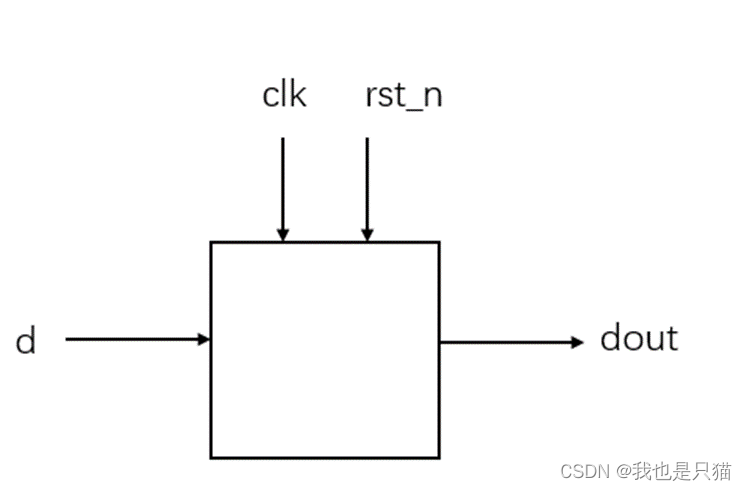

信号示意图:

clk为时钟

rst_n为低电平复位

d信号输入

dout信号输出

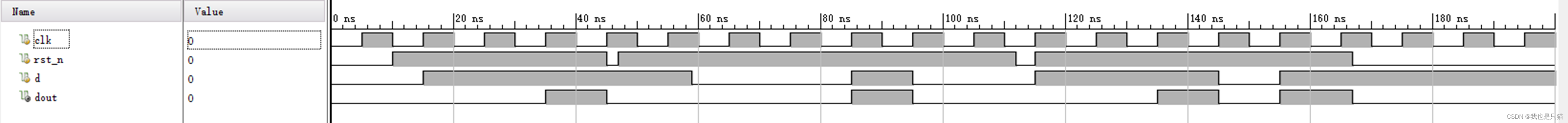

波形示意图:

输入描述:

clk为时钟

rst_n为低电平复位

d信号输入

输出描述:

dout信号输出

1、确定题目要求

复位可以在任何时候发生,表面上看跟时钟没有关系,但真实情况是异步复位也需考虑时钟跳变沿,因为时钟沿变化和异步复位都可以引起Q端数据变化。同步复位虽然解决了当时钟的有效沿来临的时候rst的边沿也正好来临所出现的冒险与竞争。但是从综合的电路上可以看出,多了一个组合逻辑MUX。如果设计中所有的复位都是这样的,那会增加很多的资源,导致芯片面积很大,而异步复位同步释放机制可以解决这一问题。

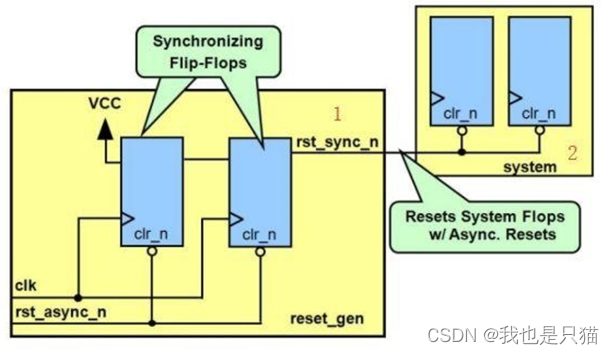

异步复位同步释放的主要目的就是在减少资源损耗的同时避免毛刺的出现。其机制如下:

异步复位会出现亚稳态是因为无法保证clk的上升沿时,rst释放信号能够满足其建立保持时间,触发器无法判断rst有效还是无效,因而出现亚稳态;而同步释放的处理机制可以保证rst释放信号的建立时间点与clk的posedge同步,在当前clk的posedge检测到rst稳定的低电平,在下一个clk的posedge可以检测到已经稳定的rst高电平,满足了rst的建立保持时间要求,从而不会出现亚稳态。

所谓“异步复位”是针对D触发器的复位端口,它是异步的,所谓“同步释放”,实际上是由于设计了同步逻辑电路,外部复位信号不会在出现释放时与clk信号竞争,整个系统将与全局时钟clk信号同步。

module ali16(

input wire clk,

input wire rst_n,

input wire d,

output reg dout

);

reg rst0,rst1;

always @ (posedge clk or negedge rst_n) begin

if (!rst_n) begin

rst0 <= 0;

rst1 <= 0;

end

else begin

rst0 <= 1;

rst1 <= rst0;

end

end

always @ (posedge clk or negedge rst1)begin

if(!rst1) begin

dout <= 1'b0;

end

else begin

dout <= d;

end

end

endmodule最后

以上就是魁梧大神最近收集整理的关于同步复位异步释放的全部内容,更多相关同步复位异步释放内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复