文章目录

(一)半加器

(二)作业题:半减器

(三)全加器

(四)作业题:全减器

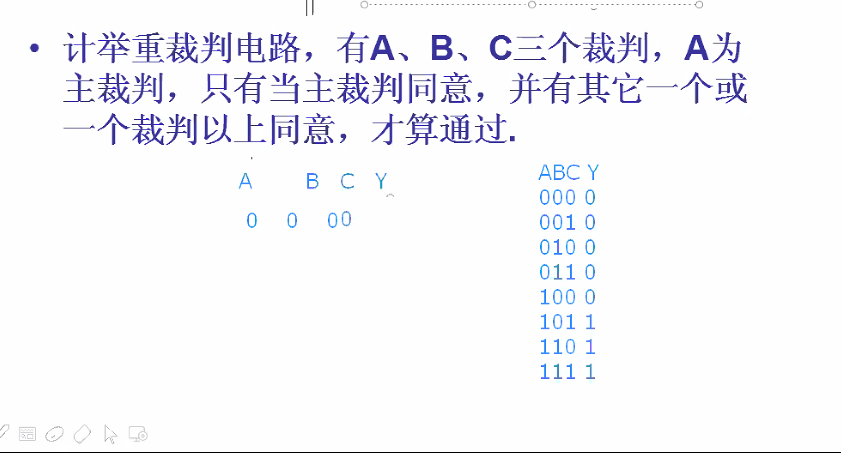

(五)作业题:举重裁判电路

(六)作业题:一个电路有32位输入,该电路输出输入端口1的个数

(七)含异步清0和同步使能控制的D触发器

(八)含同步清0的D触发器

(九)含同步清0的D触发器例题(考试考同步)

(十)作业题:用verilog实现上面的D触发器电路

(十一)16进制计数器

(十二)作业题:60进制计数器

(十三)作业题:设计一个2分频的分频器

(十四)作业题:用Verilog描述下列状态机

(十五)作业题:编写一个执行10位二进制向量做算术移位的函数

(十六)作业题:编写一个VerilogHDL仿真用程序

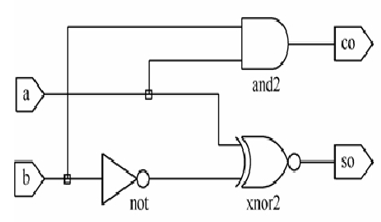

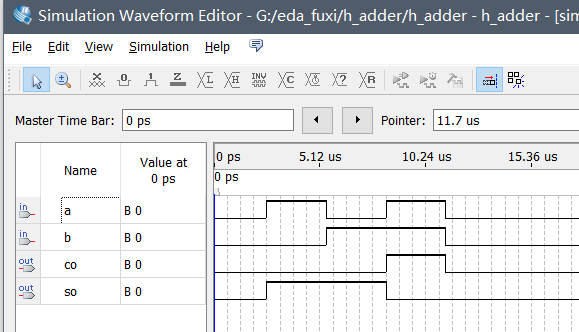

(一)半加器

| a | b | so(结果位) | co(进位位) |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 1 |

module h_adder(a,b,co,so);

output co,so;

input a,b;

assign so=a^b;//异或

assign co=a&b;//与门

endmodule

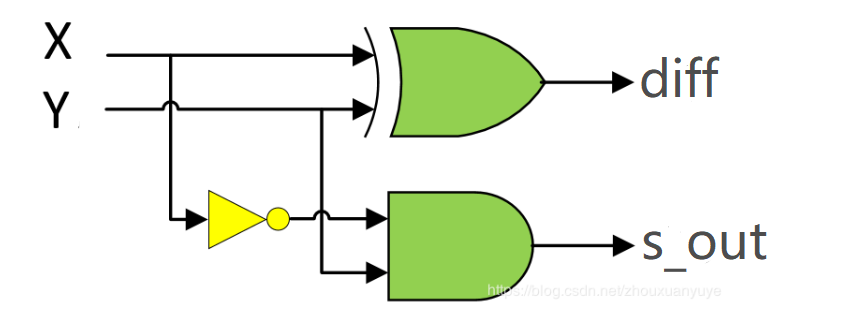

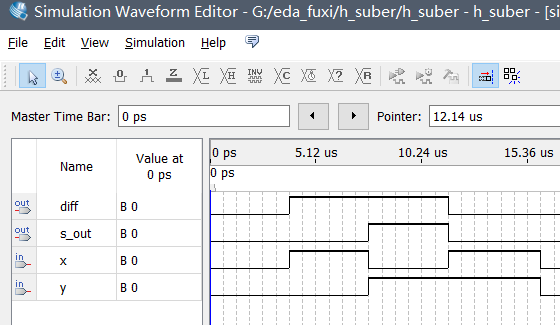

(二)作业题:半减器

| x | y | diff(结果位) | s_out(借位位) |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 1 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

module h_suber(x,y,diff,s_out);

output diff,s_out;

input x,y;

assign diff=x^y;

assign s_out=(~x)&y;

endmodule

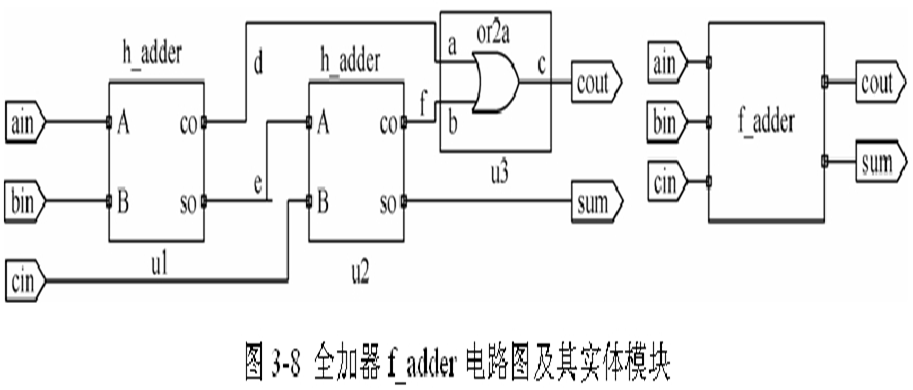

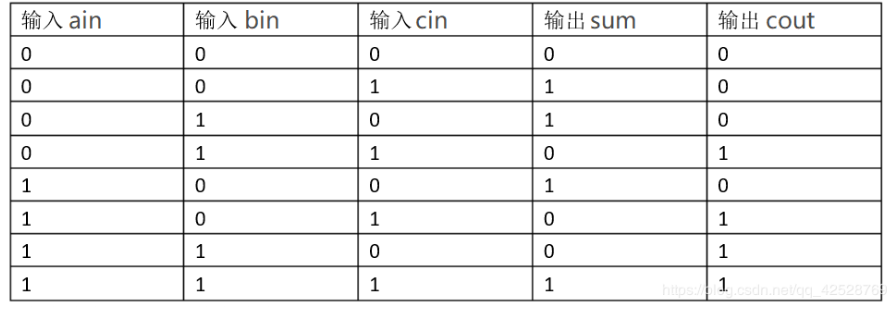

(三)全加器

利用半加器和或门实现全加器

半加器代码如下:

module h_adder(a,b,co,so);

output co,so;

input a,b;

assign so=a^b;//异或

assign co=a&b;//与门

endmodule

或门代码如下:

module or2a(a,b,c);

output c;

input a,b;

assign c=a|b;

endmodule

全加器代码如下:

module f_adder(ain,bin,cin,cout,sum);

output sum,cout;

input ain,bin,cin;

wire d,e,f;

h_adder u1(.a(ain),.b(bin),.co(d),.so(e));

h_adder u2(.a(e),.b(cin),.co(f),.so(sum));

or2a u3(.a(d),.b(f),.c(cout));

endmodule

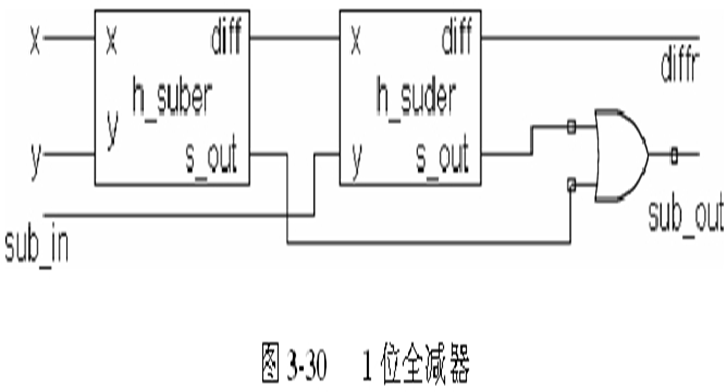

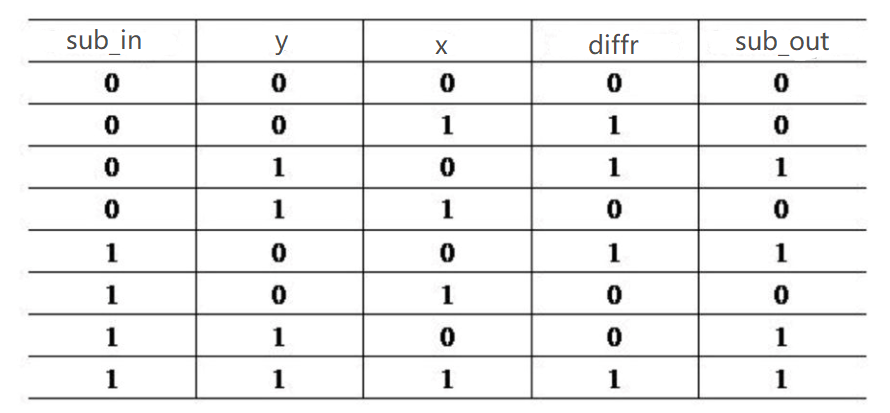

(四)作业题:全减器

利用半减器和或门实现全减器

半减器代码如下:

module h_suber(x,y,diff,s_out);

output diff,s_out;

input x,y;

assign diff=x^y;

assign s_out=(~x)&y;

endmodule

全减器代码如下:

module f_suber(x,y,sub_in,diffr,sub_out);

output diffr,sub_out;

input x,y,sub_in;

wire e,f,g;

h_suber u1(.x(x),.y(y),.diff(e),.s_out(g));

h_suber u2(.x(e),.y(sub_in),.diff(diffr),.s_out(f));

assign sub_out=f|g;

endmodule

(五)作业题:举重裁判电路

解法一:

module judge(A,B,C,Y);

input A,B,C;

output Y;

reg Y;

always@(A or B or C or Y)

begin

case({A,B,C})

3'b000:Y<=0;

3'b001:Y<=0;

3'b010:Y<=0;

3'b011:Y<=0;

3'b100:Y<=0;

3'b101:Y<=1;

3'b110:Y<=1;

3'b111:Y<=1;

default:Y<=0;

endcase

end

endmodule

解法二:

module judge(A,B,C,Y);

input A,B,C;

output Y;

reg Y;

always@*

casex({A,B,C})

3'B0ZZ,3'B100:Y=0;

3'B101,3'B110,3'B111:Y=1;

default:Y=0;

endcase

endmodule

(六)作业题:一个电路有32位输入,该电路输出输入端口1的个数

module count1(int,out);

input [31:0] int;

output [5:0] out;

reg [5:0] i,out;

always @(int)

begin

out=0;

for(i=1;i<33;i=i+1)

if((int>>i)%2==1)

out=out+1;

end

endmodule

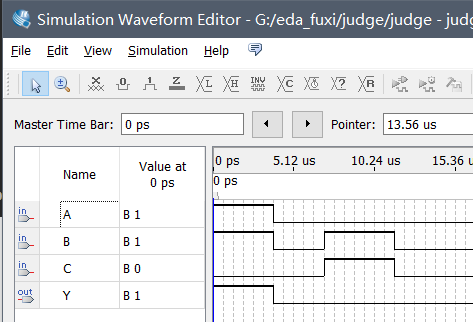

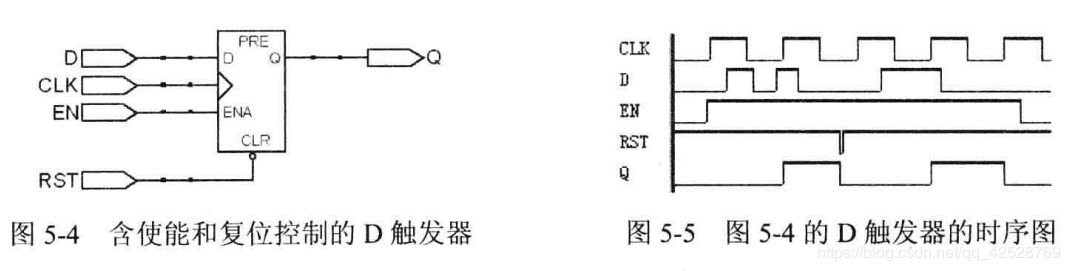

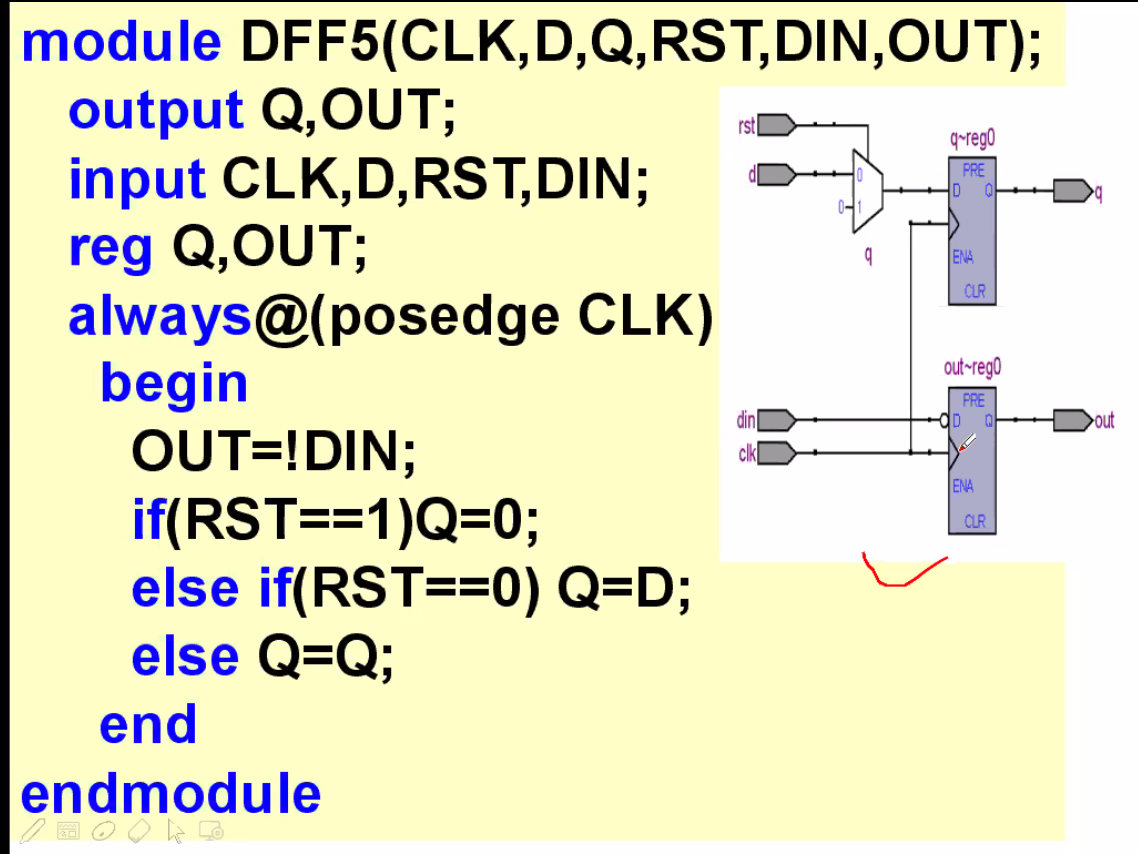

(七)含异步清0和同步使能控制的D触发器

module DFF2_yibu(clk,d,q,rst,en);

output q;

input clk,d,rst,en;

reg q;//要赋值,必须是reg类型(寄存器类型)

always@(posedge clk or negedge rst)

begin

if(!rst) q<=0;

else if(en) q<=d;//只有en使能了,才赋新值(到了这一步,说明rst=1)

end

endmodule

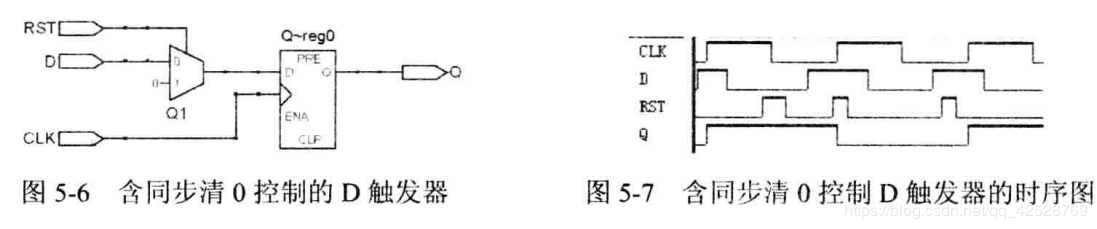

(八)含同步清0的D触发器

module DFF2_tongbu(clk,d,q,rst);

output q;

input clk,d,rst;

reg q;

always@(posedge clk)//默认是上升沿

begin

if(rst) q<=0; //如果rst=1,输出恒为0,相当于清0

else q<=d;

end

endmodule

(九)含同步清0的D触发器例题(考试考同步)

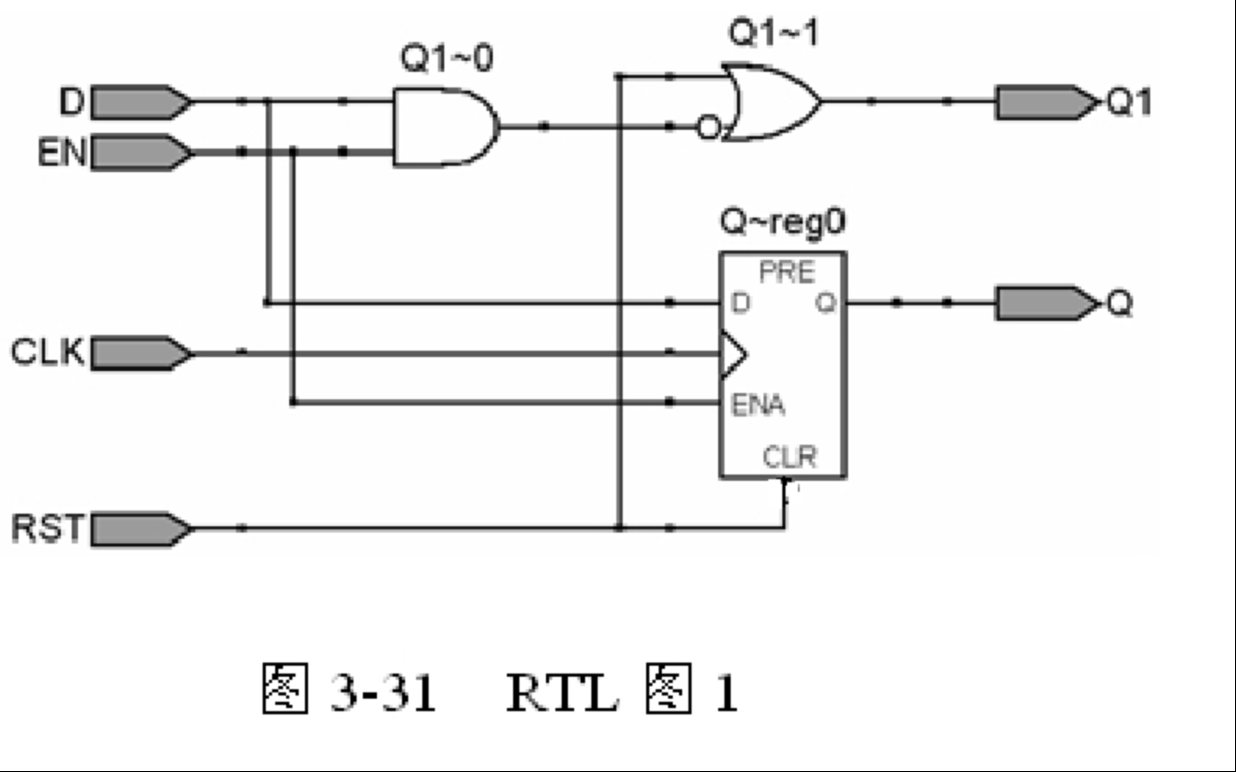

(十)作业题:用verilog实现上面的D触发器电路

module DFF2(d,en,clk,rst,q1,q);

output q1,q;

input d,en,clk,rst;

reg q;

wire n;

assign n=d&en;

assign q1=(~n)|rst;

always@(posedge clk or posedge rst)

begin

if(rst) q<=0;

else if(en) q<=d; //来到这一步,说明上面的if语句不成立

end

endmodule

(十一)16进制计数器

说明:16进制计数器(0000~1111)

注意:计数器不需要赋初值,如果初值是1001 就变成1010(无论如何都是在16个状态内循环)

module cnt16(clk,q);

input clk;

output [3:0]q;

reg [3:0]qq;

always@(posedge clk)

qq<=qq+1;

assign q=qq;

endmodule

由于计数器不受控,我们通常加一个异步清零(rst)和同步使能(en)等等去加以控制

其中load为装载信号,d为需要被装载的值

我们假设控制信号(load、en和rst)均高电平有效、load优先级高于en的优先级

module cnt16(clk,q,rst,en,load,d);

input clk,rst,en,load;

input [3:0]d;

output [3:0]q;

reg [3:0]qq;

always@(posedge clk,posedge rst)

if(rst) qq<=0;

else if(load) qq<=d;

else if(en) qq<=qq+1;

else qq<=qq; (en使能信号没有使能,只能保持原样了)

assign q=qq;

endmodule

加上溢出信号

module cnt16(clk,q,rst,en,load,d,count);

input clk,rst,en,load;

input [3:0]d;

output [3:0]q;

output count;

reg [3:0]qq;

always@(posedge clk,posedge rst)

if(rst) qq<=0;

else if(load) qq<=d;

else if(en) qq<=qq+1;

else qq<=qq;

assign q=qq;

assign count=(qq==4'b1111);

endmodule

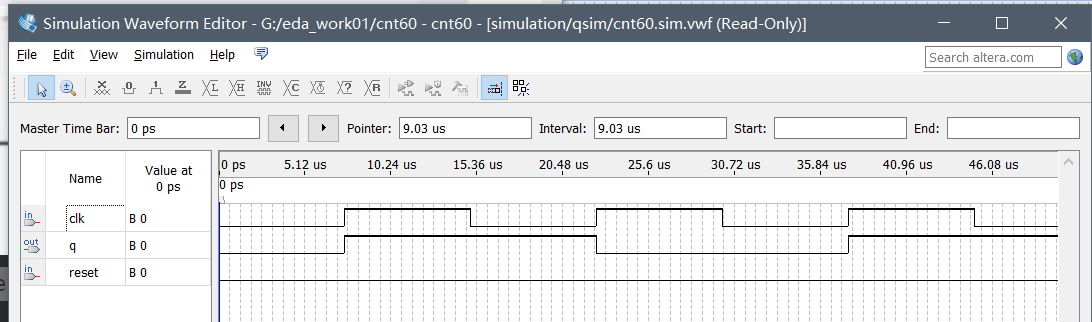

(十二)作业题:60进制计数器

我们最好是加上count

刚才的16进制计数器因为4个1刚好是15,所以无需加以判断,但是6个1并不等于59

module cnt60(clk,q,rst,en,load,d,count);

input clk,rst,en,load;

input [5:0]d;

output [5:0]q;

output count;

reg [5:0]qq;

always@(posedge clk,negedge rst)

if(!rst) qq<=0;

else if(!load) qq<=d;

else if(!en)

if(qq<59) qq<=qq+1;

else qq<=0;

else qq<=qq;

assign q=qq;

assign count=(qq==6'b111011);

endmodule

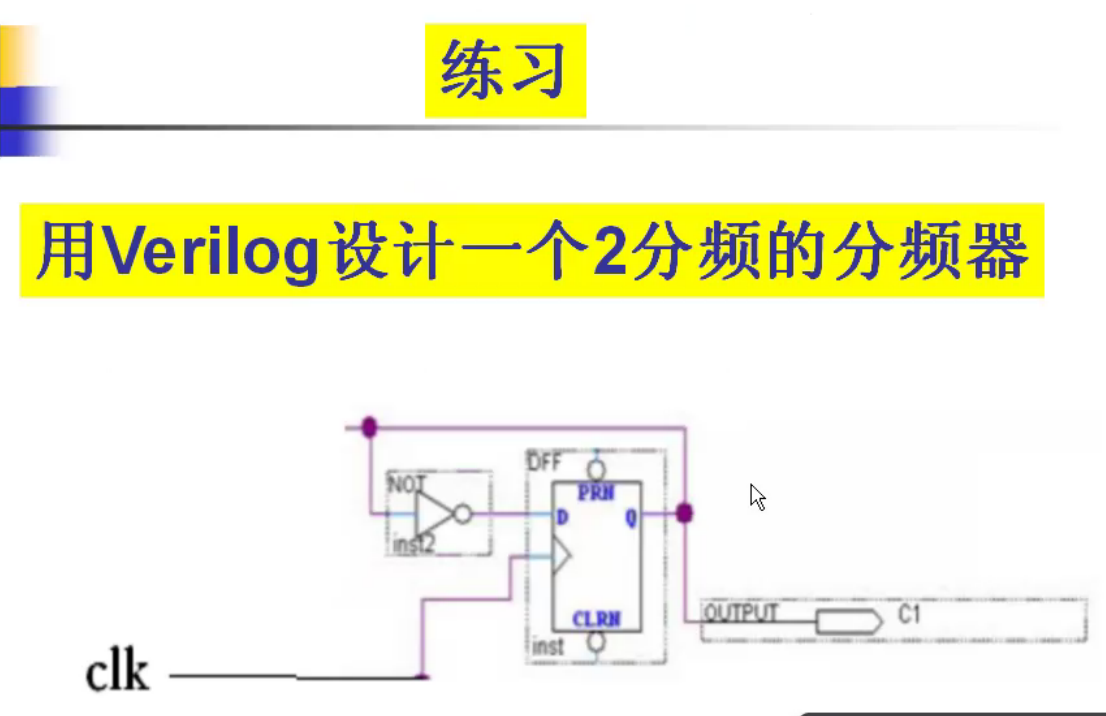

(十三)作业题:设计一个2分频的分频器

module div_2(q,clk,reset);

output q;

input reset;

input clk;

reg q;

always@(posedge clk or posedge reset)

if(reset)

q<=1'b0;//复位置零

else

q<=~q;//否则q信号翻转

endmodule

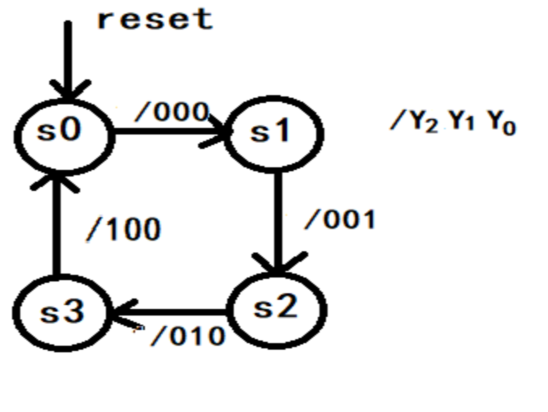

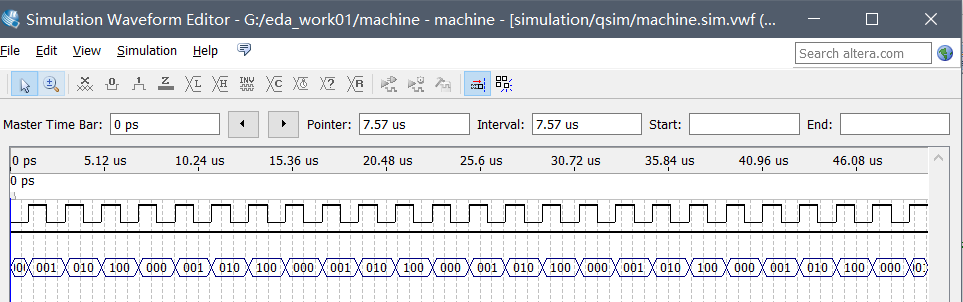

(十四)作业题:用Verilog描述下列状态机

module machine(clk,rst,y);

parameter s0=0,s1=1,s2=2,s3=3;

reg[1:0] c_state,n_state;

input clk,rst;

output[2:0] y;

reg[2:0] y;

always @(posedge clk,negedge rst)

if(!rst) c_state <= s0;

else c_state <= n_state;

always @(*)

case(c_state)

s0: begin n_state = s1; y = 3'b000; end

s1: begin n_state = s2; y = 3'b001; end

s2: begin n_state = s3; y = 3'b010; end

s3: begin n_state = s0; y = 3'b100; end

default: begin n_state = s0; y = 3'b000; end

endcase

endmodule

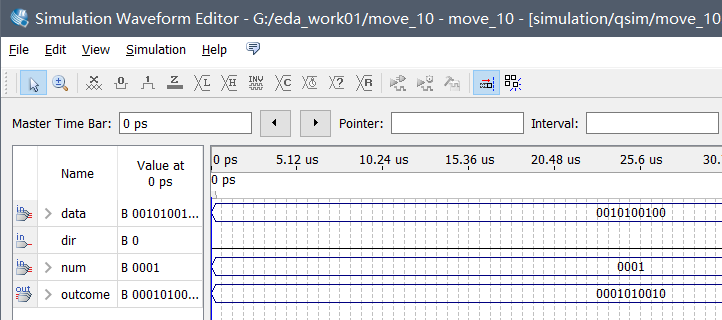

(十五)作业题:编写一个执行10位二进制向量做算术移位的函数

module move_10(data,dir,num,outcome);

input[9:0] data;

input dir;

input[3:0] num;

output[9:0] outcome;

function[9:0] move;

input[9:0] data;

input dir;

input[3:0] num;

reg[9:0] data;

if(dir)

move = data << num;

else

move = data >> num;

endfunction

assign outcome = move(data,dir,num);

endmodule

(十六)作业题:编写一个VerilogHDL仿真用程序

要求输出时钟激励信号clk,周期为50ns,产生一个RST复位激励信号,要求RST信号在仿真开始保持低电平,过150ns变为高电平,再过100ns恢复为低电平,产生一个EN信号,开始保持高电平,过700ns变为低电平,再过100ns变为高电平。用这些激励信号测试一个计数器。

`timescale 10ns/1ps

module CNT_tb;

reg clk,RST,EN;

wire[3:0] q;

initial

begin

clk = 0;

foreve #2.5 clk = ~clk;

end

initial

begin

RST = 0;

EN = 1;

#15 RST=1;

#10 RST=0;

#45 EN=0;

#10 EN=1;

#10 $stop;

end

CNT CNT(.clk(clk),.RST(RST),.EN(EN),.q(q);

endmodule

module CNT(clk,RST,EN,q);

input clk,RST,EN;

output reg[3:0] q;

always@(posedge clk,posedge RST)

begin

if(RST) q<=0;

else if(!EN) q<=q;

else q<=q+1;

end

endmodule

最后

以上就是活力过客最近收集整理的关于EDA/Verilog期末考试复习资料文章目录(一)半加器(二)作业题:半减器(三)全加器(四)作业题:全减器(五)作业题:举重裁判电路(六)作业题:一个电路有32位输入,该电路输出输入端口1的个数(七)含异步清0和同步使能控制的D触发器(八)含同步清0的D触发器(九)含同步清0的D触发器例题(考试考同步)(十)作业题:用verilog实现上面的D触发器电路(十一)16进制计数器(十二)作业题:60进制计数器(十三)作业题:设计一个2分频的分频器(十四)作业题:用Verilog描述下列状态机(十的全部内容,更多相关EDA/Verilog期末考试复习资料文章目录(一)半加器(二)作业题:半减器(三)全加器(四)作业题:全减器(五)作业题:举重裁判电路(六)作业题:一个电路有32位输入,该电路输出输入端口1内容请搜索靠谱客的其他文章。

发表评论 取消回复