(如果有错希望大佬告知,谢谢)

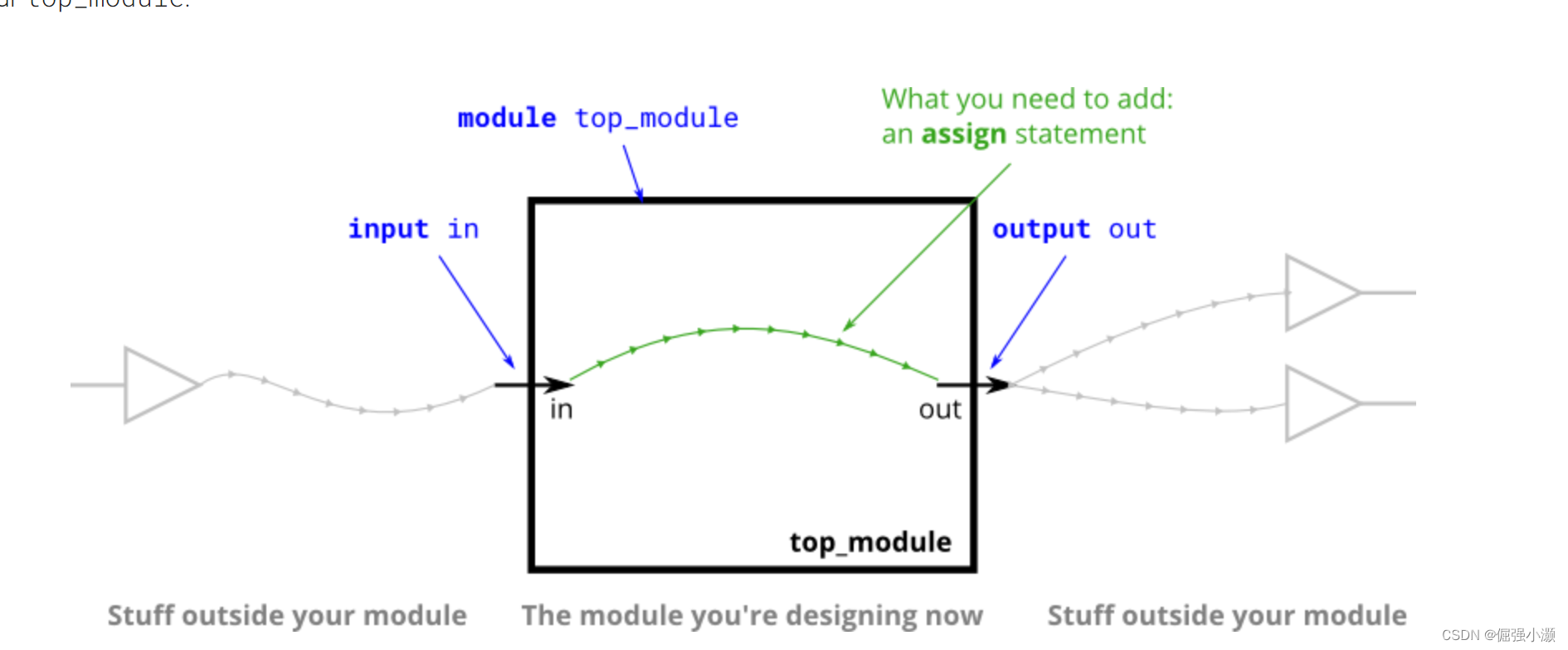

(第一题)Create a module with one input and one output that behaves like a wire.

Unlike physical wires, wires (and other signals) in Verilog are directional. This means information flows in only one direction, from (usually one) source to the sinks (The source is also often called a driver that drives a value onto a wire). In a Verilog "continuous assignment" (assign left_side = right_side;), the value of the signal on the right side is driven onto the wire on the left side. The assignment is "continuous" because the assignment continues all the time even if the right side's value changes. A continuous assignment is not a one-time event.

刚入门我是看图片的,但是小萌新还是的吧英文读一读(我读了)。目前我还看不懂波形图,今天是第一天学写代码,(可能日后就有介绍了)

assign在verilog语言中一般用于连接两个变量,将一个变量的值不断赋值给另一个变量类似一个导线。

module top_module( input in, output out );

assign out=in;

endmodule

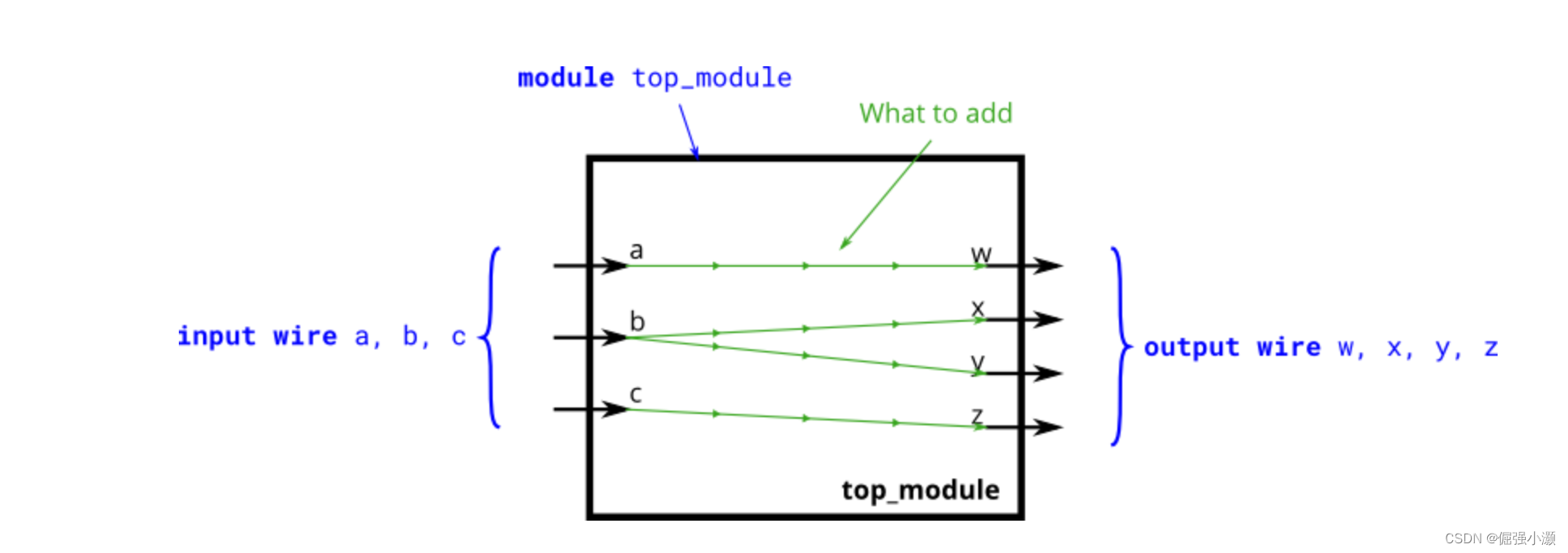

Create a module with 3 inputs and 4 outputs that behaves like wires that makes these connections:

a -> w b -> x b -> y c -> z

(第二题)The diagram below illustrates how each part of the circuit corresponds to each bit of Verilog code. From outside the module, there are three input ports and four output ports.

When you have multiple assign statements, the order in which they appear in the code does not matter. Unlike a programming language, assign statements ("continuous assignments") describe connections between things, not the action of copying a value from one thing to another.

初步阶段,看图差不多就可以看懂,跟第一题一样都是简单的输入输出。

但是这个这个题有新的词wire。

verilog中的wire数据类型,可以看成是定义在模块内部的导线。(网上说的)

大体简单的代码就是这样吧。

module top_module(

input a,b,c,

output w,x,y,z );

assign w=a;

assign x=b,y=b,z=c;

endmodule

(3-5)

这几个题都是数电讲过的与或非

与(and):全一为一

或(or):全0是0 ;

非(~):字面意思就是取反

第三题取反

module top_module( input in, output out );

assign out=~in;

endmodule第四题 取与

module top_module(

input a,

input b,

output out );

and u1(out,a,b);

//assign out = a & b;两种写法都可以

endmodule

第五题 取或在取反

module top_module(

input a,

input b,

output out );

wire s;

or u1(s ,a,b);

assign out=~s;

// nor u1(out,a,b);或非

// 或者借鉴第四题方法都是一样的

endmodule最后

以上就是失眠电话最近收集整理的关于verilog 入门刷题(HDL)(1-5)的全部内容,更多相关verilog内容请搜索靠谱客的其他文章。

发表评论 取消回复