FPGA基础入门篇(六) 八位全加器的实现

实现八位全加其实很简单,是组合逻辑电路,不必使用时钟。但本次按照如下的要求来实现

要求:用D触发器控制进位,并且用一位全加器来设计八位全加器。

1.verilog 代码实现:

module addr(

clk,adder1,adder2,q,set,cout,cin

);

input [7:0]adder1,adder2;

output[7:0]q;

input set;

output cout;

input cin;

input clk;

wire [7:0] x,y;

assign x=adder1;

assign y=adder2;

wire [7:0]s;

wire [7:1]D,Q;

assign q = s;

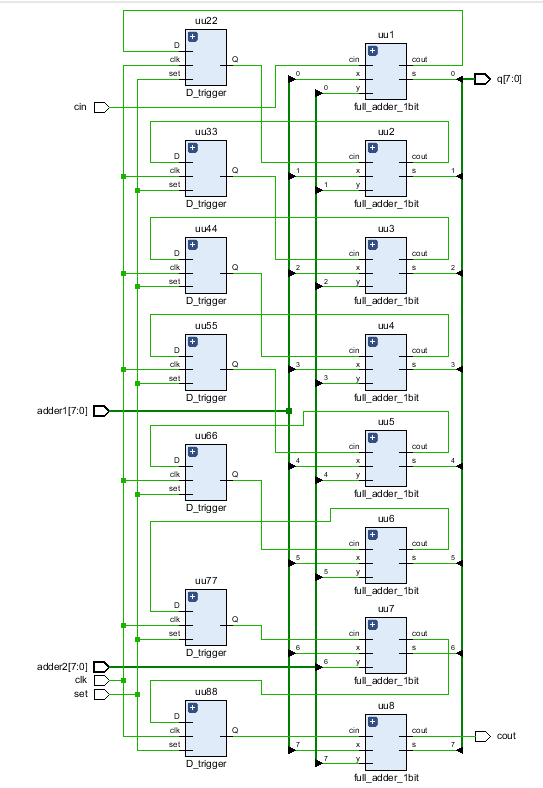

//module intance 八个一位全加器

full_adder_1bit uu1(.cin(cin),.x(x[0]),.y(y[0]),.cout(D[1]),.s(s[0]));

full_adder_1bit uu2(.cin(Q[1]),.x(x[1]),.y(y[1]),.cout(D[2]),.s(s[1]));

full_adder_1bit uu3(.cin(Q[2]),.x(x[2]),.y(y[2]),.cout(D[3]),.s(s[2]));

full_adder_1bit uu4(.cin(Q[3]),.x(x[3]),.y(y[3]),.cout(D[4]),.s(s[3]));

full_adder_1bit uu5(.cin(Q[4]),.x(x[4]),.y(y[4]),.cout(D[5]),.s(s[4]));

full_adder_1bit uu6(.cin(Q[5]),.x(x[5]),.y(y[5]),.cout(D[6]),.s(s[5]));

full_adder_1bit uu7(.cin(Q[6]),.x(x[6]),.y(y[6]),.cout(D[7]),.s(s[6]));

full_adder_1bit uu8(.cin(Q[7]),.x(x[7]),.y(y[7]),.cout(cout),.s(s[7]));

//七个触发器控制进位的产生,进位在下一个时钟到来时进位。

D_trigger uu22(.D(D[1]),.clk(clk),.Q(Q[1]),.set(set));

D_trigger uu33(.D(D[2]),.clk(clk),.Q(Q[2]),.set(set));

D_trigger uu44(.D(D[3]),.clk(clk),.Q(Q[3]),.set(set));

D_trigger uu55(.D(D[4]),.clk(clk),.Q(Q[4]),.set(set));

D_trigger uu66(.D(D[5]),.clk(clk),.Q(Q[5]),.set(set));

D_trigger uu77(.D(D[6]),.clk(clk),.Q(Q[6]),.set(set));

D_trigger uu88(.D(D[7]),.clk(clk),.Q(Q[7]),.set(set));

endmodule

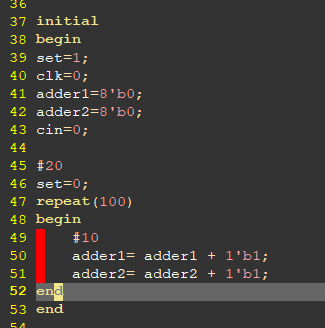

//1bit full_adder

module full_adder_1bit(cin,x,y,cout,s);

input cin;

input x,y;

output cout,s;

assign{cout,s} = x+y+cin;

endmodule

//D_trig

module D_trigger(D,clk,Q,set

);

input D,clk;

input set;

output Q;

reg Q;

always@(posedge clk)

begin

if(set==1)

begin

Q=0; //置位

end

else if(set==0)

begin

Q=D;

end

end

endmodule

- RTL电路描述:

- 仿真结果:

testbench部分代码:

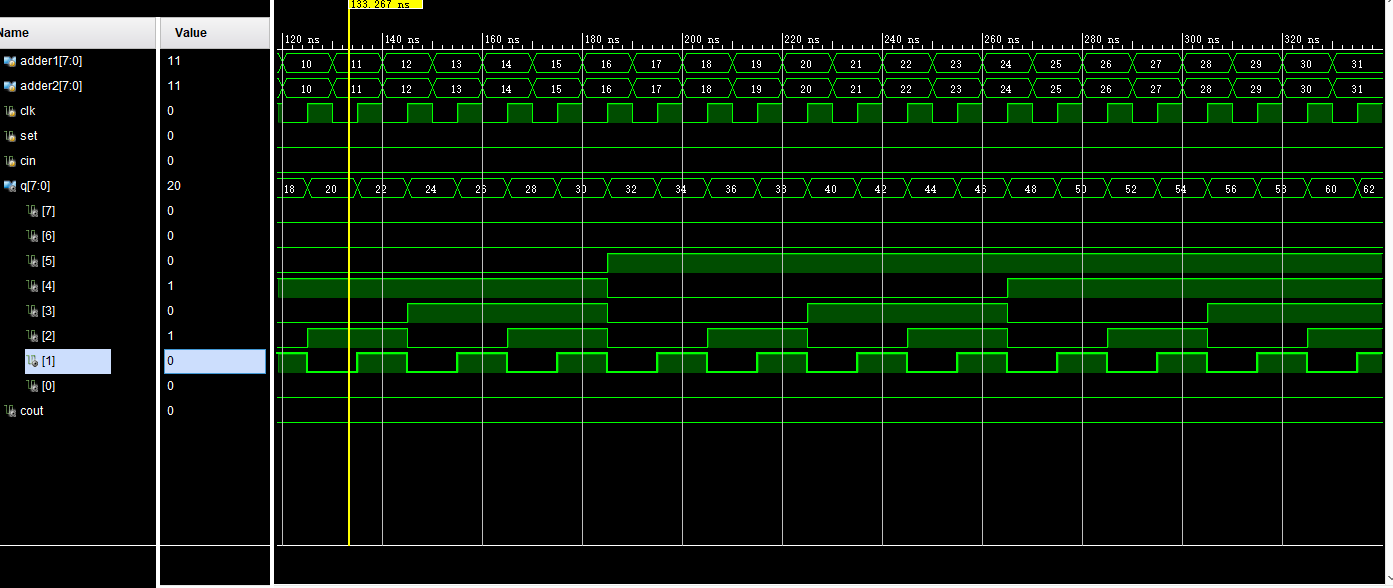

功能仿真结果:

可以看到在每一次输入两个八位二进制数时,会在下个时钟沿到来时实现相加的结果。

最后

以上就是留胡子自行车最近收集整理的关于FPGA基础入门篇(五) 八位全加器的实现,用时钟控制进位(触发器)的全部内容,更多相关FPGA基础入门篇(五)内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复