1.实验目的:

熟悉Verilog语言的使用,熟练的使用modelsim软件,对老师期末布置的三个实验进行仿真。

2.实验内容:

1.数字逻辑基础与Verilog设计P174 图5.12

2.Verilog HDL(第二版)数字电路设计及仿真 十一章实验4

3.Verilog HDL 高级数字设计(第二版)p80 例4.8

3.实验原理:

4实验工具:PC机和modelsim软件。

5.实验截图:

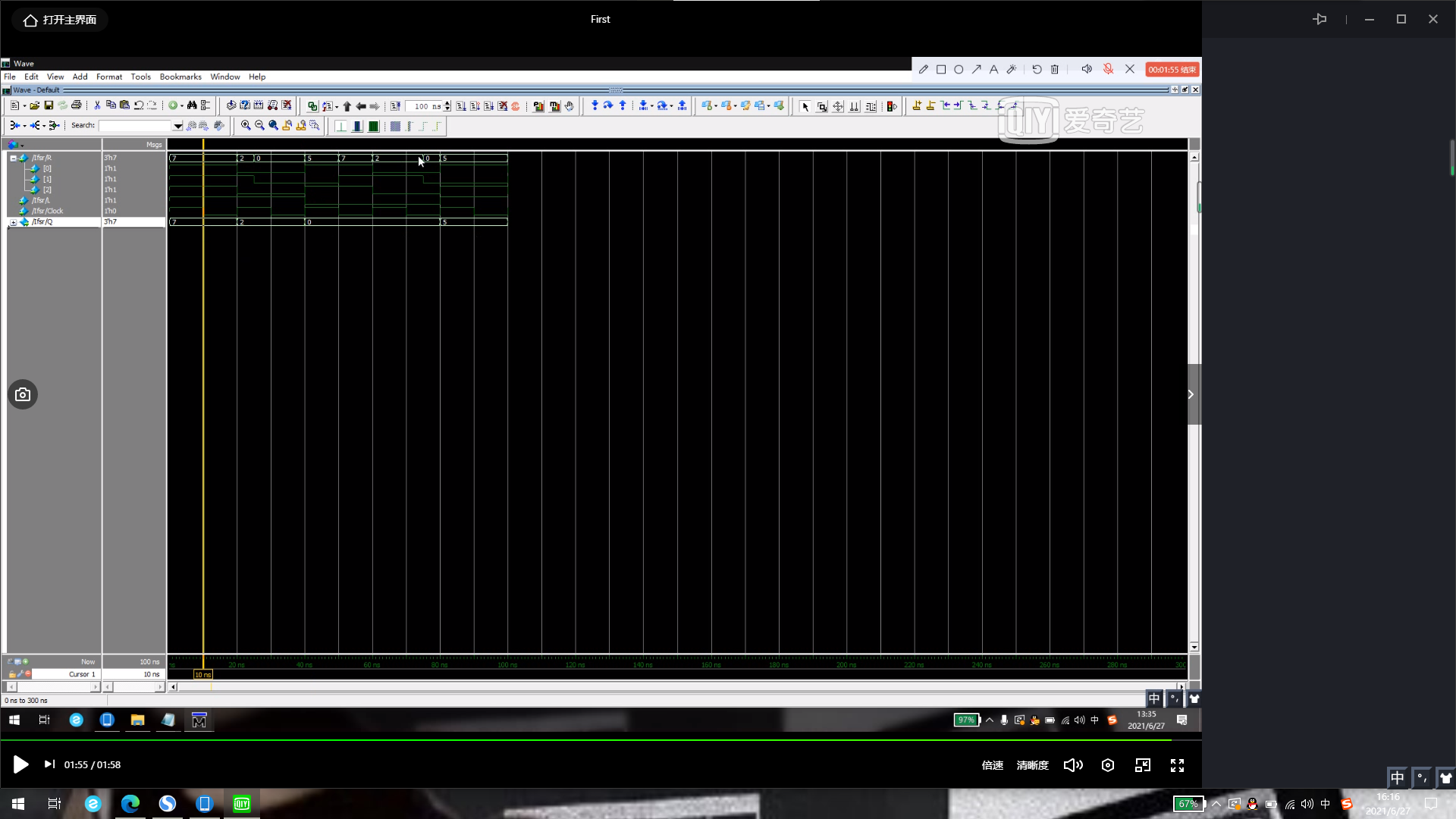

第一个实验截图

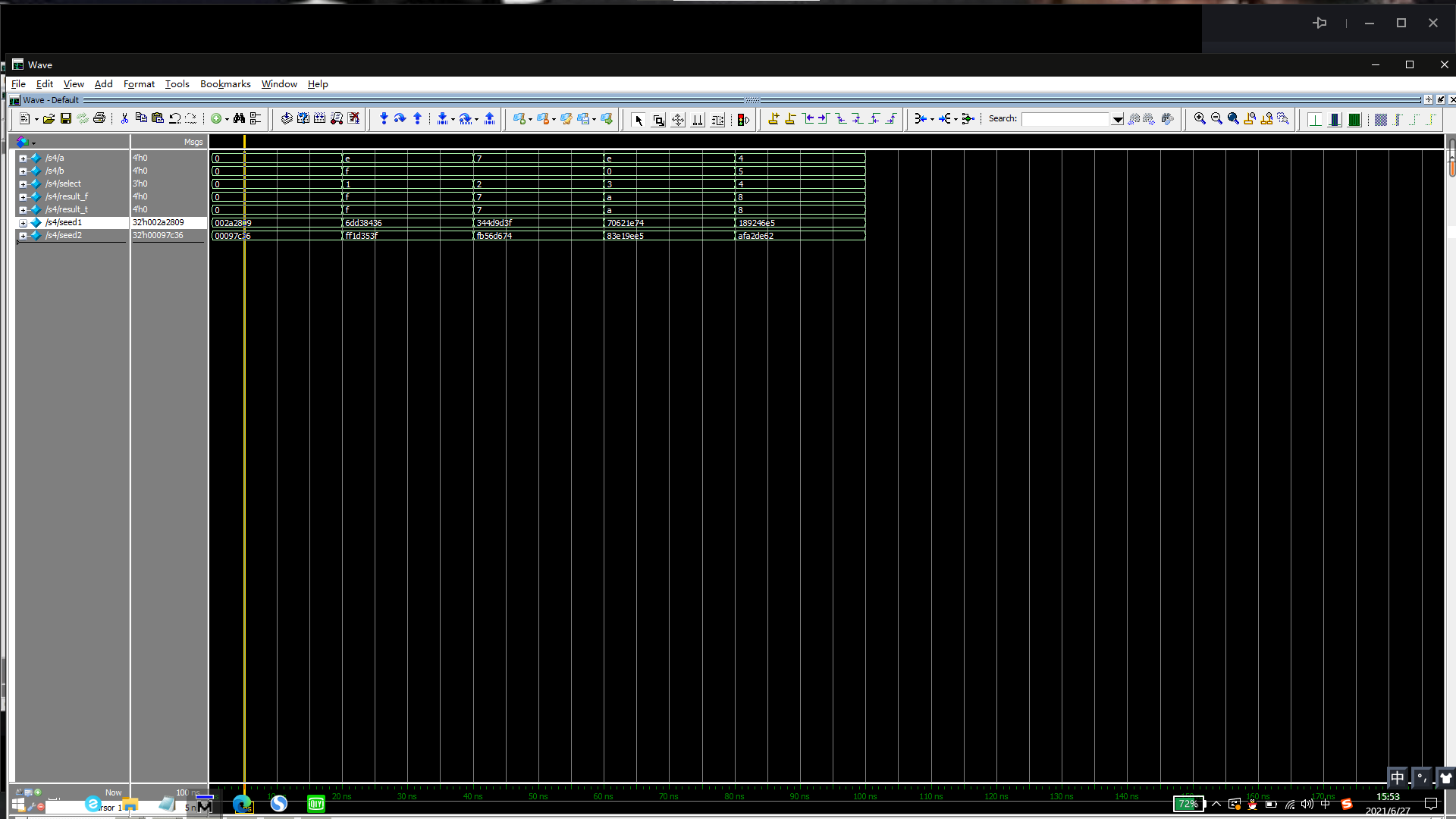

第二个实验截图

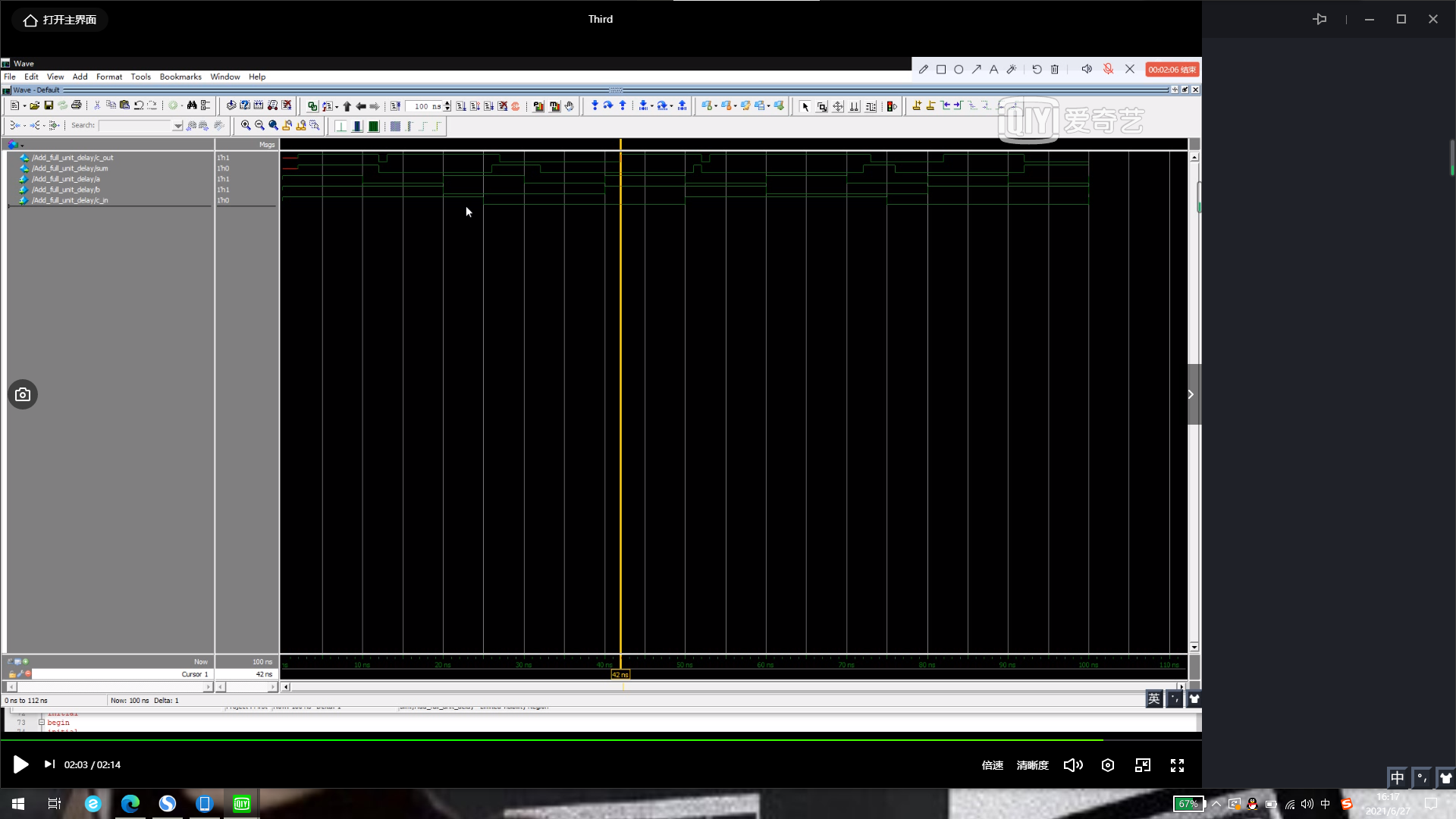

第三个实验截图

6.实验视频:

由于视频文件过大,作者已发布在哔哩哔哩app,请打开以下链接进行播放:

【数字电路基础、期末实验考试三大实验、详细讲解-哔哩哔哩】

【Third-哔哩哔哩】https://b23.tv/GX0WuB

【Second-哔哩哔哩】https://b23.tv/tCkV8P

【First-哔哩哔哩】https://b23.tv/pi0iCS

7.实验代码:

实验一

module Ifsr(R,L, Clock, Q); input [0:2]R;

input L,Clock;

output reg [0:2] Q;

always @(posedge Clock) if (L)

Q<=R;

else

begin

Q[0]=Q[2];

Q[1]=Q[0];

Q[2]=Q[1]^Q[2];

end

endmodule

实验二

module s4;

function [3:0] my_ALU; // function reg [3:0]my_ALU?

input [3:0] a,b;

input [2:0] select;

begin

case (select)

3’b000:my_ALU=a+b;

3’b001:my_ALU=a-b;

3’b010:my_ALU=a;

3’b011:begin

my_ALU={a[3],{~a[2:0]+1}};

end

3’b100:my_ALU=a<<1;

3’b101:my_ALU=a>>1;

3’b110:my_ALU=a%b;

3’b111: begin

if (a>b)

my_ALU=a;

else

my_ALU=b;

end

default:my_ALU=0;

endcase

end

endfunction

task myALU;

input [3:0] a,b;

input [2:0] select;

output[3:0] result; //

begin

case (select)

3’b000:result=a+b;

3’b001:result=a-b;

3’b010:result=a;

3’b011: begin

result={a[3],{~a[2:0]+1}};

end

3’b100: result=a<<1;

3’b101:result=a>>1;

3’b110: result=a%b;

3’b111:begin

if(a>b)

result=a;

else

result=b;

end

default:result=0;

endcase

end

endtask

reg [3:0] a,b;

reg [2:0] select;

reg [3:0] result_f, result_t;

integer seed1,seed2;

initial

begin

select=0;

seed1=40;

seed2=9;

end

always

begin

a={KaTeX parse error: Expected 'EOF', got '}' at position 17: …andom(seed1)/16}̲; b={random(seed2)/16};

#20 select=select+1;

end

always @(a,b,select)

begin

result_f=my_ALU(a,b,select);

myALU(a,b,select,result_t);

end

endmodule

实验三

module Add_full_unit_delay (output c_out, sum, input a, b, c_in);

wire w1,w2,w3;

Add_half_unit_delay M1 (w2, w1, a, b);

Add_half_unit_delay M2 (w3, sum, w1, c_in);

or #1 M3 (c_out, w2, w3);

endmodule

module Add_half_unit_delay (output c_out, sum, input a, b);

xor #1 M1 (sum, a, b);

and #1 M2 (c_out, a, b);

endmodule

8.实验感悟:通过大量的Verilog代码的编写,熟悉了代码的格式,学会自己看懂代码,懂得实验原理,在老师的引领下,从懵懂无知,到逐渐步入了数字电路的世界,领悟Verilog语言的精妙和数字的电路的奇妙,不断进步,成为更严更博识更强大的学生。

最后

以上就是奋斗可乐最近收集整理的关于Verilog HDL期末作业的全部内容,更多相关Verilog内容请搜索靠谱客的其他文章。

发表评论 取消回复