我是靠谱客的博主 震动帽子,这篇文章主要介绍设计一个同步时序电路, 使得每输入4个周期的CLK脉冲, 便输出一个正脉冲, 其宽度等于CLK脉冲的周期. 要求用下降沿触发的JK触发器和尽可能少的门电路构成.,现在分享给大家,希望可以做个参考。

根据题目的描述, 须先设计一个同步四进制(加法)计数器.

根据四进制加法计数器的状态变化特性, 绘制状态表.

| 状态表 | ||||

| Q1 | Q0 | Q1* | Q0* | Z |

| 0 | 0 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 0 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 0 | 1 |

根据状态表, 绘制状态激励表.

| 状态激励表 | ||||||||

| Q1 | Q0 | Q1* | Q0* | J1 | K1 | J0 | K0 | Z |

| 0 | 0 | 0 | 1 | 0 | × | 1 | × | 0 |

| 0 | 1 | 1 | 0 | 1 | × | × | 1 | 0 |

| 1 | 0 | 1 | 1 | × | 0 | 1 | × | 0 |

| 1 | 1 | 0 | 0 | × | 1 | × | 1 | 1 |

由状态激励表, 得知 J1=K1=Q0, J0=K0=1, Z=Q1Q0.

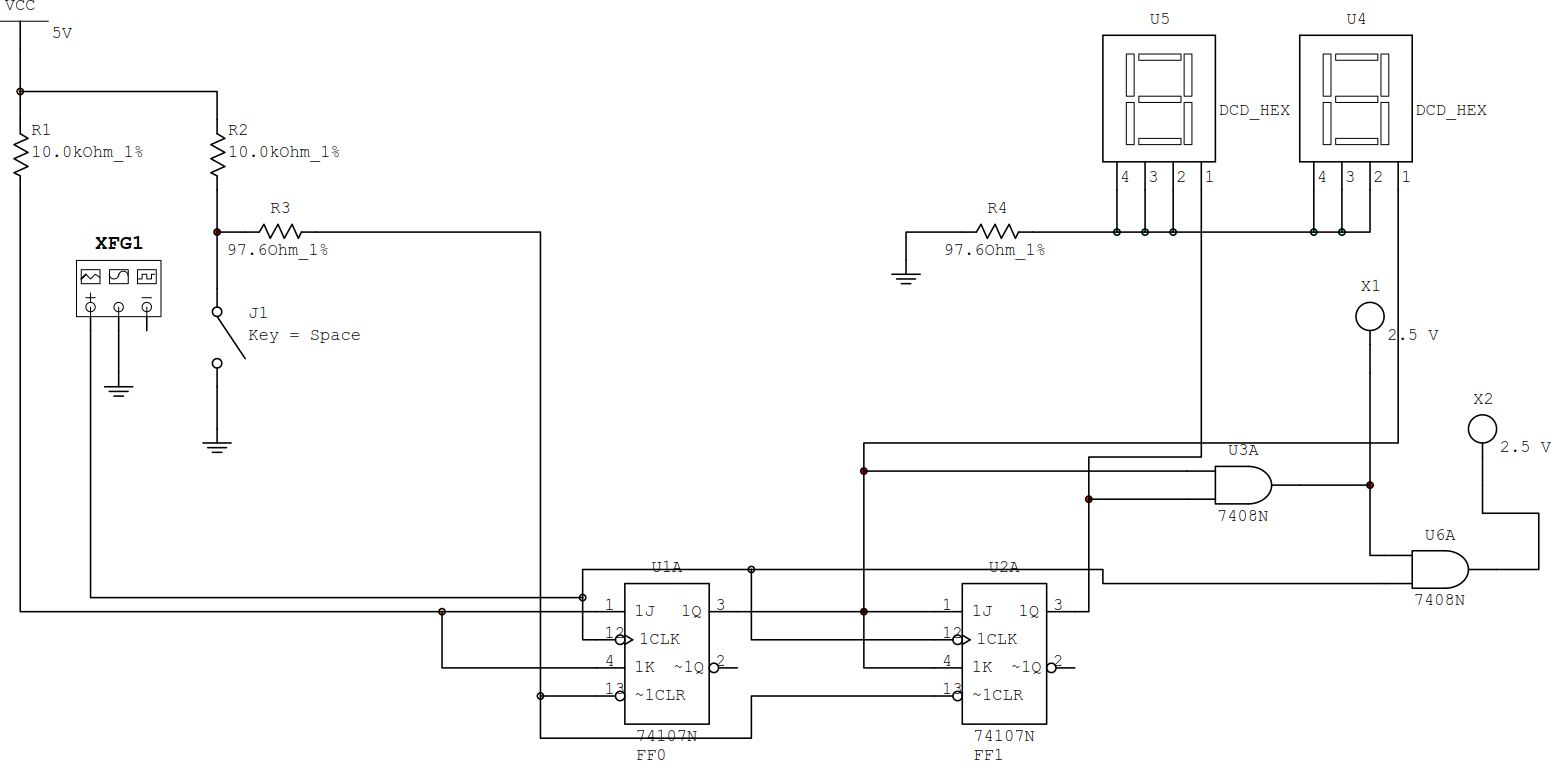

由上面的分析, 绘制电路的原理图.

最后

以上就是震动帽子最近收集整理的关于设计一个同步时序电路, 使得每输入4个周期的CLK脉冲, 便输出一个正脉冲, 其宽度等于CLK脉冲的周期. 要求用下降沿触发的JK触发器和尽可能少的门电路构成.的全部内容,更多相关设计一个同步时序电路,内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复