上篇博文写了用仿真和综合来认识D触发器(通过仿真和综合认识D触发器(Verilog HDL语言描述D触发器)),这篇博文采用完全并行的方式来认识JK触发器。

让我们迅速进入正题吧。

J-K触发器的Verilog HDL程序代码

//边沿JK触发器

module jk_trigger(clk, j, k, q);

input clk, j, k;

output q;

reg q;

wire qb;

always@(posedge clk) //时钟上升沿到来时,判断jk的值

begin

case({j,k})

2'b00: q <= q; //如果{j,k}=00,则触发器处于保持状态

2'b01: q <= 1'b0; //如果{j,k}=01,则触发器置1

2'b10: q <= 1'b1; //同理10,清零

2'b11: q <= ~q; //11,翻转

default: q <= q;

endcase

end

assign qb = ~q;

endmodule

测试文件:

//jk触发器的测试文件

`timescale 1ns/1ps

module jk_trigger_tb;

reg j,k,clk;

wire q;

//时钟电路,周期为20ns

always

begin

#10 clk = ~clk;

end

//初始化

initial

begin

clk = 0;

j = 1'b0;

k = 1'b0;

#30 j = 1'b0; k = 1'b1; //这30ns内,由于q处于保持状态,且q没有初始值,所以此时间段内q值应该处于不确定状态,

//当过了这30ns后,时钟上升沿到来,q值被置0;

#20 j = 1'b1; k = 1'b0; //q值被置1;

#20 j = 1'b1; k = 1'b1; //q值翻转为0;

#20 j = 1'b1; k = 1'b0; //q值被置1;

//拭目以待呗;

end

jk_trigger u1(.j(j), .k(k), .clk(clk), .q(q));

endmodule

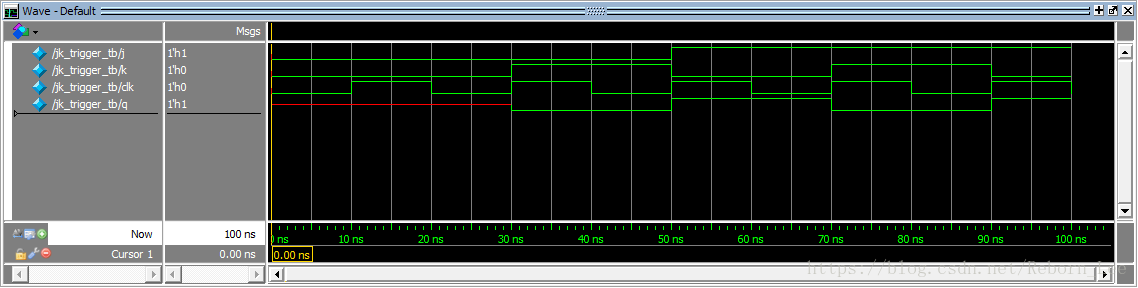

仿真波形:

由仿真波形图可见,和我们在测试代码中说明的一模一样,说明设计正确。

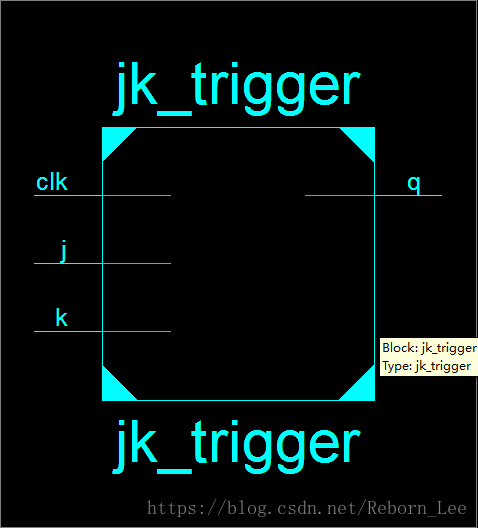

综合后电路图(RTL Schematic):

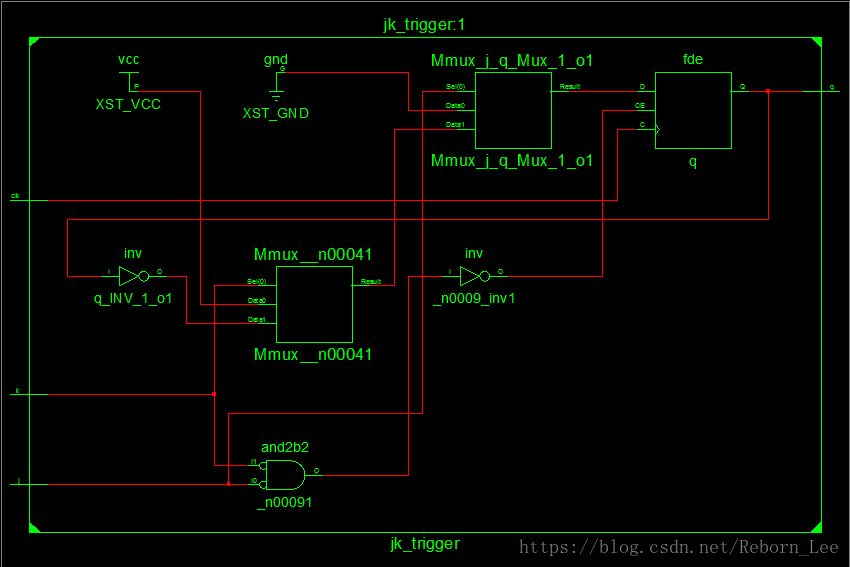

展开后为:

综合出来的电路貌似有点复杂了,但可以直观的看出,这个jk触发器在FPGA中是由D触发器组成的,也就是说FPGA中只有D触发器,其他触发器由D触发器组成。

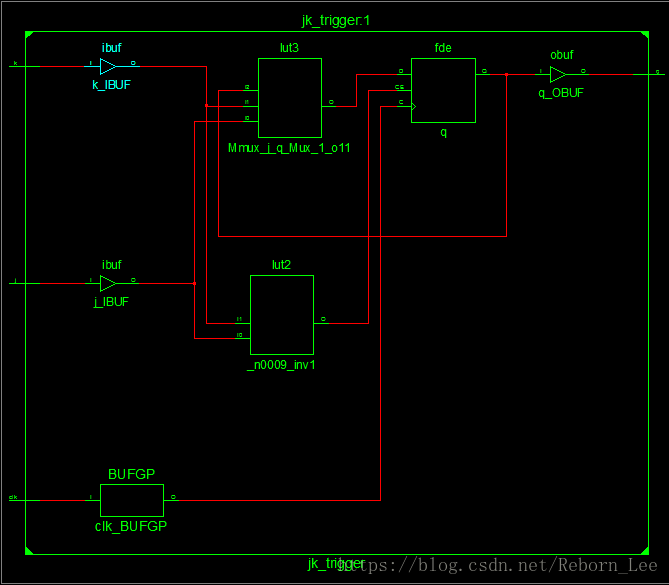

下面再看看Technology Schematic

从中可以看出由查找表(lut),D触发器以及各种缓冲器(buf)组成,关于这里的各种buf是干什么的,可以查看这篇博文:

【FPGA】IBUFG、IBUFGDS、IBUFDS...(这些到底是啥?)

看完之后会有一定的感触的。

最后给出J_k触发器的输入输出关系表格:

| clk | J | K | q | qb |

| 上升沿 | 0 | 0 | q | ~q |

| 上升沿 | 0 | 1 | 0 | 1 |

| 上升沿 | 1 | 0 | 1 | 0 |

| 上升沿 | 1 | 1 | ~q | q |

最后

以上就是积极书包最近收集整理的关于通过仿真和综合认识JK触发器(Verilog HDL语言描述JK触发器)的全部内容,更多相关通过仿真和综合认识JK触发器(Verilog内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复