钟控触发器

钟控触发器的触发方式

按触发器组成结构可将时钟触发器分为四种:电位、维阻、边沿、主从四种。其中电位式触发器结构最简单,前述的四种不同功能的触发器RS、D、JK、T,是按电位式触发器来描述的。这里介绍其它结构形式的RS或D或JK或T触发器。

1.电位式触发器的缺陷

电位式触发器在CP为高电平期间,能接收控制输入信号。在高电平时,如果输入信号发生多次变化,触发器也会发生相应的多次翻转,这种在一个脉冲期间触发器的状态发生多于一次变化的现象,称为触发器的空翻。空翻意味着失控,即触发器的输出不能严格按时钟节拍工作,没有实用性。

2.主从触发器

主从触发器具有主从结构,并以双节拍方式工作,避免了空翻。这里以主从JK触发器为例进行重点讲述。

电路结构见图4-10所示,它由电位式JK触发器和一个电位式RS触发器组成。下面的触发器是主触发器,它的输出Q主、Q非主为内部输出端;上面的触发器为从触发器,它的输出Q、Q非为总的触发器输出。主触发器的输出Q主、Q非主相当于从触发器的输入S、R。

在一个CP周期内它的工作过程分两个阶段:

CP=1期间为第一阶段,此时主触发器根据输入信号J、K改变输出Q主、Q非主的状态,且仅改变一次,称为一次翻转现象,从触发器被封锁,状态不变。

CP由1->0时刻为第二阶段,此时主触发器被封锁,从触发器接收,并输出Q主、Q非主的状态。见其时序图(图4-11)所示。

主从触发器的问题是抗干扰能力不强,如在高电平期间来了一个干扰信号,可能会被主触发器接收,导致触发器的错误翻转。

3.边沿触发器

它是在CP脉冲的跳变沿到来时刻才接收输入信号,并改变触发器的状态。这种触发器 称边沿触发器。在其它时刻不接收信号。边沿触发器根据触发方式分为下降沿触发和上升沿触发两种。先介绍下降沿触发的JK触发器。

在CP下降沿时刻,根据当前的J、K值,并将它们代入JK触发器的特性方程,得到触发器的次态,它是利用电路内部的时延来实现的。

下图4-12,给出了下降沿触发的JK触发器的时序图。

4.维持-阻塞触发器

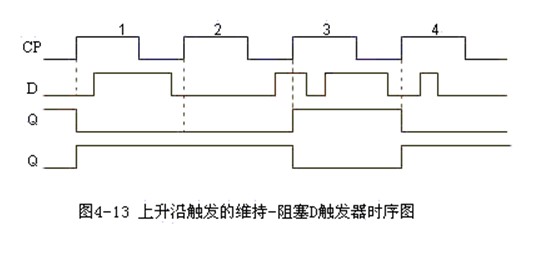

这里介绍上升沿触发的维持-阻塞D触发器。在CP上升沿时刻,触发器根据当前的输入D,反映到触发器输出端,从而改变触发器的状态,它是利用电路内部的维持阻塞线来实现状态改变的。

下图4-13,给出了上升沿触发的维持-阻塞D触发器的时序图。

四、常用触发器的逻辑符号

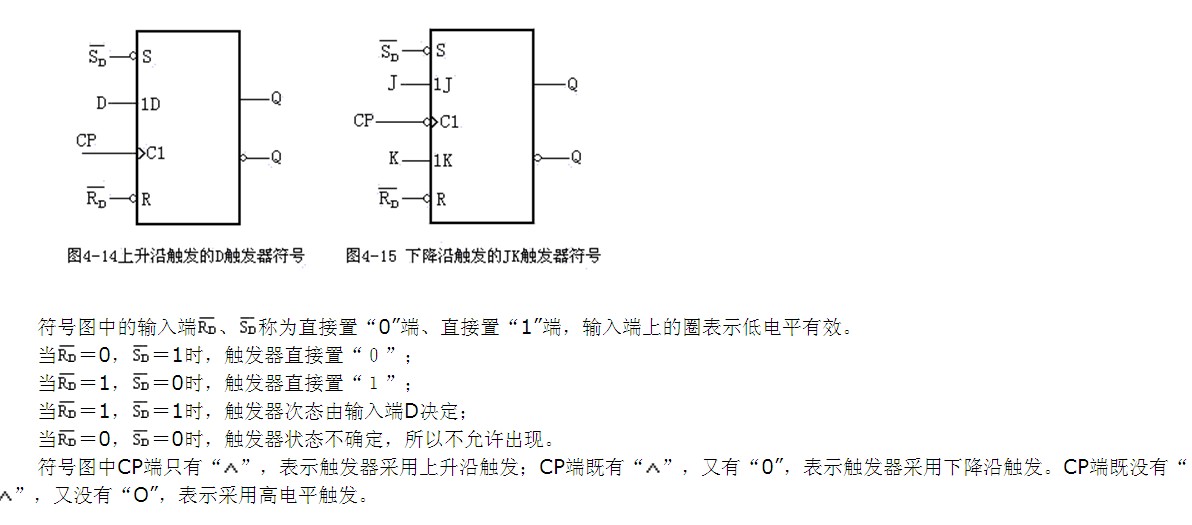

上升沿触发的D触发器和下降沿触发的JK触发器是实际工程中使用得最普遍的集成触发器。它们的新标准符号如图4-14、4-15所示。

一个完整的脉冲是由一个上升沿和一个下降沿组成的,一个完整的脉冲信号应该从第一个上升沿开始,到下一个上升沿结束。

边沿触发是指由一个上升沿或者是一个下降沿就可以触发,具体由上升沿触发或者是下降沿触发得看电路构造。而脉冲触发则要判断是否完整的捕捉到了上升沿与下降沿。

最后

以上就是复杂可乐最近收集整理的关于钟控触发器的全部内容,更多相关钟控触发器内容请搜索靠谱客的其他文章。

发表评论 取消回复