一、填空题(1*15分)

1.

(

67.375

)

10

(67.375)_{10}

(67.375)10=

(

_

_

_

)

2

(___)_2

(___)2=

(

_

_

_

)

16

(___)_{16}

(___)16=

(

_

_

_

)

8421

(___)_{8421}

(___)8421=

(

_

_

_

)

余

三

码

(___)_{余三码}

(___)余三码

2. 若

x

=

−

0.11101

x=-0.11101

x=−0.11101,

[

y

]

补

=

101101

[y]_补=101101

[y]补=101101,则

[

x

]

补

[x]_补

[x]补=(___),

[

−

y

]

补

[-y]_补

[−y]补=(___),

y

y

y=(___),

[

1

2

y

]

补

=

(

_

_

_

)

[frac12y]_补=(___)

[21y]补=(___)

3. 若

x

=

10110111

x=10110111

x=10110111,

[

y

]

G

r

a

y

码

=

11010110

[y]_{Gray码}=11010110

[y]Gray码=11010110,则

[

x

]

G

r

a

y

码

=

(

_

_

_

)

[x]_{Gray码}=(___)

[x]Gray码=(___),

y

=

(

_

_

_

)

y=(___)

y=(___)

4. 若校验位放在最低位,则6的余三码对应的奇校验码是(___)

5. 若

F

=

(

A

‾

+

B

C

‾

)

(

A

+

B

D

‾

)

F=(overline A+Boverline C)(A+Boverline D)

F=(A+BC)(A+BD),则

F

‾

=

(

_

_

_

)

overline F=(___)

F=(___),

F

d

=

(

_

_

_

)

F_d=(___)

Fd=(___)

6. 若

F

(

A

,

B

,

C

)

=

A

‾

B

+

B

C

‾

+

A

B

C

F(A,B,C)=overline AB+Boverline C+ABC

F(A,B,C)=AB+BC+ABC,则

F

=

Σ

m

(

_

_

_

)

=

Π

M

(

_

_

_

)

F=Sigma_m(___)=Pi _M(___)

F=Σm(___)=ΠM(___)

二、选择题(2*5分)

1. 下列器件中,不属于组合逻辑电路的是(___)

A编码器 B译码器 C移位寄存器 D多路选择器

2. 下列PLD器件中与阵列和或阵列都可编程的是(___)

A.PLA B.PAL C.普通型GAL D.PROM

3. 关于逻辑函数

F

(

A

,

B

,

C

)

=

A

B

+

A

‾

C

+

B

C

F(A,B,C)=AB+overline AC+BC

F(A,B,C)=AB+AC+BC的竞争与险象说法正确的是(___)

A变量B存在竞争条件

B变量A存在竞争条件,但不会产生险象

C变量C存在竞争条件

D变量A存在竞争条件,会产生0型险象

4. 以下关于VHDL语言的描述不正确的是(___)

A.完整的VHDL描述包含库、程序包、实体、结构体、配置五个部分,但仅有实体和结构体是必需的。

B.实体部分仅描述电路的对外接口,不描述电路的具体功能。

C.结构体部分用于描述电路的具体功能,结构体与实体存在一一对应关系。

D.结构体有数据流描述、行为描述、结构描述和混合描述4种描述方法。

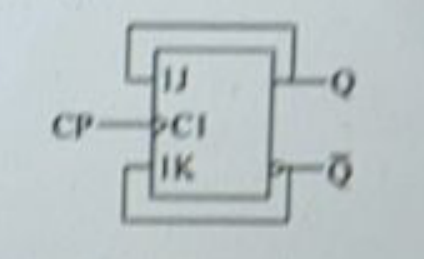

5. JK触发器按图方式连接,其次态方程为(___)

A.

Q

n

+

1

=

Q

‾

Q^{n+1}=overline Q

Qn+1=Q

B.

Q

n

+

1

=

1

Q^{n+1}=1

Qn+1=1

C.

Q

n

+

1

=

0

Q^{n+1}=0

Qn+1=0

D.

Q

n

+

1

=

Q

Q^{n+1}=Q

Qn+1=Q

三、化简(2*8分)

将下列逻辑函数化简成最简与或式和最简或与式

1.

F

(

A

,

B

,

C

,

D

)

=

A

C

‾

+

A

B

C

+

A

C

D

‾

+

C

D

F(A,B,C,D)=Aoverline C+ABC+ACoverline D+CD

F(A,B,C,D)=AC+ABC+ACD+CD

2.

F

(

A

,

B

,

C

,

D

)

=

Σ

m

(

2

,

5

,

6

,

8

,

12

,

13

,

14

)

+

Σ

d

(

0

,

1

,

4

,

10

)

F(A,B,C,D)=Sigma _m(2,5,6,8,12,13,14)+Sigma _d(0,1,4,10)

F(A,B,C,D)=Σm(2,5,6,8,12,13,14)+Σd(0,1,4,10)

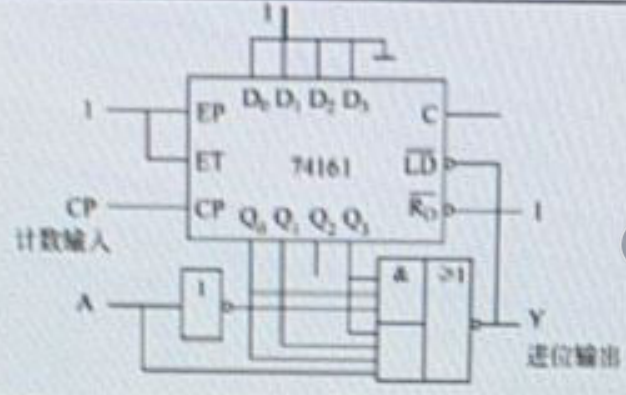

四、计数器(2*8分)

分析如图的可变进制计数器,完成下列问题

1.试分析当控制变量A为0和1时电路实现的各式多少进制计数器,要求给出分析过程。

2.用74LS161设计一个可逆计数器,当控制变量A=0时按6进制计数,A=1时按12进制计数。

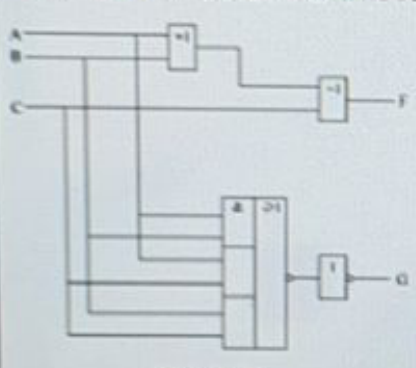

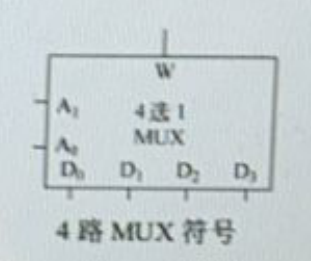

五、组合逻辑(5*4分)

分析图示组合逻辑电路,说明其实现功能

1.写出电路的输出表达式,说明其实现的功能

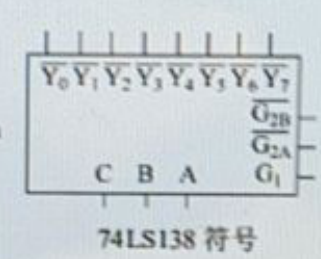

2.用74LS138译码器和与非门实现该电路功能。

3.用四路MUX实现该电路的功能,选择A、B接选择器的地址端。

4.用PLA实现该电路功能,画出阵列图。

六、时序逻辑(15分)

试用JK触发器设计一个八进制计数器,要求如下:

1.该计数器有一个计数输出端

C

C

C,计数到最大状态时

C

=

1

C=1

C=1,否则

C

=

0

C=0

C=0

2.该计数器有一个使能控制端

E

,

E

=

1

E,E=1

E,E=1时正常计数,

E

=

0

E=0

E=0时,停止计数保持原状态且进位输出保持不变。

3.只需求出激励表达式和输出表达式即可,可不画电路图。

JK触发器次态方程为

Q

n

+

1

=

J

Q

‾

+

K

‾

Q

Q^{n+1}=Joverline Q+overline KQ

Qn+1=JQ+KQ

七、VHDL(8分)

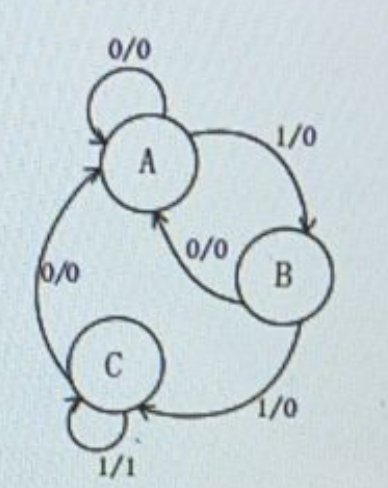

用VHDL语言描述下图所示的状态图,请将程序中的状态转移进程和输出进程补充完整。

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity sequence_detector is

port(clk,x,RD:in std_logic;

Z:out std_logic);

end sequence_detector;

architecture one of sequence_detector is

type state_type is (A,B,C);

signal state:state_type;

begin

process (clk,RD)

begin

.

.

.

…把状态转移进程补充完整。

end process;

output_p:process(state)

begin

.

.

.

…把输出转移进程补充完整

end process;

end one;

最后

以上就是乐观背包最近收集整理的关于江苏大学 数字逻辑电路设计/数字电路 期末/考研 复习题一、填空题(1*15分)二、选择题(2*5分)三、化简(2*8分)四、计数器(2*8分)五、组合逻辑(5*4分)六、时序逻辑(15分)七、VHDL(8分)的全部内容,更多相关江苏大学内容请搜索靠谱客的其他文章。

发表评论 取消回复