同歩二进制加法计数器

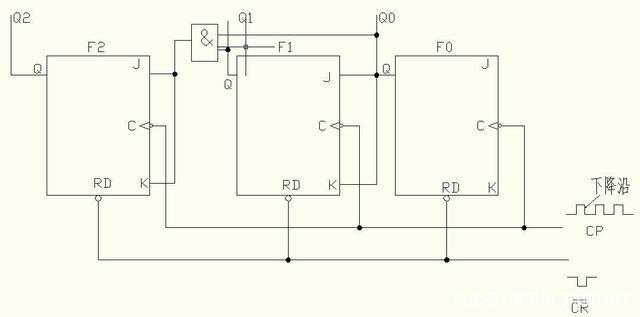

3位同步二进制加法计数器如图所示。

3位同步二进制加法计数器

该计数器是一个3位同步二进制加法计数器,它由3个JK触发器和一个与门组成。与 异步计数器不同的是,它将计数脉冲同时送到每个触发器的CP端,计数脉冲到来时,各个触发器同时工作,这种形式的计数器成为同步计数器。

数字计数器

计数器的工作过程分为两步。

第一步:计数器复位清零。

在工作前应先对计数器进行复位清零。在复位控制端送一个负脉冲到各触发器Rd端, 触发器状态都变为“0",即Q2Q1Q0=000 。

第二步:计数器开始计数。

当第1个时钟脉冲的下降沿到来时,3个触发器同时工作。在时钟脉冲下降沿到来时, 触发器F。的J=K=1 (J、K悬空为“1”),触发器F0状态翻转,由“0”变为“1”;在时钟脉冲下降沿到来时,触发器F1的J=K=Q0=0 (注:在时钟脉冲下降沿刚到来时,触发器F0状态 还未变为“1”),触发器F1状态保持不变,仍为“0”;在时钟脉冲下降沿到来时,触发器F2 的

J=K=Q0*Q1=0*0=0 (注:在时钟脉冲下降沿刚到来时,触发器F0、F1状态还未变化,均 为“0”),触发器F2状态保持不变,仍为“0”。第1个时钟脉冲过后,计数器的Q2Q1Q=OO1.

数字芯片

同理,当第37个时钟脉冲下降沿到来时,计数器状态依次变为011、100, 101、110、 111;当再来一个时钟脉冲时,计数器状态又变为000。

从上面的分析可以看出,同步计数器的各个触发器在时钟脉冲的控制下同时工作,计数速度快。如果将图中的Q0 Q1改接到Q0非 Q1非上,就可以构成同步二进制减法计数器。

最后

以上就是愤怒诺言最近收集整理的关于jk触发器改为四进制_3位同步二进制加法计数器加法减法的实现的全部内容,更多相关jk触发器改为四进制_3位同步二进制加法计数器加法减法内容请搜索靠谱客的其他文章。

发表评论 取消回复