EDA(电子设计自动化) 河北大学实验

说明:本文作者为河大新区2016级通信工程学生,河大理工的学弟学妹看到这篇文章就可以放心的抄了

- 实验一 分频器的设计

要求:掌握时序逻辑电路的设计方法,编写50MHz分频得到1Hz的方波信号。(文件名为fenpin.v)

module fenpin (res,clk,fout);

input clk,res;

output fout;

reg fout;

reg [21:0] j; //21位宽

always@(posedge clk)

if (res)

begin

fout <=0;

j<=0;

end

else

begin

if(j==3124999) //这里的j=3124999 计算方法为(50M / 8)-1 实现了50MHz→8Hz

begin

j<=0;

fout<=~fout;

end

else

j<=j+1;

end

endmodule

- 实验二 计数器的设计

要求1:设计一位十进制计数器(文件名为jishu10.v)。 具有异步复位和技术使能功能。复位信号高电平有效。clken=0,暂停计数;clken=1,正常计数。

module jishu10 (clk,q,co,rst,clken);

input clk,rst,clken;

output [3:0] q;

output co;

reg [3:0]q;

reg co;

always@ (posedge clk or posedge rst)

if (rst)

begin q<=0; co<=0;

end

else if (clken)

if (q==4'd9)

begin q<=0;

co<=1;

end

else begin q<=q+1; co<=0; end

else begin q<=q; co<=co;end

endmodule

要求2:把实验一的分频器加到本实验中,作为一位十进制计数器的时钟输入信号。利用元件例化方法设计。原理如图(此处略,懒得敲了)

要求3:利用元件例化方法设计四位十进制计数器。(文件名为siwei10)

module siwei10 (clk,rst,clken,q0,q1,q2,q3,co0,co1,co2,co);

input clk,rst,clken;

output [3:0] q0,q1,q2,q3;

output co0,co1,co2,co;

wire data0,data1,data2,data3;//clk,q,co,rst,clken

jishu10 u1 (.clk(clk),.clken(clken),.q(q0),.co(co0),.rst(rst));

jishu u2 (.clk(co0),.clken(clken),.q(q1),.co(co1),.rst(rst));

jishu u3 (.clk(co1),.clken(clken),.q(q2),.co(co2),.rst(rst));

jishu u4 (.clk(co2),.clken(clken),.q(q3),.co(co),.rst(rst));

endmodule

- 实验三 用Modelsim对计数器仿真

要求:对十进制计数器工程进行仿真

见实验指导书P62。

- 实验四 七段译码器设计

要求1:对应七段数码管(共阳极,低电平有效),写出七段译码器verilog程序(文件名sevenyima.v)

module sevenyima(decodeout,indec);

output[0:6] decodeout;

input [3:0] indec;

reg [0:6] decodeout;

always@(indec)

begin

case(indec)

4'b0000:decodeout=7'b0000001;

4'b0001:decodeout=7'b1001111;

4'b0010:decodeout=7'b0010010;

4'b0011:decodeout=7'b0000110;

4'b0100:decodeout=7'b1001100;

4'b0101:decodeout=7'b0100100;

4'b0110:decodeout=7'b0100000;

4'b0111:decodeout=7'b0001111;

4'b1000:decodeout=7'b0000000;

4'b1001:decodeout=7'b0000100;

default:decodeout=7'bx;

endcase

end

endmodule

要求2:对译码器的设计进行仿真,记录仿真结果。

略//懒得打了

- 实验五 数字频率计设计

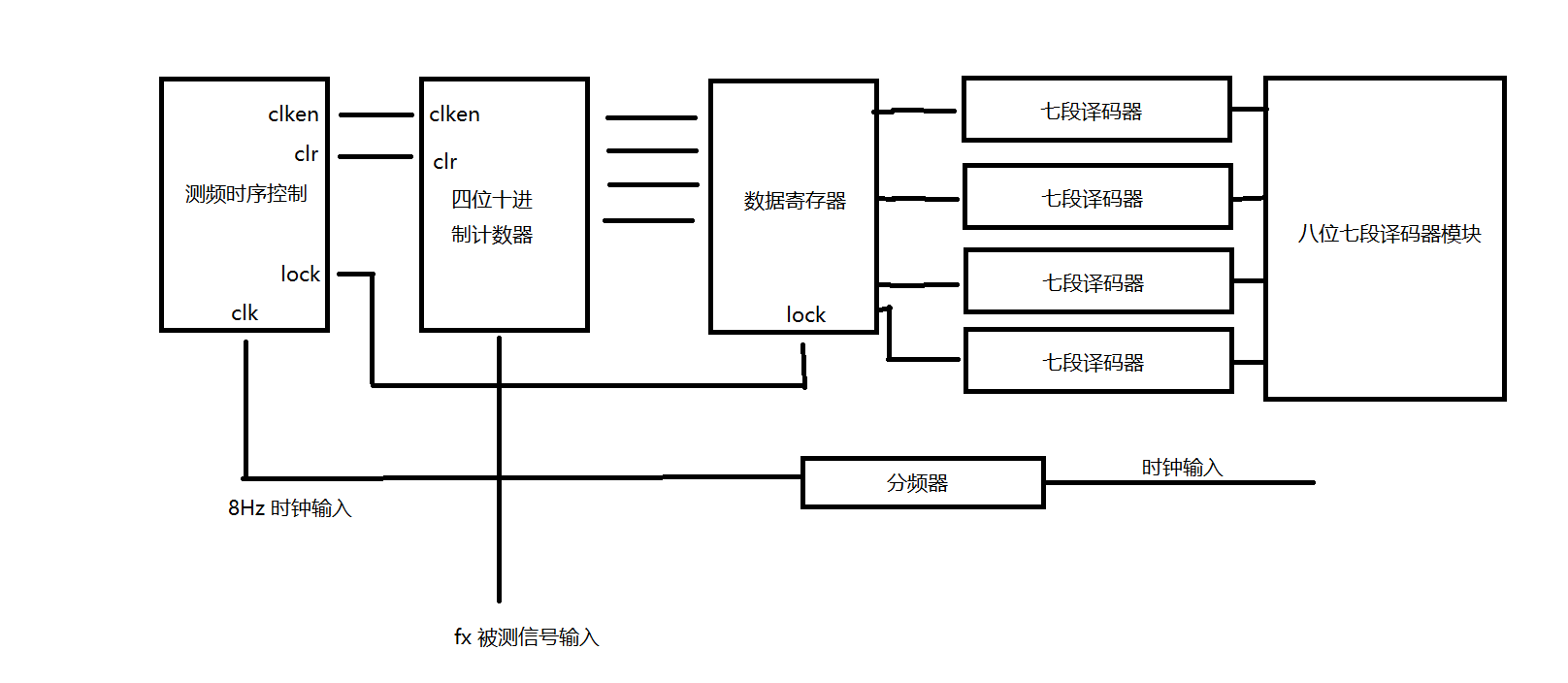

要求:对输入的信号fx进行数字频率的记录

原理图如图:

代码如下:

①分频器代码(文件名fenpin.v,见上文)

②测频时序控制代码(文件名 ck.v)

module ck (clken,clr,lock,clk);

input clk;

output clken,clr,lock;

reg clken,clr,lock;

reg [3:0]j ;

always@(posedge clk)

begin

j<=j+1;

case(j)

4'd0:begin clken<=1;clr<=0;lock<=0; end

4'd1:begin clken<=1;clr<=0; lock<=0; end

4'd2:begin clken<=1;clr<=0; lock<=0; end

4'd3:begin clken<=1;clr<=0; lock<=0; end

4'd4:begin clken<=1;clr<=0; lock<=0; end

4'd5:begin clken<=1;clr<=0; lock<=0; end

4'd6:begin clken<=1;clr<=0; lock<=0; end

4'd7:begin clken<=1;clr<=0; lock<=0; end

4'd8:begin clken<=0;clr<=0; lock<=0; end

4'd9:begin clken<=0;clr<=0; lock<=1; end

4'd10:begin clken<=0;clr<=0;lock<=0; end

4'd11:begin clken<=0;clr<=0;lock<=0; end

4'd12:begin clken<=0;clr<=0;lock<=0; end

4'd13:begin clken<=0;clr<=1;lock<=0; end

4'd14:begin clken<=0;clr<=0;lock<=0; end

4'd15:begin clken<=0;clr<=0;lock<=0; end

endcase

end

endmodule

③四位十进制计数器(文件名siwei10.v,见上文)

④数据寄存器(文件名jicunqi.v)

module jicunqi (lock,a0,a1,a2,a3,b0,b1,b2,b3);

input lock;

input [3:0] a0,a1,a2,a3;

output [3:0] b0,b1,b2,b3;

reg [3:0] b0,b1,b2,b3;

always @(posedge lock)

begin

b0<=a0;

b1<=a1;

b2<=a2;

b3<=a3;

end

endmodule

⑤七段译码器(四个七段译码器并行,即顶层文件调用四次)(文件名sevenyima.v)

⑥八位七段数码管模块(顶层文件的编写)(文件名top.v)

module top (y0,y1,y2,y3,clk,fx);

input clk,fx;

output [0:6] y0,y1,y2,y3;

wire [3:0] a0,a1,a2,a3;

wire [3:0] b0,b1,b2,b3;

wire lock;//此处五个wire型变量 为声明的线网(意即连接模块间的线,无实际意义)

wire f8;

wire res;

wire clr;

wire en;

fenpin u1 (.fout(f8),.clk(clk),.res(0)); //fen pin shu chu

ck u2 (.clk(f8),.lock(lock),.clr(clr),.clken(en)); //测频输入和输出

siwei10 u3 (.clken(en),.rst(clr),.clk(fx),.q0(a0),.q1(a1),.q2(a2),.q3(a3)); //四位十进制输入和输出clk,rst,clken,q0,q1,q2,q3,co0,co1,co2,co3

jicunqi u4 ( .lock(lock),.a0(a0),.a2(a2),.a3(a3),.a1(a1),.b0(b0),.b1(b1),.b2(b2),.b3(b3)); //寄存器输入和输出

sevenyima u5 (.indec(b0),.decodeout(y0));

sevenyima u6 (.indec(b1),.decodeout(y1));

sevenyima u7 (.indec(b2),.decodeout(y2));

sevenyima u8 (.indec(b3),.decodeout(y3));

endmodule

感谢您的阅读,如果对您的学习或工作起到了一丝丝帮助,麻烦您点个赞,靴靴。

最后

以上就是勤劳棒球最近收集整理的关于EDA(电子设计自动化) 河北大学实验的全部内容,更多相关EDA(电子设计自动化)内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复