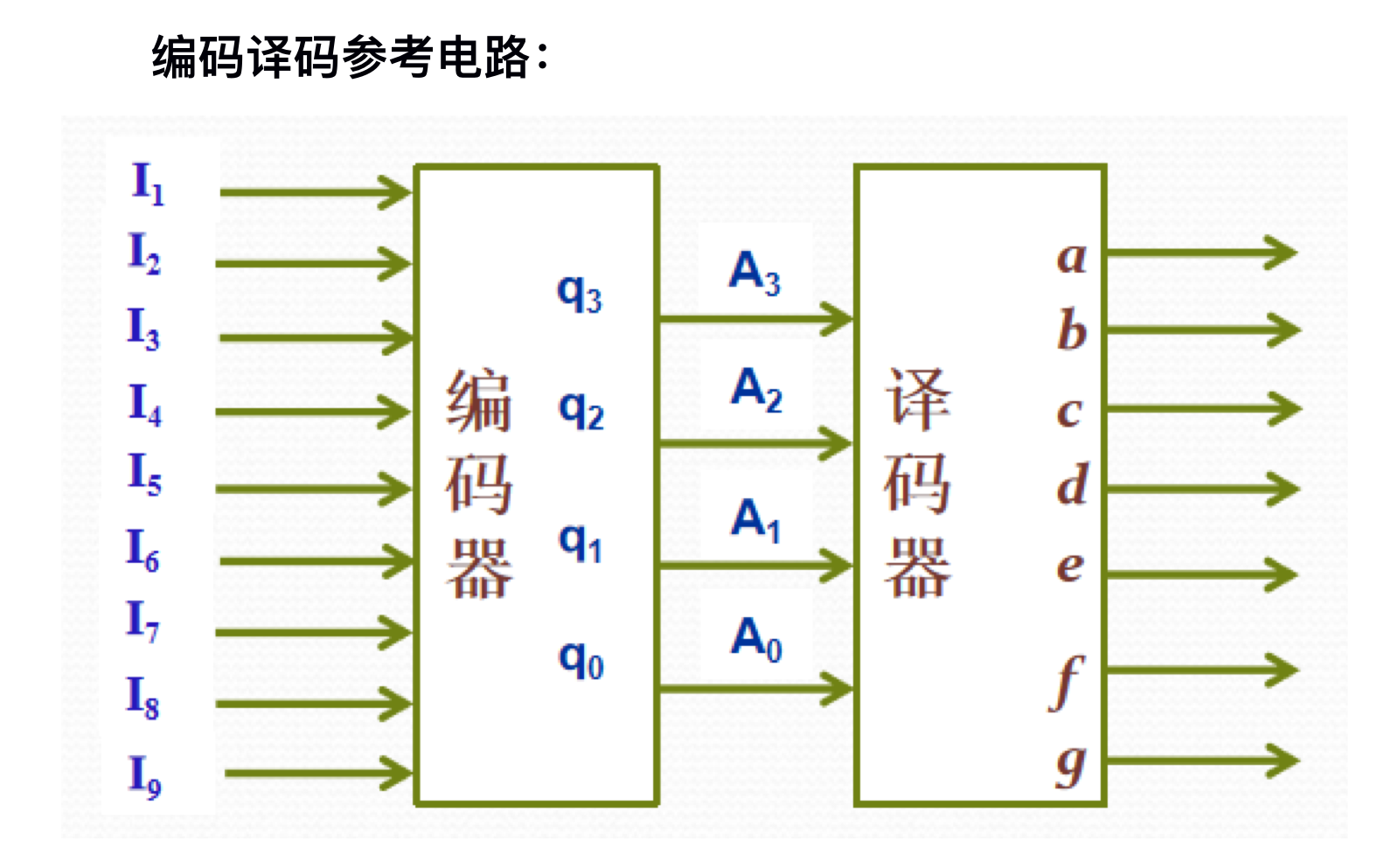

EDA实验(2)编码译码电路设计

实验要求

1.采用Verilog设计BCD编码器并生成元件符号

2.采用Verilog设计七段译码器并生成元件符号

3.建立顶层原理图文件,组成编码译码器电路

思路与代码

1.BCD编码器的设计

使用9位拨码开关实现:当每一个对应的拨码开关被打开,编码器输出其对应的BCD码。代码如下:

module code(A,BCD);

input[8:0] A;

output[3:0] BCD;

reg[3:0] BCD;

always@(A)

case(A)

9'b000000001:BCD<=4'b0001;

9'b000000010:BCD<=4'b0010;

9'b000000100:BCD<=4'b0011;

9'b000001000:BCD<=4'b0100;

9'b000010000:BCD<=4'b0101;

9'b000100000:BCD<=4'b0110;

9'b001000000:BCD<=4'b0111;

9'b010000000:BCD<=4'b1000;

9'b100000000:BCD<=4'b1001;

default BCD<=4'b0000;

endcase

endmodule 2.译码器的设计

译码器收到编码器传出的BCD码后,输出对应的编码至数码管,使数码管显示对应的数字。程序如下:

module decode(B,LED7S);

input[3:0] B;

output[6:0] LED7S;

reg[6:0] LED7S;

always@(B)

case(B)

4'b0000:LED7S<=7'b1111110; //0

4'b0001:LED7S<=7'b0110000; //1

4'b0010:LED7S<=7'b1101101; //2

4'b0011:LED7S<=7'b1111001; //3

4'b0100:LED7S<=7'b0110011; //4

4'b0101:LED7S<=7'b1011011; //5

4'b0110:LED7S<=7'b1011111; //6

4'b0111:LED7S<=7'b1110000; //7

4'b1000:LED7S<=7'b1111111; //8

4'b1001:LED7S<=7'b1111011; //9

endcase

endmodule 最后

以上就是鳗鱼盼望最近收集整理的关于EDA实验(2)编码译码电路设计的全部内容,更多相关EDA实验(2)编码译码电路设计内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复