link

Verilog中仿真事件中的不同延时方法

-

电路的延时

在实际电路中存在两种延迟,惯性延迟 (Inertial delay) 和传导延迟 (Transport delay)。

惯性延迟

定义:若元件的输入信号的脉冲宽度小于一定值时,元件的输出没有响应,也就是说元件具有一定的惯性。

产生原因:当脉冲到达时,由于脉冲宽度小于元件本身的延迟,当脉冲结束时,元件的新输出还未建立起来。考虑了电路中存在的大量分布电容。

传导延迟

定义:输入信号变化到对应输出信号变化经过的时间,类似于物理传输线的延迟。

产生原因:载流子运动的速度有限,通过导线需要一定的时间。 -

Verilog中的时序模型

在分析Verilog HDL的仿真行为前,我们需要了解Verilog中时序模型。

时序模型分为:门级时序模型、过程时序模型。

门级时序模型

适用范围:所有的连续赋值语句、过程连续赋值语句、门原语、用户自定义原语。

特点:

任意时刻输入发生变化,将重新计算输出。

当之前的事件未执行完毕时又发生的新的变化,则会撤销之前的事件,开始新的事件。

过程时序模型

适用范围:过程语句。

特点:

当敏感列表发生变化时触发执行。

当之前的事件未执行完毕时又发生的新的变化,则不撤销原有事件,同时开始新的事件,如果同时有几个更新事件,它们的执行顺序是不确定的。

- Verilog中的仿真延迟语句

Verilog 中的仿真延时语句为 #n,n表示延时时间,将该语句加在语句中,延迟n个时间单位。

延时的添加方法有两种:正规延迟和内定延迟

正规延迟 (#在外面)

5 C = A +B

在 T 时刻执行到该语句时,等待 5 个时间单位,然后计算等号右边的值赋给 C,此时使用的 A B 的值是 T+5 时刻的值。

内定延迟 (#在里面)

C = #5 A +B

在 T 时刻执行到该语句时,先计算 A+B 的值,计算后等待 5 个时间单位将值赋给 C,使用的 A B 的值是 T 时刻的值。

- 在 Verilog 建模中增加延时

两种延时的添加方式和三种赋值方式 (连续赋值、阻塞赋值、非阻塞赋值) 一共形成六中添加延迟的方式。

| // 1. 连续赋值+ 正规延迟 | |

| assign #5 C = A +B; | |

| // 2. 连续赋值+ 内定延迟 | |

| assign C = #5 A +B; | |

| // 3. 阻塞赋值 + 正规延迟 | |

| always @(*) begin | |

| #5 C = A +B; | |

| end | |

| // 4. 阻塞赋值 + 内定延迟 | |

| always @(*) begin | |

| C = #5 A +B; | |

| end | |

| // 5. 非阻塞赋值 + 正规延迟 | |

| always @(*) begin | |

| #5 C <= A +B; | |

| end | |

| // 6. 非阻塞赋值 + 内定延迟 | |

| always @(*) begin | |

| C <= #5 A +B; | |

| end |

下面对这六种方式逐一分析:

1.连续赋值+ 正规延迟

在 T 时刻执行到该语句时,等待 5 个时间单位,然后计算等号右边的值赋给 A。

使用的 A B 的值是 T+5 时刻的值。

若在等待过程中 A B 的值发生变化再次触发 assign block,根据 assign block 的门级时序模型特点,仿真器会撤销先前的等待事件,然后重新执行语句。

当变化脉冲小于 5 个时间单位时,等待事件会被撤销,该脉冲将不起作用。

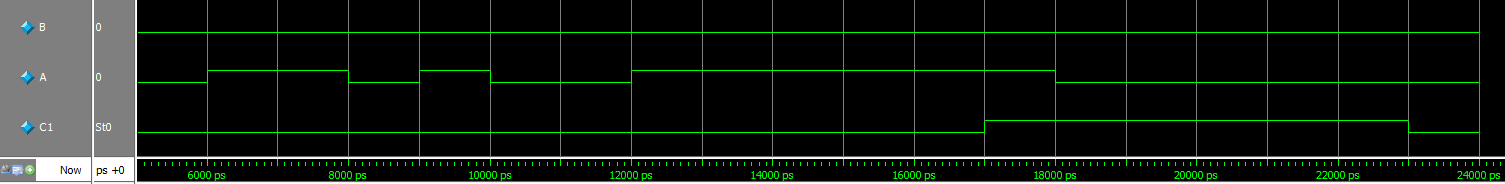

仿真结果:

可以看出在 6ns、8ns、9ns、10ns 时刻 A 发生了变化,但皆因持续时间小于 5ns,所以都没有对 C1 产生影响,只有在 12ns 和 18ns 的变化持续时间超过 5ns,作用到 C1 上。

2.连续赋值+ 内定延迟

在 T 时刻执行到该语句时,计算等号右边的值,等待 5 个时间单位后赋给 A。

使用的 A B 的值是 T 时刻的值。

若在等待过程中 A B 的值发生变化再次触发 assign block,根据 assign block 的门级时序模型特点,仿真器会撤销先前的等待事件,然后重新执行语句。

当变化脉冲小于 5 个时间单位时,等待事件会被撤销,该脉冲将不起作用。

该种方式有记忆属性,与连续赋值原则不符,为非法语句,编译不能通过。

- 阻塞赋值 + 正规延迟

在 T 时刻执行到该语句时,等待 5 个时间单位,然后计算等号右边的值阻塞赋给 A。

使用的 A B 的值是 T+5 时刻的值。

若在等待过程中 A B 的值发生变化再次触发 always block,根据 always block 的过程时序模型特点,此时还在等待过程,always 语句还未执行结束,不会开始新一轮的事件,仿真器不会对敏感列表反应。

仿真器忽略延迟时间段的数据变化。

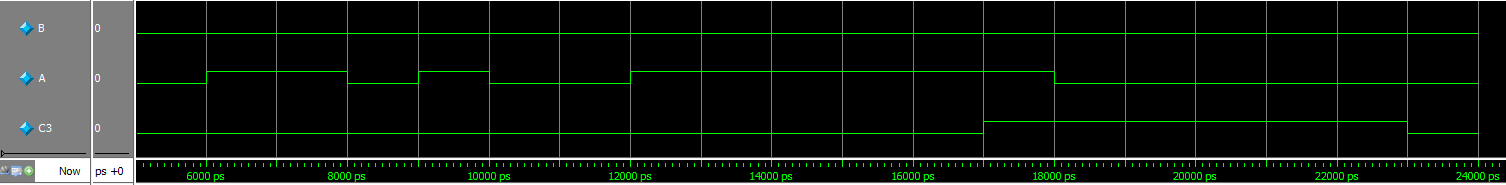

仿真结果:

在 6ns 时刻 A 的值发生变化,always block 开始执行,经过 5ns,用 11ns 时刻的 A B 的值计算出结果赋给 C3,而忽略了 8ns 和 10ns 时刻的变化。

- 阻塞赋值 + 内定延迟

在 T 时刻执行到该语句时,计算等号右边的值,等待 5 个时间单位后赋给 A。

使用的 A B 的值是 T 时刻的值。

若在等待过程中 A B 的值发生变化再次触发 always block,根据 always block 的过程时序模型特点,由于赋值方式为阻塞赋值,此时 always 语句还未执行结束,不会开始新一轮的事件,仿真器不会对敏感列表反应。

仿真器忽略延迟时间段的数据变化。

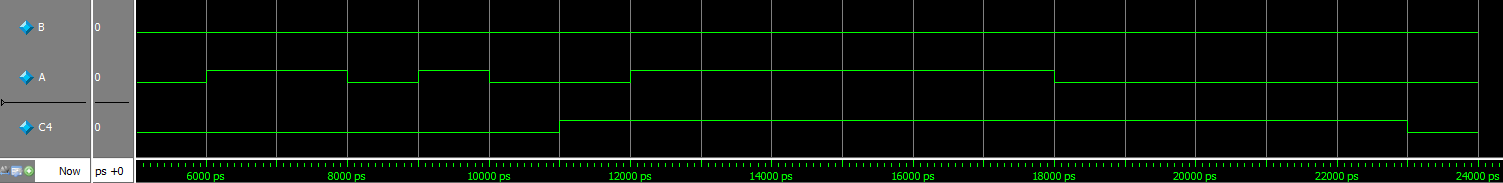

仿真结果:

在 6ns 时刻 A 的值发生变化,always block 开始执行,经过 5ns,用 6ns 时刻的 A B 的变化后的值计算出结果赋给 C4,而忽略了 8ns 和 10ns 时刻的变化。

- 非阻塞赋值 + 正规延迟

在 T 时刻执行到该语句时,等待 5 个时间单位,然后计算等号右边的值阻塞赋给 A。

使用的 A B 的值是 T+5 时刻的值。

若在等待过程中 A B 的值发生变化再次触发 always block,根据 always block 的过程时序模型特点,此时还在等待过程,always 语句还未执行结束,不会开始新一轮的事件,仿真器不会对敏感列表反应。

仿真器忽略延迟时间段的数据变化。

仿真结果:

在 6ns 时刻 A 的值发生变化,always block 开始执行,经过 5ns,用 11ns 时刻的 A B 的值计算出结果赋给 C5,而忽略了 8ns 和 10ns 时刻的变化。

- 非阻塞赋值 + 内定延迟

在 T 时刻执行到该语句时,计算等号右边的值,等待 5 个时间单位后赋给 A。

使用的 A B 的值是 T 时刻的值。

若在等待过程中 A B 的值发生变化再次触发 always block,根据 always block 的过程时序模型特点,由于赋值方式为非阻塞赋值,将赋值事件放进事件队列后,always 语句执行结束,等待下一次的触发,触发来到时开始新一轮的事件。

仿真器接受延迟时间段的数据变化,输入的变化延迟会全部反应在输出上。

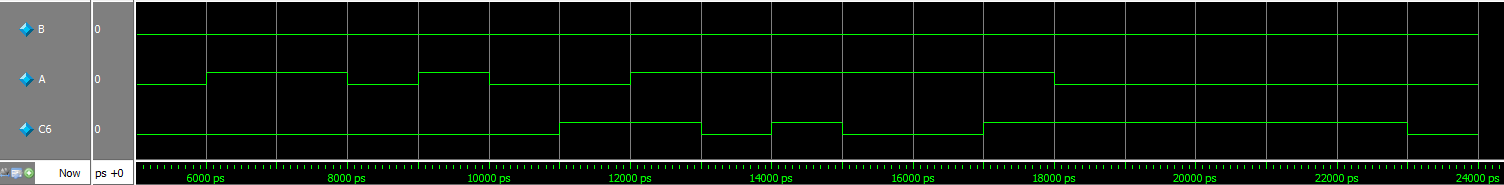

仿真结果:

A B 的每一次变化都触发 always block 的执行,每一次变化都延时 5ns 后反应在 C6 上。

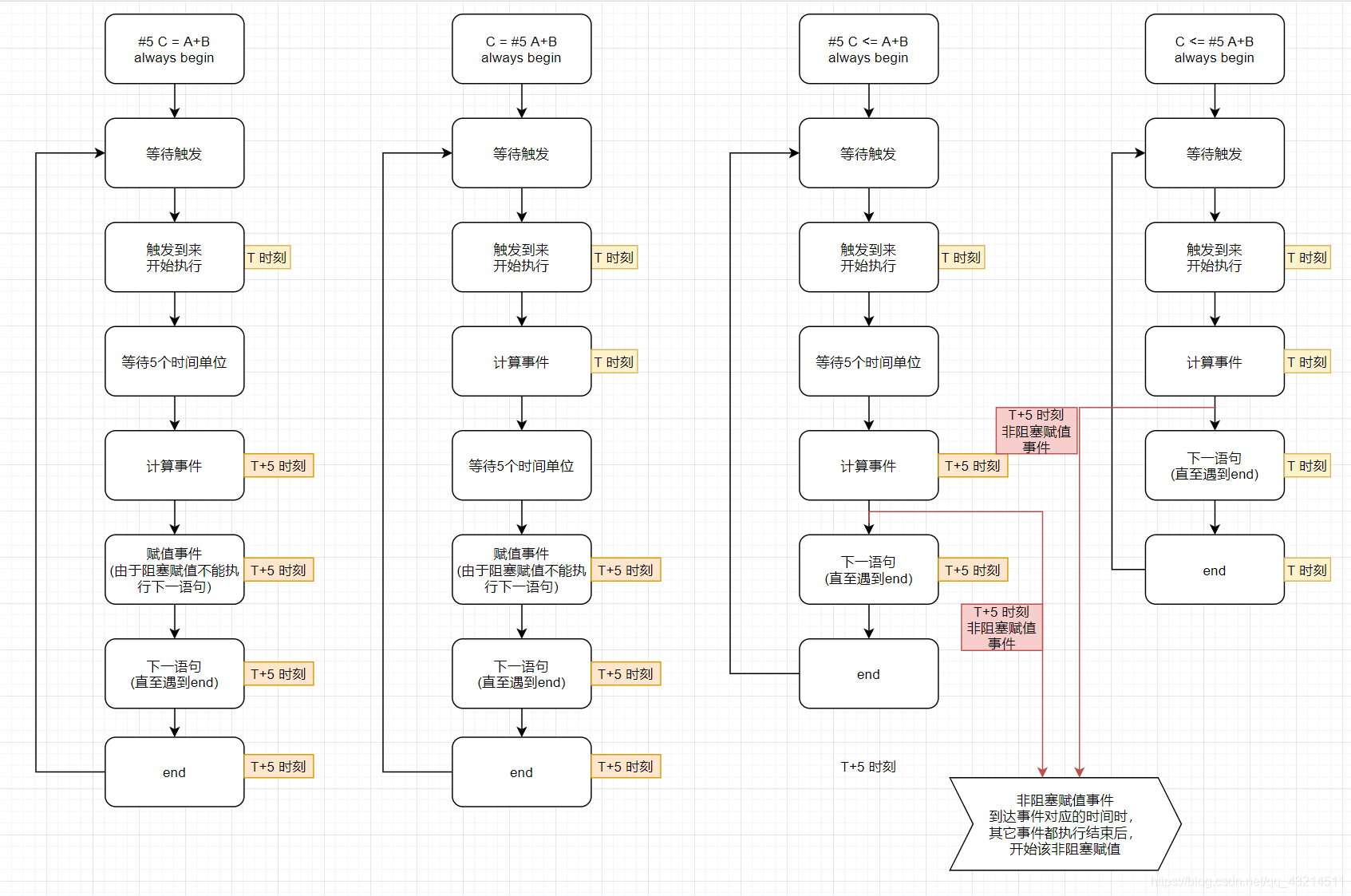

下图为 always block 中的四种延时方式的仿真流程:

| // 仿真源码 | |

| `timescale 1ns/1ps | |

| module Testbench; | |

| reg A,B; | |

| wire C1,C2; | |

| reg C3,C4,C5,C6; | |

| initial begin | |

| A = 0; B = 0; | |

| C3 = 0; C4 = 0; C5 = 0; C6 = 0; | |

| #6 A = 1; | |

| #2 A = 0; | |

| #1 A = 1; | |

| #1 A = 0; | |

| #2 A = 1; | |

| #6 A = 0; | |

| end | |

| // 1. 连续赋值+ 正规延迟 | |

| assign #5 C1 = A +B; | |

| // 3. 阻塞赋值 + 正规延迟 | |

| always @(*) begin | |

| #5 C3 = A +B; | |

| end | |

| // 4. 阻塞赋值 + 内定延迟 | |

| always @(*) begin | |

| C4 = #5 A +B; | |

| end | |

| // 5. 非阻塞赋值 + 正规延迟 | |

| always @(*) begin | |

| #5 C5 <= A +B; | |

| end | |

| // 6. 非阻塞赋值 + 内定延迟 | |

| always @(*) begin | |

| C6 <= #5 A +B; | |

| end | |

| endmodule | |

- 总结

根据上述分析,容易看出惯性延时对应于连续赋值中的正规延迟,而传导延时对应于非阻塞赋值中的内定延迟。

所以仿真中常用 “连续赋值 + 正规延迟“ 模拟惯性延迟,用 ”非阻塞赋值 + 内定延迟“ 模拟传导延迟。

<div id="blog_post_info">

<div class="clear"></div>

<div id="post_next_prev"></div>

posted on 2022-08-12 22:27 SOC验证工程师 阅读(211) 评论(0) 编辑 收藏 举报

最后

以上就是个性朋友最近收集整理的关于Verilog中仿真事件中的不同延时方法5 C = A +B的全部内容,更多相关Verilog中仿真事件中的不同延时方法5内容请搜索靠谱客的其他文章。

![Node.js[译] Overview of Blocking vs Non-BlockingOverview of Blocking vs Non-Blocking](https://www.shuijiaxian.com/files_image/reation/bcimg22.png)

发表评论 取消回复