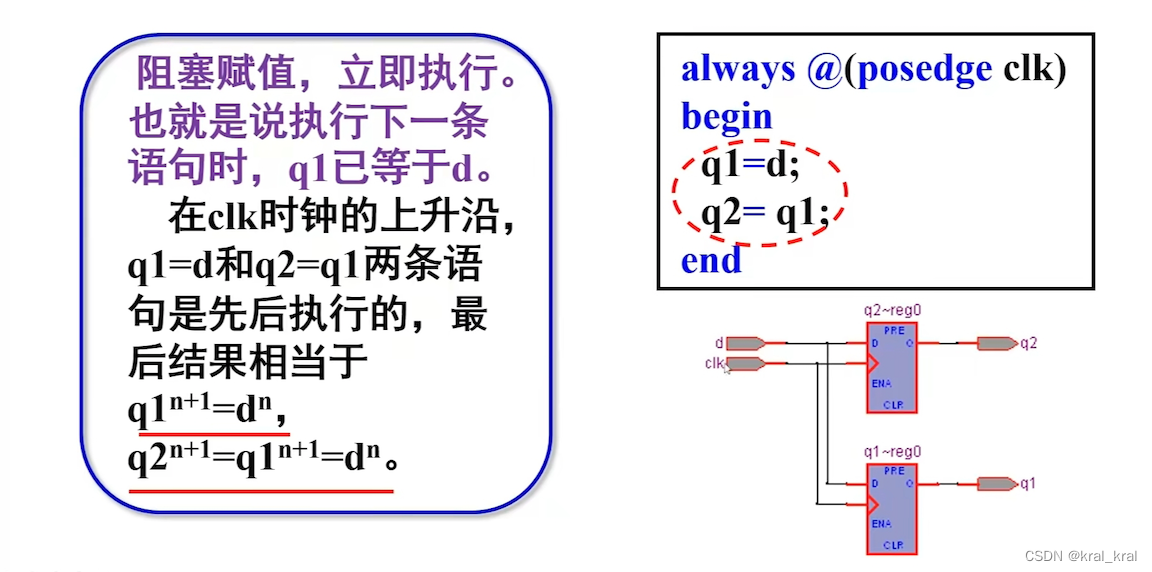

阻塞赋值:

在Verilog HDL的概念中阻塞赋值操作符用等号(即=)表示。在赋值时先计算等号右手部分的值,这时赋值语句不允许任何别的Verilog语句的干扰,直到现行的赋值完成时刻,才允许别的赋值语句的执行。

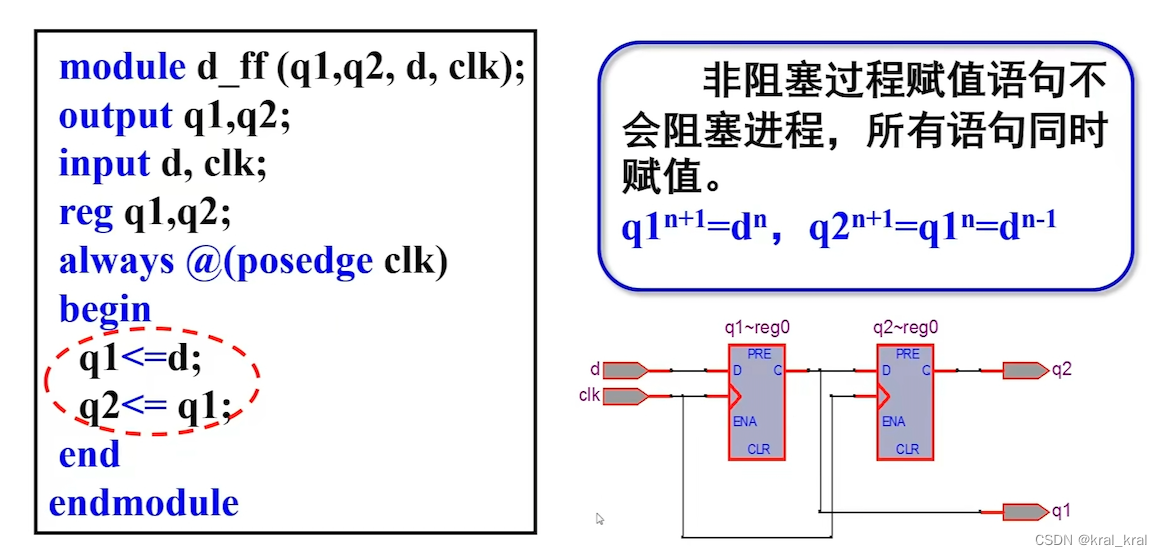

非阻塞赋值:

非阻塞赋值操作符用小于等于号(即<=)表示,由时钟节拍决定,在时钟上升到来时,执行赋值语句右边,然后将begin-end之间的所有赋值语句同时赋值到赋值语句的左边。非阻塞赋值允许其他的Verilog语句同时进行操作。

两者区别:

在状态变量的赋值或开关变量的赋值中,已明确建议大家使用非阻塞赋值。这不但是因为综合工具要求这样做,最根本的原因是与非阻塞赋值语句语意对应的电路结构正是我们想要实现的。这两种赋值语句对应着两种不同的电路结构。阻塞赋值对应的电路结构往往与触发沿没有关系,只与输入电平的变化有关系。而非阻塞赋值对应的电路结构往往与触发沿有关系,只有在触发沿时才有可能发生赋值的情况。

代码演示:

module Assignment_way1a(q1,q2,q3,q4,d,clk);

output q1,q2,q3,q4;

input d,clk;

reg q1,q2,q3,q4;

//Block assignment mode

always@(posedge clk)begin

q1 = d;

q2 = q1;

end

//Non-blocking assignment mode

always@(posedge clk)begin

q3 <= d;

q4 <= q3;

end

endmodule

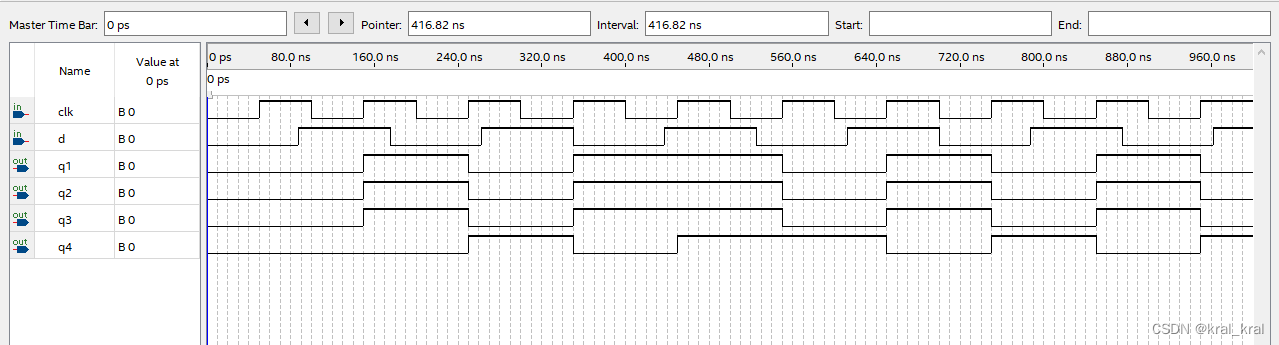

编译运行结果:

此运行结果符合下面阻塞赋值与非阻塞赋值公式演示的结果 。

代码分析:

阻塞赋值实现的功能相当于两个D触发器并联;

非阻塞赋值实现的功能相当于两个D触发器串联;

D触发器:

D触发器是一个具有记忆功能的,具有两个稳定状态的信息存储器件,是构成多种时序电路的最基本逻辑单元,也是数字逻辑电路中一种重要的单元电路。

因此,D触发器在数字系统和计算机中有着广泛的应用。触发器具有两个稳定状态,即"0"和"1",在一定的外界信号作用下,可以从一个稳定状态翻转到另一个稳定状态。

D触发器有集成触发器和门电路组成的触发器。触发方式有电平触发和边沿触发两种,前者在CP(时钟脉冲)=1时即可触发,后者多在CP的前沿(正跳变0→1)触发。

D触发器的次态取决于触发前D端的状态,即次态=D。因此,它具有置0、置1两种功能。

对于边沿D触发器,由于在CP=1期间电路具有维持阻塞作用,所以在CP=1期间,D端的数据状态变化,不会影响触发器的输出状态。

D触发器应用很广,可用做数字信号的寄存,移位寄存,分频和波形发生器等等。

收获与感想:

在程序设计过程中,要根据需求使用阻塞赋值方法或者非阻塞赋值方式。

使用要点:

(1)在描述组合逻辑的always块中用阻塞赋值,则综合成组合逻辑的电路结构:

(2)在描述时序逻辑的always块中用非阻塞赋值,则综合成时序逻辑的电路结构。

Tips

-

欢迎您在评论区留下您的宝贵意见。

最后

以上就是碧蓝香氛最近收集整理的关于Verilog 语言的阻塞赋值与非阻塞赋值阻塞赋值: 非阻塞赋值:两者区别:D触发器:收获与感想: 的全部内容,更多相关Verilog内容请搜索靠谱客的其他文章。

发表评论 取消回复