详细题目:

通知公告_集成电路EDA设计精英挑战赛eda.icisc.cn

命题单位:芯华章科技股份有限公司

“芯华章” 寓意开启芯片产业的华丽篇章,由一支心怀抱负的EDA(电子设计自动化)精英创始团队于2020年3月创立,致力于提供自主研发EDA智能软件和系统的研发、销售和技术服务。

芯华章汇聚了核心技术研发、运营和营销人才,配置完整,核心骨干悉数来自国际领先EDA厂商,从业经验均在20年以上,兼具国际视野和强大的本地市场运营能力,拥有前瞻的技术理念和深厚的技术积累,其技术理念和研发能力受到了国家顶级集成电路学科专家和院士的广泛认可。

芯华章将肩负重任,首先打造决定芯片设计成败的验证软件和系统,从底层架构创新出发,融合AI、云计算等最新技术,研发出自主研发、安全可靠的验证软件和系统,突破现今验证技术在验证效率、工具扩展性、设计可适配性、低功耗、功能安全等多项挑战。全面支持中国集成电路、5G、人工智能、云服务和超级计算等多领域高科技发展,加速创新,为合作伙伴提供自主研发、安全可靠的解决方案与服务。

赛题背景

这道赛题是让学生了解一下EDA验证软件,尤其是Verilog仿真软件的理念和挑战。

芯片设计一般都是用Verilog写的,Verilog是一种硬件描述语言 (HDL)。设计者用Verilog写好design后,需要用EDA工具进行仿真,检验其功能是否正确。

Verilog的仿真软件一般是个编译器,它的输入是Verilog 语言,输出是可执行代码。因此,它和一般的编译器有一定的类似之处,也是由parser, elaboration, code generation 等模块构成。

然而,Verilog毕竟不是普通的编程语言,它描述的是硬件。这就意味着,一个Verilog的仿真器,必然要把Verilog背后表示的硬件逻辑解析清楚,而不是简单的停留在Verilog字面上。

这道赛题就是让学生了解到,Verilog的仿真器需要处理哪些HDL独有的信息,以及由此带来的在实现上挑战。

赛题描述

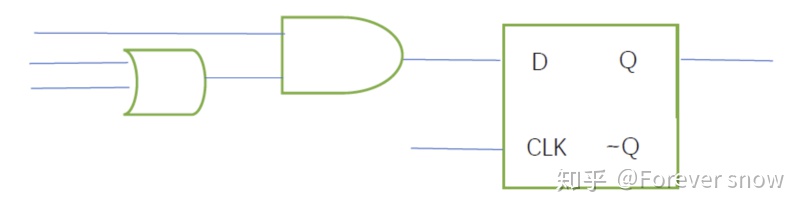

在RTL的设计中,有一部分是组合逻辑(combinational logic),一部分是时序逻辑(sequential logic)。一般而言,一个寄存器类型的变量只能有一个驱动(driver),该驱动可以是组合/时序逻辑的输出。如:

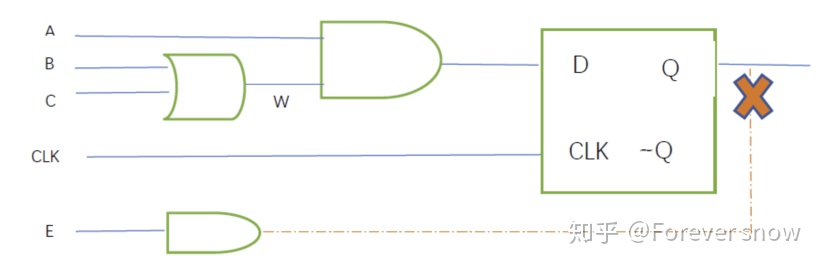

在实际RTL开发中,有一类比较常见的错误,就是一个时序电路的输出(如Q)会有多个驱动,如:

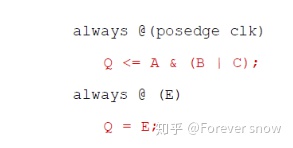

其对应的RTL Verilog 为:

通常,这种错误往往在仿真结果出现问题的时候才能发现,用户调试起来周期非常长,尤其是RTL设计非常大的时候。理想的情况是验证工具进行静态检查(static check),让这类问题在编译阶段(compile time)报出,从而节省用户的调试时间。本赛题就是要求参赛者开发这样一种静态检查的功能。

完整描述请参考官方链接:

http://eda.icisc.cn/download/index?type=2

技术要点1

本赛题用到例子是一个RTL design. 通常,RTL design由组合逻辑和时序逻辑构成。一个数字电路的网表抽象出来后就是一个图,每个变量是一个节点,变量之间的连线就是边。每个节点会有驱动(driver),和负载(load). 要想实现本赛题的驱动检查,首先需要从表面的Verilog语言建立出一个这样的图,方便查询每个节点的驱动。

以赛题中的RTL design为例, 我们需要为该设计中的节点(Q , E, A, B, C CLK)建立起一个driver->load 关系图。如,A 的 load是一个与门, B,C的load是一个或门, E 的load是一个 buffer。同样,D 的driver 是与门, 或门的driver是 B, C, 等。 有了这个driver-load关系图,就比较清楚那个节点的driver数目是大于1 的。

技术要点 2

RTL design的抽象程度要高于门级(gate level),这意味着,会有vector, memory这样的word-level 的数据类型,以及 for loop 这样的控制类型语句。 而驱动信息是作用在每个bit 上的,如何从word-level的表示,高效的拿到bit-level的驱动信息,是这道赛题里要解决的问题。这里面我们没有标准答案,留给参赛选手自己发挥。

今年,大赛增设最高奖项“麒麟杯”20万元。如此高额的奖金,在国内集成电路相关的所有学科竞赛中,相信是绝无仅有的。EDA是目前中国集成电路被卡脖子最为严重的领域,奖金非常有诚意。

欢迎广大集成电路、微电子、计算机、软件、数学领域的同学来角逐,展现自己的聪明才智和技术实力。即使拿不到20万元的奖金,还有8万元、2万元等等奖项。

大赛官网:

集成电路EDA设计精英挑战赛eda.icisc.cn

更多问题可加入大赛官方QQ群:792345737

最后

以上就是传统秋天最近收集整理的关于verilog找不到模块_【赛题解析】赛题四--芯华章:时序模块驱动冲突的检查的全部内容,更多相关verilog找不到模块_【赛题解析】赛题四--芯华章:时序模块驱动冲突内容请搜索靠谱客的其他文章。

发表评论 取消回复