关于如何新建项目,请移步:【Modelsim零基础入门】新建项目+运行第一个verilog仿真程序:一位加法器

↓ 第一个自己写的verilog程序以及对应的测试程序

计算A+B

源程序

文件名称:simpleAdd.v

如果复制粘贴后报错,请删除注释以及所有可能的特殊字符

module addTwo(sum,a,b);

input a,b;

output sum;

assign sum=a+b;

endmodule

测试程序

文件名称:test.v

`timescale 1ns/1ns

`include "simpleAdd.v"

module addTwo_tb;

reg a,b;

wire sum;

addTwo myAddTwo(sum,a,b);

initial

begin a=0;b=0; //不能给sum赋值sum=0;

#5 a<=1;

#5 b<=1; //因为begin-end是串行,实际上是第5+5ns开始对b赋值

end

initial

begin

$monitor($time,,"%d + %d = %d",a,b,sum);

#20

$finish;

end

endmodule

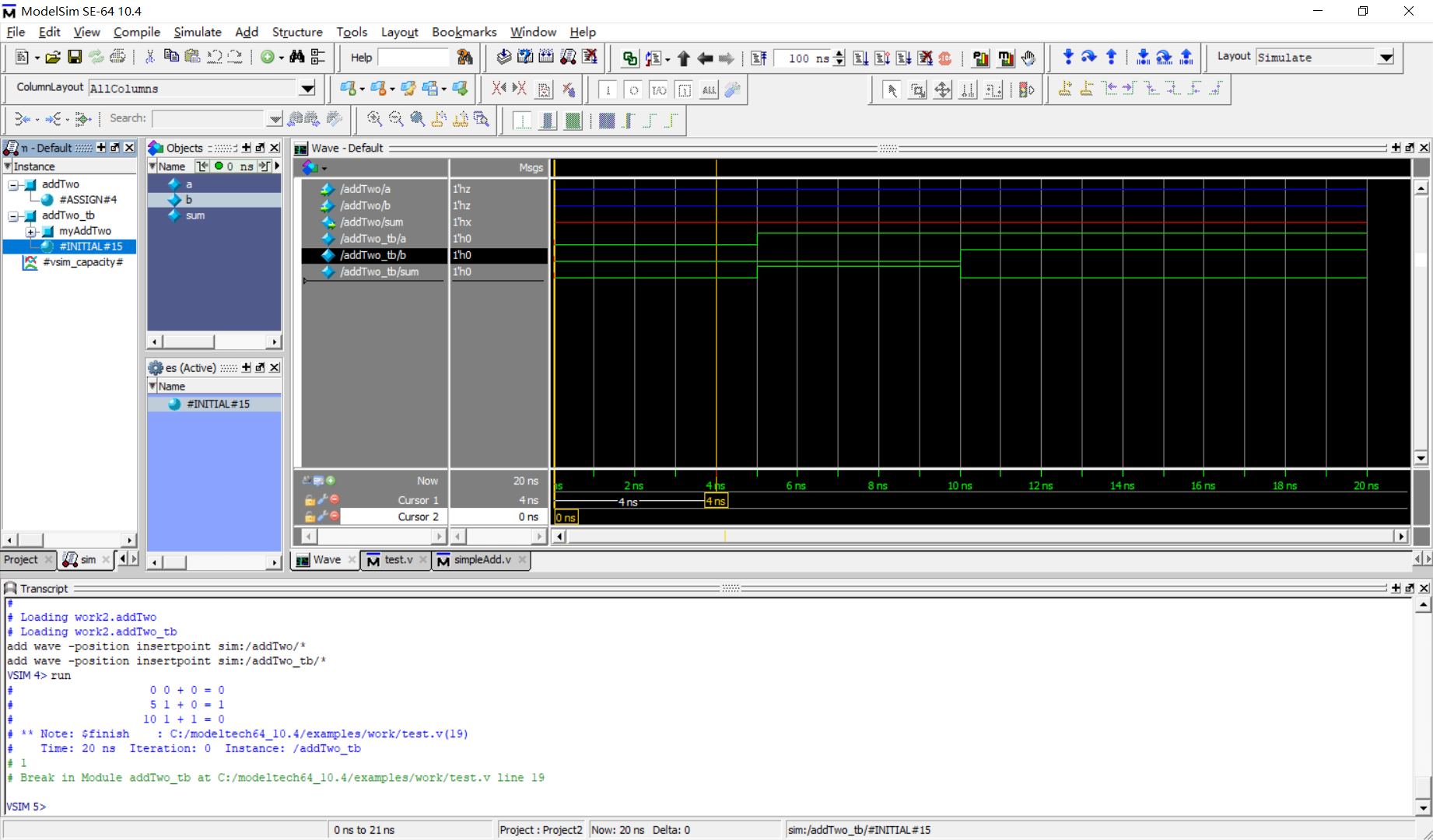

运行结果

从wave图中可以看到,从#5ns开始a=1,从#10ns开始b=1

sum总是随着a,b的变化而变化

下面的控制台也输出了每一次变化的过程记录

最后

以上就是烂漫翅膀最近收集整理的关于【Modelsim零基础入门】verilog仿真程序:1-bit A+B的全部内容,更多相关【Modelsim零基础入门】verilog仿真程序:1-bit内容请搜索靠谱客的其他文章。

本图文内容来源于网友提供,作为学习参考使用,或来自网络收集整理,版权属于原作者所有。

发表评论 取消回复